好久不测试占空比,快忘了,幸亏同事提醒,用15分钟的时间维度测试完占空比

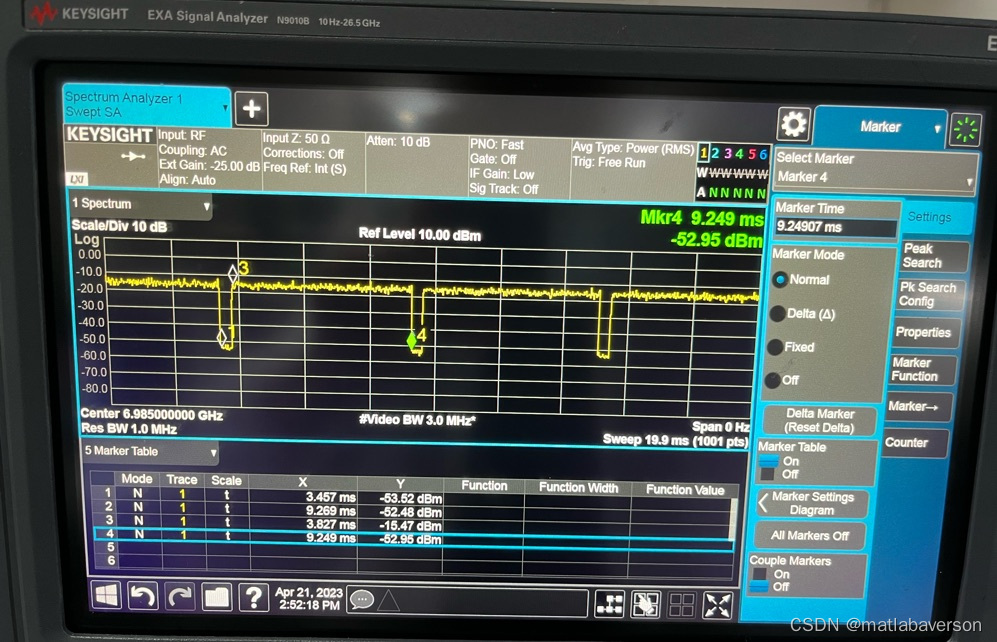

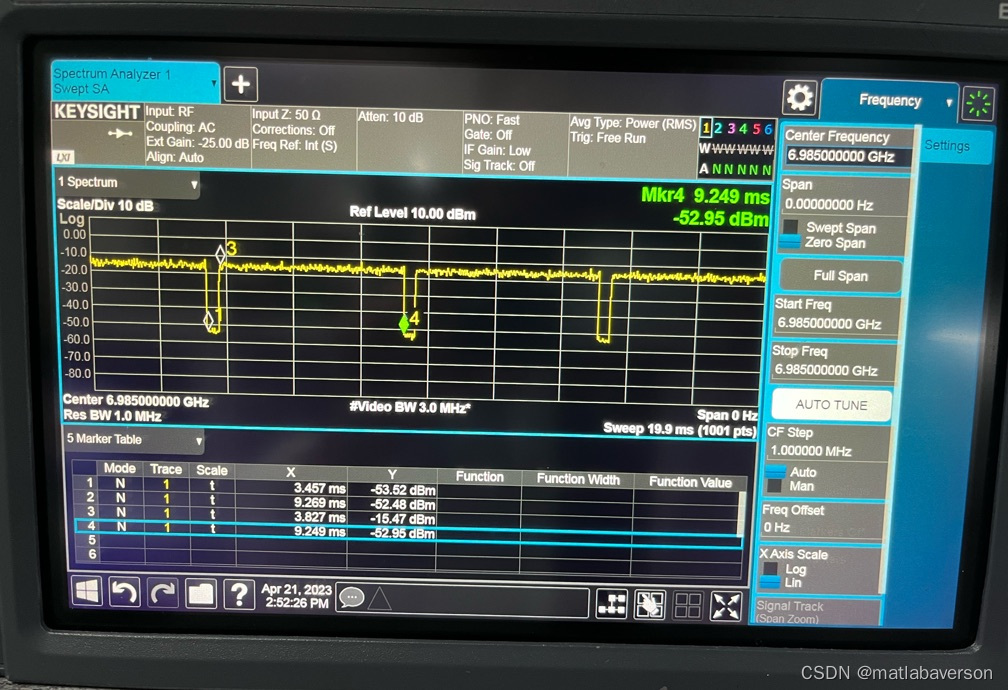

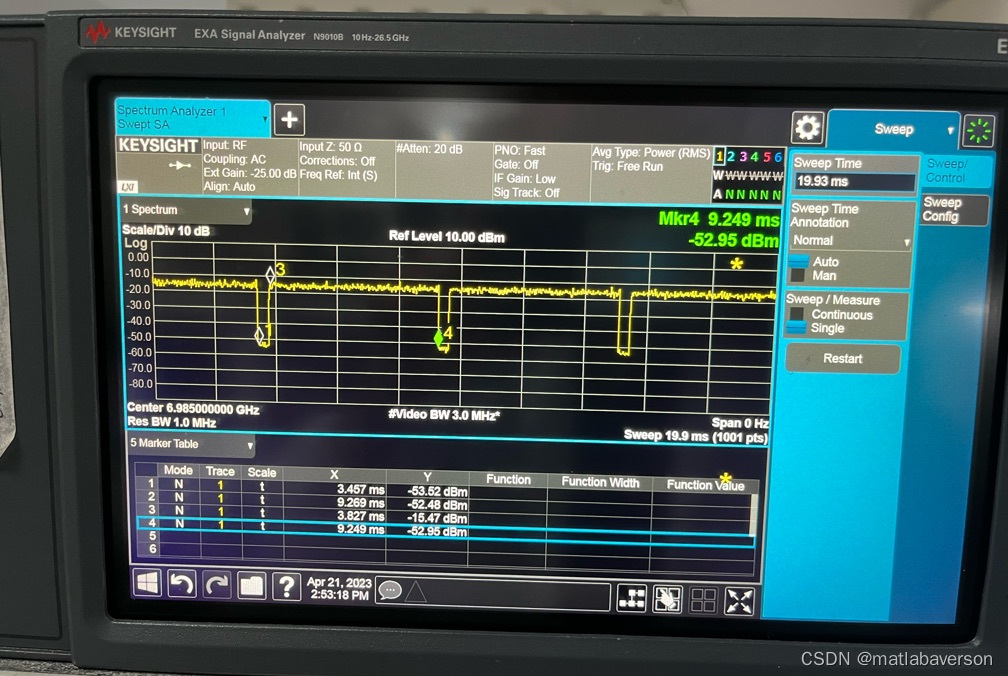

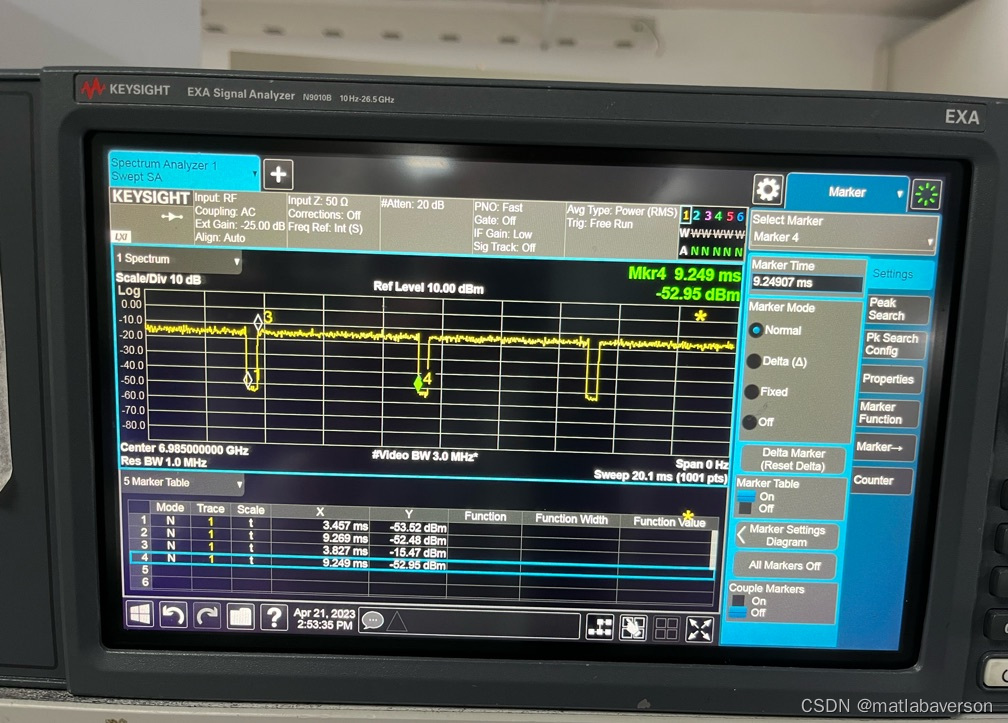

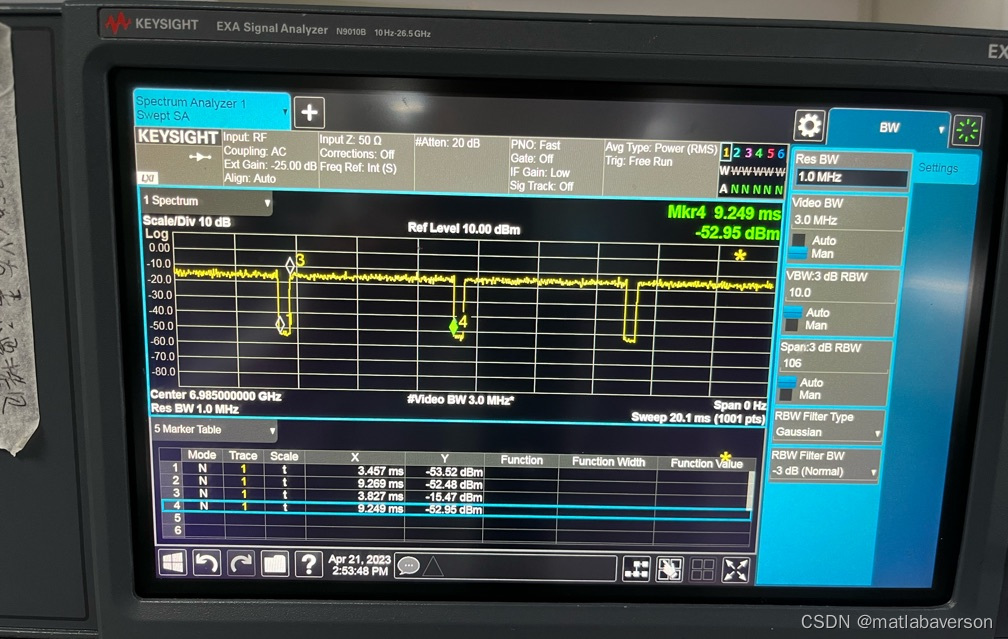

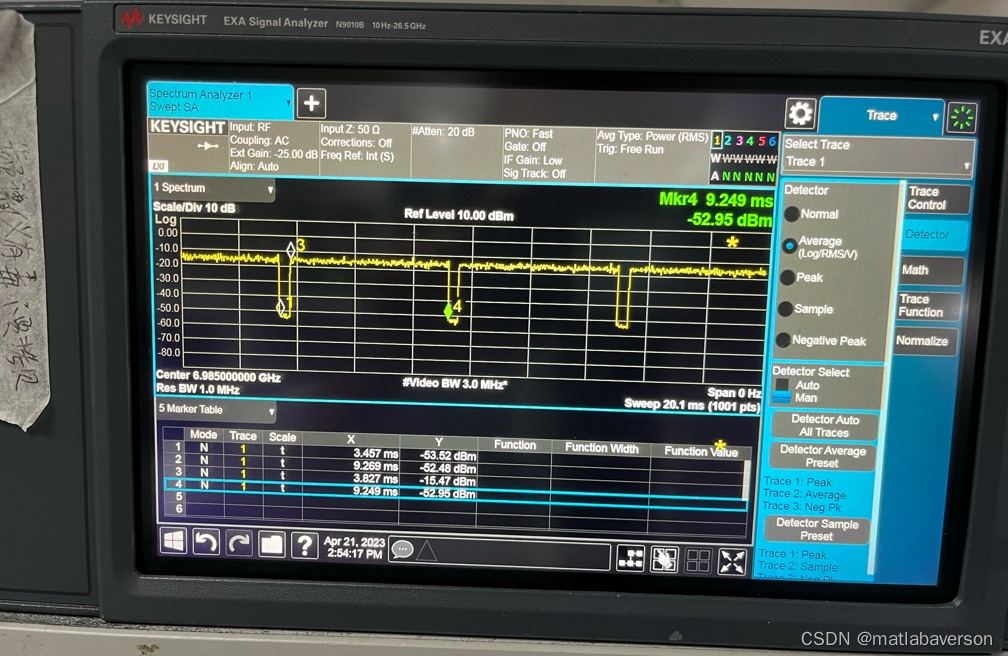

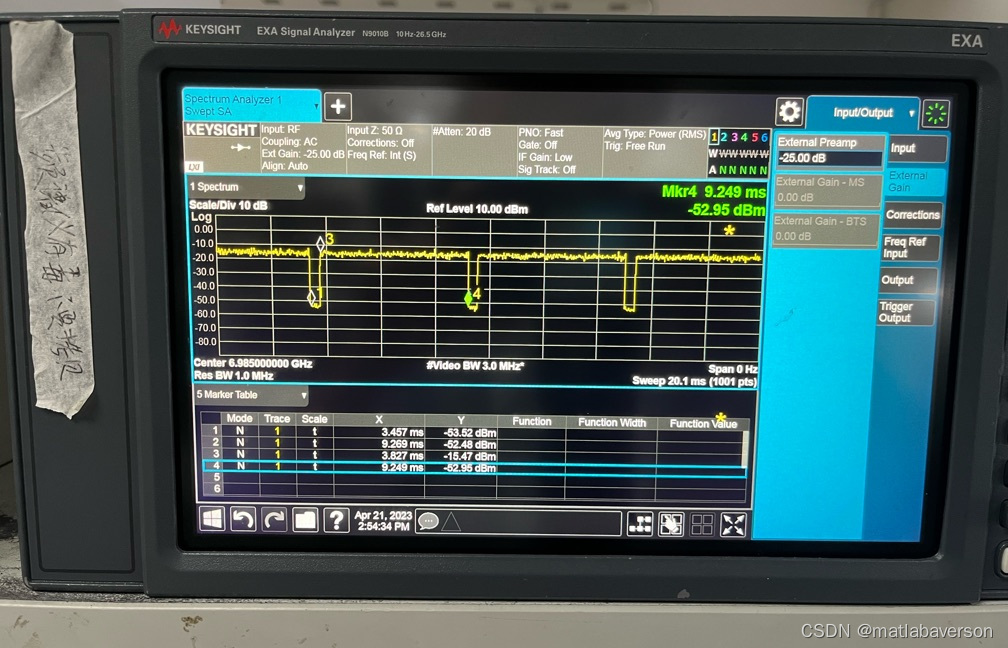

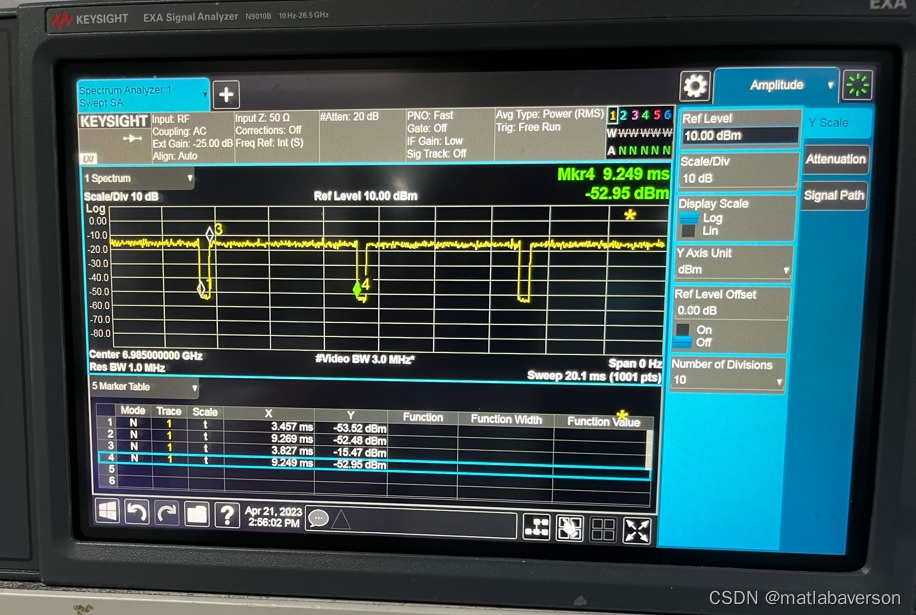

1.频谱仪设置

Center Frequency

SPAN 0

RBW 8M

VBM 8M

Sweep Time 10ms ≤Sweep point*工(工为当前模式传输周期)

Sweep Mode single

Sweep point 10000

Sweep time Trace RMS 或 Sample(设备没有 RMS 检测器时)

设置方式见下图

2.读取当前频谱仪波形中的 Ton和Tof时间,计算占空比x(TON/(TON+TOFF))。

3.取10log(1/x),如图计算出来是0.3,加到功率计对应的功率上面

1552

1552

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?