原创地址:http://lidunyang2008.blog.163.com/blog/static/190676205201210551750805/

什么是ECC校验

定义

ECC校验是一种内存纠错原理,它是现在比较先进的内存错误检查和更正的手段。ECC内存即纠错内存,简单的说,其具有发现错误,纠正错误的功能,一般多应用在高档台式电脑/服务器及图形工作站上,这将使整个电脑系统在工作时更趋于安全稳定。技术原理

内存是一种电子器件,在其工作过程中难免会出现错误,而对于稳定性要求高的用户来说,内存错误可能会引起致命性的问题。内存错误根据其原因还可分为 硬错误 和软错误。硬件错误是由于硬件的损害或缺陷造成的,因此数据总是不正确,此类错误是无法纠正的;软错误是随机出现的,例如在内存附近突然出现电子干扰等因素都可能造成内存软错误的发生。 为了能检测和纠正内存软错误,在ECC技术出现之前,首先出现的是内存“ 奇偶校验 (Parity)”。内存中最小的单位是比特,也称为“位(bit)”,位有只有两种状态分别以1和0来标示,每8个连续的比特叫做一个字节(byte)。不带奇偶校验的内存每个字节只有8位,如果其某一位存储了错误的值,就会导致其存储的相应数据发生变化,进而导致应用程序发生错误。而奇偶校验就是在每一字节(8位)之外又增加了一位作为错误检测位。在某字节中存储数据之后,在其8个位上存储的数据是固定的,因为位只能有两种状态1或0,假设存储的数据用位标示为1、1、1、0、0、1、0、1,那么把每个位相加(1+1+1+0+0+1+0+1=5),结果是奇数。对于 偶校验,校验位就定义为1( 保证逻辑高的位数是偶数个), 反之则为0;对于奇校验, 校验位为0,这样就有奇数个逻辑高位 。当CPU读取存储的数据时,它会再次把前8位中存储的数据相加,计算结果是否与校验位相一致。从而一定程度上能检测出内存错误,奇偶校验只能检测出错误而无法对其进行修正,同时虽然双位同时发生错误的概率相当低,奇偶校验却无法检测出双位错误。示例

ECC(Error Checking and Correcting,错误检查和纠正)内存,它同样也是在 数据位 上额外的位存储一个用数据加密的代码。当数据被写入内存,相应的ECC代码与此同时也被保存下来。当重新读回刚才存储的数据时,保存下来的ECC代码就会和读数据时产生的ECC代码做比较。如果两个代码不相同,他们则会被解码,以确定数据中的那一位是不正确的。然后这一错误位会被抛弃, 内存控制器 则会释放出正确的数据。被纠正的数据很少会被放回内存。假如相同的错误数据再次被读出,则纠正过程再次被执行。重写数据会增加处理过程的开销,这样则会导致系统性能的明显降低。如果是随机事件而非内存的缺点产生的错误,则这一 内存地址 的错误数据会被再次写入的其他数据所取代。 如果数据位是8位,则需要增加5位来进行ECC错误检查和纠正,数据位每增加一倍,ECC只增加一位检验位,也就是说当数据位为16位时ECC位为6位,32位时ECC位为7位,数据位为64位时ECC位为8位,依此类推,数据位每增加一倍,ECC位只增加一位。总之,在内存中ECC能够容许错误,并可以将错误更正,使系统得以持续正常的操作,不致因错误而中断,且ECC具有自动更正的能力,可以将Parity无法检查出来的错误位查出并将错误修正。其它相关资料

ECC内存误区

目前是一谈到 服务器内存 ,大家都一致强调要买ECC内存,认为ECC内存速度快,其实是一种错误地认识,ECC内存成功之处并不是因为它速度快(速度方面根本不关它事只与 内存类型 有关),而是因为它有特殊的纠错能力,使服务器保持稳定。ECC本身并不是一种内存型号,也不是一种内存专用技术,它是一种广泛应用于各种领域的 计算机指令 中,是一种 指令纠错技术 。它的英文全称是“Error Checking and Correcting”,对应的中文名称就叫做“错误检查和纠正”,从这个名称我们就可以看出它的主要功能就是“发现并纠正错误”,它比奇偶校正技术更先进的方面主要在于它不仅能发现错误,而且能纠正这些错误,这些错误纠正之后计算机才能正确执行下面的任务,确保服务器的正常运行。之所以说它并不是一种内存型号,那是因为并不是一种影响内存结构和存储速度的技术,它可以应用到不同的内存类型之中,就象我们在前面讲到的“奇偶校正”内存,它也不是一种内存,最开始应用这种技术的是EDO内存,现在的SD也有应用,而ECC内存主要是从SD内存开始得到广泛应用,而新的DDR、RDRAM也有相应的应用,目前主流的ECC内存其实是一种SD内存。参考文档: http://blogimg.chinaunix.net/blog/upfile2/080702112233.pdf

NAND FLASH ECC校验原理与实现

ECC简介

由于NAND Flash的工艺不能保证NAND的Memory Array在其生命周期中保持性能的可靠,因此,在NAND的生产中及使用过程中会产生坏块。为了检测数据的可靠性,在应用NAND Flash的系统中一般都会采用一定的坏区管理策略,而管理坏区的前提是能比较可靠的进行坏区检测。

如果操作时序和电路稳定性不存在问题的话,NAND Flash出错的时候一般不会造成整个Block或是Page不能读取或是全部出错,而是整个Page(例如512Bytes)中只有一个或几个bit出错。

对数据的校验常用的有奇偶校验、CRC校验等,而在NAND Flash处理中,一般使用一种比较专用的校验——ECC。ECC能纠正单比特错误和检测双比特错误,而且计算速度很快,但对1比特以上的错误无法纠正,对2比特以上的错误不保证能检测。

ECC原理

ECC一般每256字节原始数据生成3字节ECC校验数据,这三字节共24比特分成两部分:6比特的列校验和16比特的行校验,多余的两个比特置1,如下图所示:

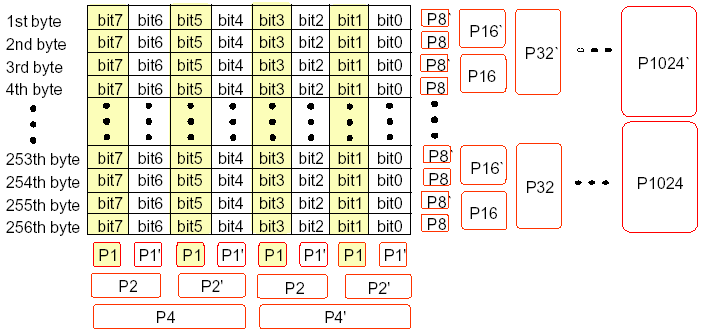

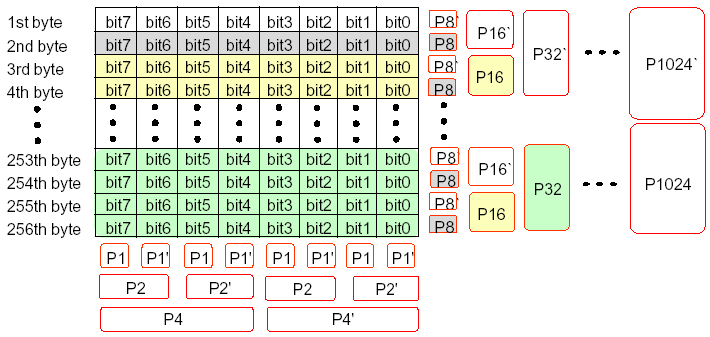

ECC的列校验和生成规则如下图所示(Parity Generation ( In case of 256 byte input )):

用数学表达式表示为:

P1=bit7(+)bit5(+)bit3(+)bit1(+)P1

P2=bit7(+)bit6(+)bit3(+)bit2(+)P2

P4=bit7(+)bit6(+)bit5(+)bit4(+)P4

这里(+)表示“位异或”操作ECC的行校验和生成规则如下图所示(Parity Generation ( In case of 256 byte input )):

用数学表达式表示为:

P8 = bit7(+)bit6(+)bit5(+)bit4(+)bit3(+)bit2(+)bit1(+)bit0(+)P8

这里(+)同样表示“位异或”操作

当往NAND Flash的page中写入数据的时候,每256字节我们生成一个ECC校验和,称之为原ECC校验和,保存到PAGE的OOB(out-of-band)数据区中。

当从NAND Flash中读取数据的时候,每256字节我们生成一个ECC校验和,称之为新ECC校验和。

校验的时候,根据上述ECC生成原理不难推断:将从OOB区中读出的原ECC校验和新ECC校验和按位异或,若结果为0,则表示不存在错(或是出现了ECC无法检测的错误);若3个字节异或结果中存在11个比特位为1,表示存在一个比特错误,且可纠正;若3个字节异或结果中只存在1个比特位为1,表示OOB区出错;其他情况均表示出现了无法纠正的错误。

- The result of XOR : all ECC code is `0`

* Correctable Error

- The result of XOR : total 11bits are `1`

- When main area has 1 bit error, each parity pair (ex. P8 & P8`) has 1 & 0 or 0 & 1

*ECC Error

- The result of XOR : only 1bit is `1`

- When ECC area has an error, call it ECC error

* Uncorrectable Error

- The result of XOR : random data

- When the flash memory has more than 2 bits error, data couldn’t be corrected

ECC算法的实现

static const u_char nand_ecc_precalc_table[] =

{

0x00, 0x55, 0x56, 0x03, 0x59, 0x0c, 0x0f, 0x5a, 0x5a, 0x0f, 0x0c, 0x59, 0x03, 0x56, 0x55, 0x00,

0x65, 0x30, 0x33, 0x66, 0x3c, 0x69, 0x6a, 0x3f, 0x3f, 0x6a, 0x69, 0x3c, 0x66, 0x33, 0x30, 0x65,

0x66, 0x33, 0x30, 0x65, 0x3f, 0x6a, 0x69, 0x3c, 0x3c, 0x69, 0x6a, 0x3f, 0x65, 0x30, 0x33, 0x66,

0x03, 0x56, 0x55, 0x00, 0x5a, 0x0f, 0x0c, 0x59, 0x59, 0x0c, 0x0f, 0x5a, 0x00, 0x55, 0x56, 0x03,

0x69, 0x3c, 0x3f, 0x6a, 0x30, 0x65, 0x66, 0x33, 0x33, 0x66, 0x65, 0x30, 0x6a, 0x3f, 0x3c, 0x69,

0x0c, 0x59, 0x5a, 0x0f, 0x55, 0x00, 0x03, 0x56, 0x56, 0x03, 0x00, 0x55, 0x0f, 0x5a, 0x59, 0x0c,

0x0f, 0x5a, 0x59, 0x0c, 0x56, 0x03, 0x00, 0x55, 0x55, 0x00, 0x03, 0x56, 0x0c, 0x59, 0x5a, 0x0f,

0x6a, 0x3f, 0x3c, 0x69, 0x33, 0x66, 0x65, 0x30, 0x30, 0x65, 0x66, 0x33, 0x69, 0x3c, 0x3f, 0x6a,

0x6a, 0x3f, 0x3c, 0x69, 0x33, 0x66, 0x65, 0x30, 0x30, 0x65, 0x66, 0x33, 0x69, 0x3c, 0x3f, 0x6a,

0x0f, 0x5a, 0x59, 0x0c, 0x56, 0x03, 0x00, 0x55, 0x55, 0x00, 0x03, 0x56, 0x0c, 0x59, 0x5a, 0x0f,

0x0c, 0x59, 0x5a, 0x0f, 0x55, 0x00, 0x03, 0x56, 0x56, 0x03, 0x00, 0x55, 0x0f, 0x5a, 0x59, 0x0c,

0x69, 0x3c, 0x3f, 0x6a, 0x30, 0x65, 0x66, 0x33, 0x33, 0x66, 0x65, 0x30, 0x6a, 0x3f, 0x3c, 0x69,

0x03, 0x56, 0x55, 0x00, 0x5a, 0x0f, 0x0c, 0x59, 0x59, 0x0c, 0x0f, 0x5a, 0x00, 0x55, 0x56, 0x03,

0x66, 0x33, 0x30, 0x65, 0x3f, 0x6a, 0x69, 0x3c, 0x3c, 0x69, 0x6a, 0x3f, 0x65, 0x30, 0x33, 0x66,

0x65, 0x30, 0x33, 0x66, 0x3c, 0x69, 0x6a, 0x3f, 0x3f, 0x6a, 0x69, 0x3c, 0x66, 0x33, 0x30, 0x65,

0x00, 0x55, 0x56, 0x03, 0x59, 0x0c, 0x0f, 0x5a, 0x5a, 0x0f, 0x0c, 0x59, 0x03, 0x56, 0x55, 0x00

};

// Creates non-inverted ECC code from line parity

static void nand_trans_result(u_char reg2, u_char reg3,u_char *ecc_code)

{

u_char a, b, i, tmp1, tmp2;

/* Initialize variables */

a = b = 0x80;

tmp1 = tmp2 = 0;

/* Calculate first ECC byte */

for (i = 0; i < 4; i++)

{

if (reg3 & a) /* LP15,13,11,9 --> ecc_code[0] */

tmp1 |= b;

b >>= 1;

if (reg2 & a) /* LP14,12,10,8 --> ecc_code[0] */

tmp1 |= b;

b >>= 1;

a >>= 1;

}

/* Calculate second ECC byte */

b = 0x80;

for (i = 0; i < 4; i++)

{

if (reg3 & a) /* LP7,5,3,1 --> ecc_code[1] */

tmp2 |= b;

b >>= 1;

if (reg2 & a) /* LP6,4,2,0 --> ecc_code[1] */

tmp2 |= b;

b >>= 1;

a >>= 1;

}

/* Store two of the ECC bytes */

ecc_code[0] = tmp1;

ecc_code[1] = tmp2;

}

// Calculate 3 byte ECC code for 256 byte block

void nand_calculate_ecc (const u_char *dat, u_char *ecc_code)

{

u_char idx, reg1, reg2, reg3;

int j;

/* Initialize variables */

reg1 = reg2 = reg3 = 0;

ecc_code[0] = ecc_code[1] = ecc_code[2] = 0;

/* Build up column parity */

for(j = 0; j < 256; j++)

{

/* Get CP0 - CP5 from table */

idx = nand_ecc_precalc_table[dat[j]];

reg1 ^= (idx & 0x3f);

/* All bit XOR = 1 ? */

if (idx & 0x40) {

reg3 ^= (u_char) j;

reg2 ^= ~((u_char) j);

}

}

/* Create non-inverted ECC code from line parity */

nand_trans_result(reg2, reg3, ecc_code);

/* Calculate final ECC code */

ecc_code[0] = ~ecc_code[0];

ecc_code[1] = ~ecc_code[1];

ecc_code[2] = ((~reg1) << 2) | 0x03;

}

// Detect and correct a 1 bit error for 256 byte block

int nand_correct_data (u_char *dat, u_char *read_ecc, u_char *calc_ecc)

{

u_char a, b, c, d1, d2, d3, add, bit, i;

/* Do error detection */

d1 = calc_ecc[0] ^ read_ecc[0];

d2 = calc_ecc[1] ^ read_ecc[1];

d3 = calc_ecc[2] ^ read_ecc[2];

if ((d1 | d2 | d3) == 0)

{

/* No errors */

return 0;

}

else

{

a = (d1 ^ (d1 >> 1)) & 0x55;

b = (d2 ^ (d2 >> 1)) & 0x55;

c = (d3 ^ (d3 >> 1)) & 0x54;

/* Found and will correct single bit error in the data */

if ((a == 0x55) && (b == 0x55) && (c == 0x54))

{

c = 0x80;

add = 0;

a = 0x80;

for (i=0; i<4; i++)

{

if (d1 & c)

add |= a;

c >>= 2;

a >>= 1;

}

c = 0x80;

for (i=0; i<4; i++)

{

if (d2 & c)

add |= a;

c >>= 2;

a >>= 1;

}

bit = 0;

b = 0x04;

c = 0x80;

for (i=0; i<3; i++)

{

if (d3 & c)

bit |= b;

c >>= 2;

b >>= 1;

}

b = 0x01;

a = dat[add];

a ^= (b << bit);

dat[add] = a;

return 1;

}

else

{

i = 0;

while (d1)

{

if (d1 & 0x01)

++i;

d1 >>= 1;

}

while (d2)

{

if (d2 & 0x01)

++i;

d2 >>= 1;

}

while (d3)

{

if (d3 & 0x01)

++i;

d3 >>= 1;

}

if (i == 1)

{

/* ECC Code Error Correction */

read_ecc[0] = calc_ecc[0];

read_ecc[1] = calc_ecc[1];

read_ecc[2] = calc_ecc[2];

return 2;

}

else

{

/* Uncorrectable Error */

return -1;

}

}

}

/* Should never happen */

return -1;

}

5691

5691

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?