串行12C总线具有双引脚接口。串行数据和地址(SDA)数据3脚用于I/O功能,串行时钟线(SCL)时钟引脚控制和引用I2C总线。I2C接口允许PXA27x处理器作为I2C总线上的主从设备。

I2C接口使PXA27x处理器能够与I2C外围设备和微控制器进行系统管理功能的通信。I2C总线需要最少的硬件中继状态、可靠性和设备之间的控制信息,I2C接口作为外围设备驻留在处理器内部总线上。缓冲接口提供对通过I2C总线发送和接收的数据的访问。一组内存增强寄存器、中继控制和状态信息。

注意: I2C接口不支持硬件通用调用、10位寻址、高速模式(HS-模式,3.4Mbit/s)或CBUS兼容性。

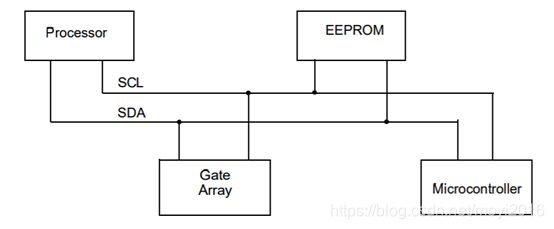

例如,处理器I2C接口可以在总线上充当主机,将EEPROM作为接收数据的从站(参下图)。当12C接口寻址EEPROM时,它充当主发射机,EEPROM作为从接收器。当I2C接口读取数据时,它充当主接收器,EEPROM作为从发送器。无论是作为发射机还是接收器,主服务器都生成时钟,启动事务并终止事务。

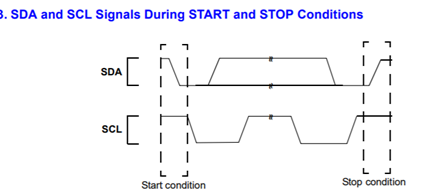

I2C总线使用开路的有线和结构,它允许多个设备驱动TheBus线路,并就仲裁、等待状态和错误条件等事件进行状态通信。当主服务器在数据传输期间驱动时钟(SCL)行时,它会在时钟较高的每个实例上传输一点。当从站无法接受或驱动由主程序分配的数据时,从站可以在高状态之间保持较低的SCL,以插入等待间隔。主时钟只能在仲裁期间由另一个主站改变,或者由保持时钟线低的慢从属器来改变。

I2C总线允许多个主机,这意味着多个设备可以同时启动数据传输。总线仲裁解决了主程序之间的冲突。如果两位主人驾驶着相同的数据,他们就会同时在公共汽车上做烛光。如果主程序试图将SDA推高,而另一位主程序将SDA降低,则主程序将输掉仲裁。SCL线是由主程序使用有线和连接到SCL线生成的时钟的同步组合。

I2C事务由I2C接口作为主程序发起,或者由I2C接口作为从级接收。这两种情况都可能导致读、写或在I2C总线上同时进行。

操作块

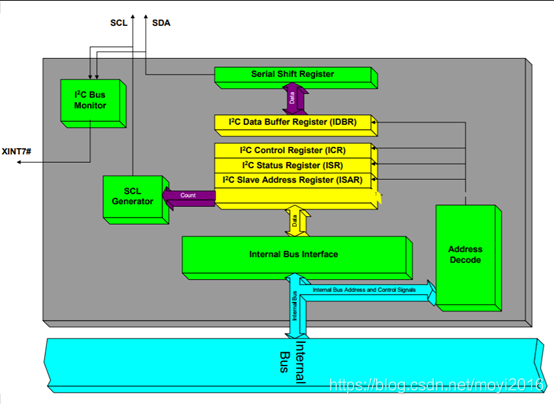

I2C单元驻留在处理器外围总线上。处理器中断机制可用于通知CPU在I2C总线上存在活动。可以使用轮询代替中断。I2C接口包括到I2C总线的双线接口、用于往返PXA27x处理器的数据的八位缓冲区、一组控制和状态寄存器以及用于并行/串行转换的移位寄存器(见下图)。I2C总线接口单元图

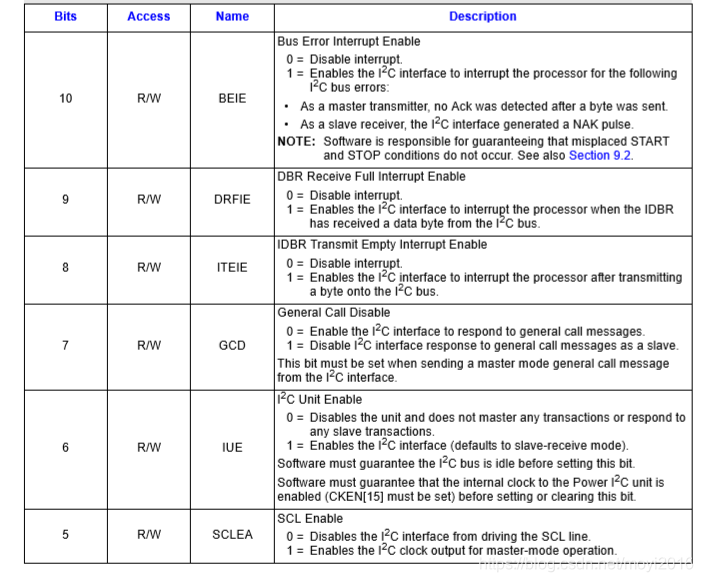

在以下情况,I2C接口启动对PXA27x处理器的中断:

(1) 缓冲器满了

(2) 缓冲区为空

(3) 检测到I2C接口从地址

(4) 仲裁失败

(5) 出现总线错误情况

当PXA27x处理器在I2C总线上启动读或写时,它会将接口从默认的从接收模式切换到主传输模式。如果事务是写的,则在地址传输完成后,I2C接口仍然处于主传输模式。如果事务是读的,则I2C接口发送从地址,然后切换到主接收模式。

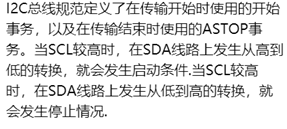

I2C启动和停止

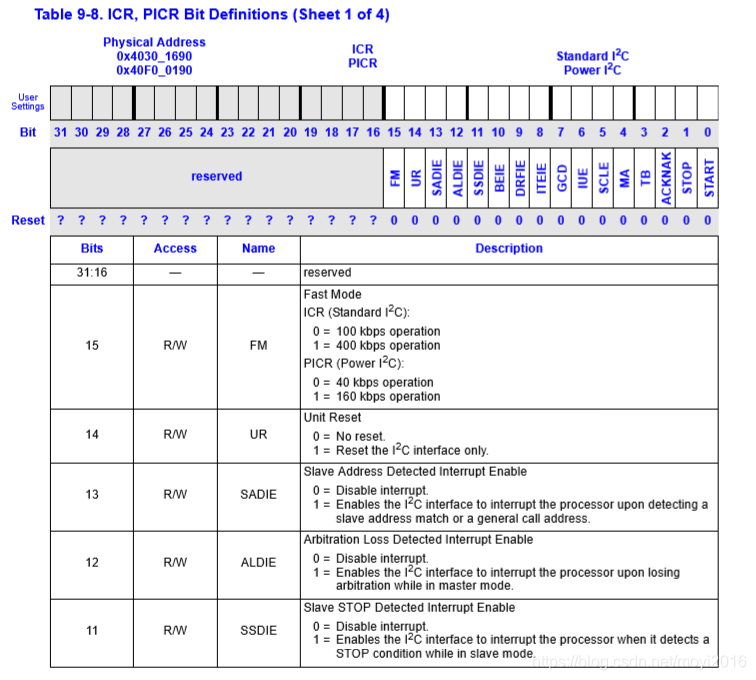

I2C单元使用ICR[START]和ICR[STOP]位来:启动额外的字节传输,在I2C总线上启动一个启动条件,启动数据连接(重复启动),在I2C总线上启动停止条件

Start

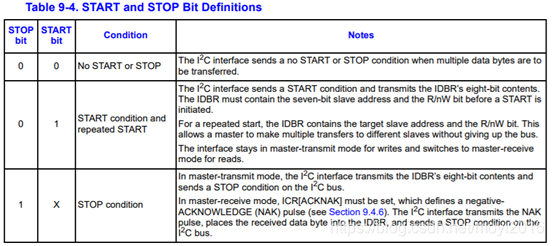

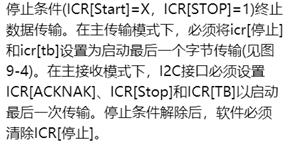

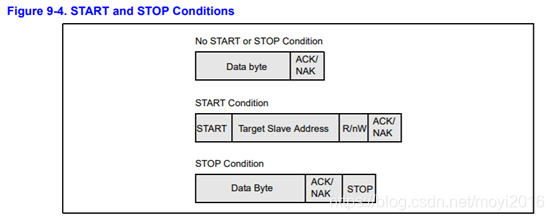

启动条件(icr[start]=1, icr[stop]=0)启动主事务或重复启动。在设置ICR[Start]之前,软件必须在IDBR中加载目标从地址和R/nW位(参见9.5.4节)。在设置ICR[TB]后, 在I2C总线上传输起始和IDBR内容。对于写入请求,I2C总线停留在主传输模式,对于读取请求则进入主接收模式。对于重复启动、读或写的更改或目标从地址的变化,IDBR包含更新的目标从地址和ther/nw位。重复的启动使主人能够在不放弃总线的情况下多次转移到不同的奴隶

No START or STOP Condition

在主传输模式中使无开始或停止条件 (icr[start]=0, icr[stop]=0), 而I2C接口正在传输多个数据字节(见图9-4)。软件写数据字节,I2C接口设置ISR[ITE]并清除ICR[TB]。然后,软件将一个新字节写入IDBR并设置ICR[TB],以启动新的字节传输。这个过程一直持续到软件设置ICR[开始]或ICR[停止]为止。ICR[Start]和ICR[Stop]在发送开始、停止或重复START后,I2C接口不会自动清除。

在每个字节传输之后,包括ICR[ACKNAK]控制位定义的确认脉冲之后,I2C接口将SCL线保持在较低的位置,以插入等待状态,直到设置了ICR[TB]。此操作通知I2C接口释放SCI行, 并允许下一次信息传输继续进行。

STOP condition

9.4.4数据传输序列

I2C单元以1字节增量传输数据,并始终遵循以下顺序:

1、 START启动

2、 7位从地址

3、 R/nW位

4、 确认脉冲

5、 8位数据

6、 确认脉冲

7、 对所需字节数重复步骤5和步骤6

8、 重复启动(重复步骤1)或停止

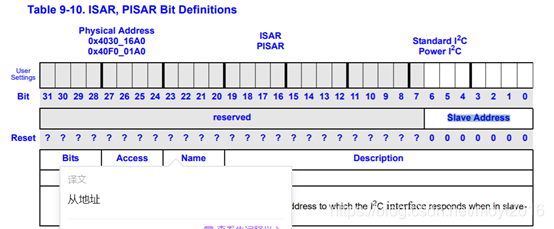

9.4.5数据和地址管理

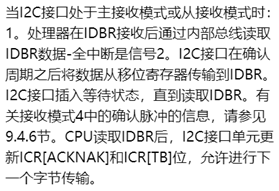

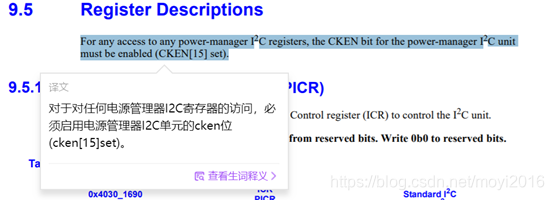

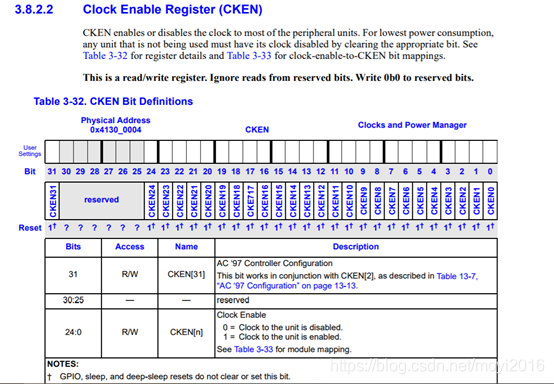

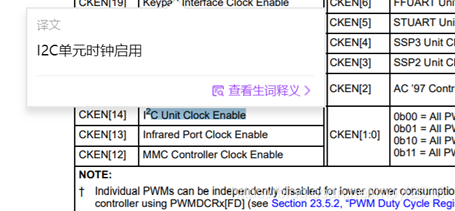

I2C数据缓存寄存器(IDBR)和I2C从地址寄存器(ISAR)管理数据和从地址。IDBR(参 见9.5.4节)包含-个字节的数据或一.个7位的从地址和R/NW位。ISAR包含处理器的可编程从地址。I2C接口在接收和确认完整字节后将接收到的数据放入IDBR。为了传输数据,CPU写入IDBR, I2C接口在设置ICR[TB]时将信息传递给串行总线。见9.5.1节。

当I2C接口处于主或从传输模式时:

1、 软件通过内部总线将数据写入IDBR,内部总线启动主事务或在设置ISR[ITE]后发送下一个数据字节。

2、 I2C接口在设置ICR[TB]时从IDBR传输数据

3、 启用时,当一个字节在I2C总线上传输,并且应答周期完成时,IDBR发送空中断就会被发出信号。

4、 当I2C接口准备在CPU编写IDBR之前传输下一个字节,并且停止条件不到位时,I2C接口插入等待状态,直到CPU向IDBR写入新值并设置ICR[TB]。

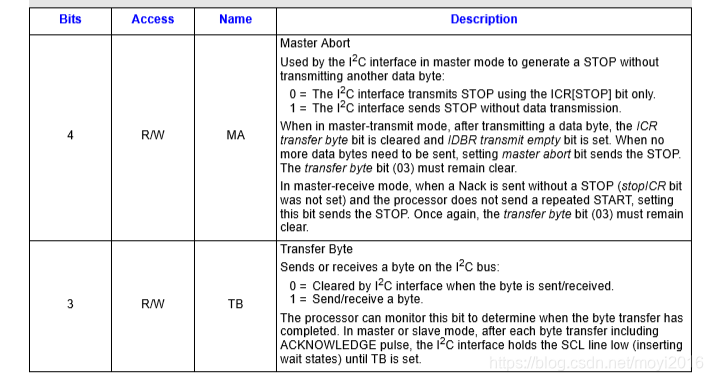

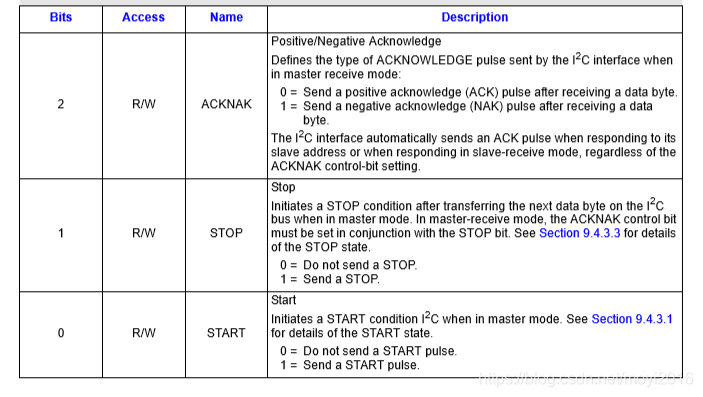

以下是自己答辩嵌入式IIC实验时准备的每个寄存器相对应位的作用,这里是为了存着自己用

如有需要pxa270芯片手册查找IIC以及中断相关寄存器则自行查找芯片手册

953

953

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?