昨天刚把OpenSPARC T1 处理器的运行环境(CentOS6)整理了一下,上传到的百度网盘(我的上篇文章Run OpenSPARC T1 on CentOS (百度网盘)_Jude_99的博客-CSDN博客),这个CentOS6(run OpenSPARC T1 的环境) 是我在2019年年初调试完成的。后来太忙了,再没动过。

今天再给自己挖个坑,准备以写博客的形式解析OpenSPARC™ T1 处理器,其实这个处理器中的任何一部分拿出来单独写都是一篇硕士毕业论文,涵盖的知识和内容很多,慢慢来吧! 会从OpenSPARC™ T1 Microarchitecture Specification 开始写起,边学边写。

作为一名数字IC设计工程师,这个处理器是很好的开源项目,对于初学者或是想成为数字IC设计工程师的本科生/研究生也是很好的开源项目。

OpenSPARC™ T1 Microarchitecture Specification

1.1 Introducing the OpenSPARC T1 Processor

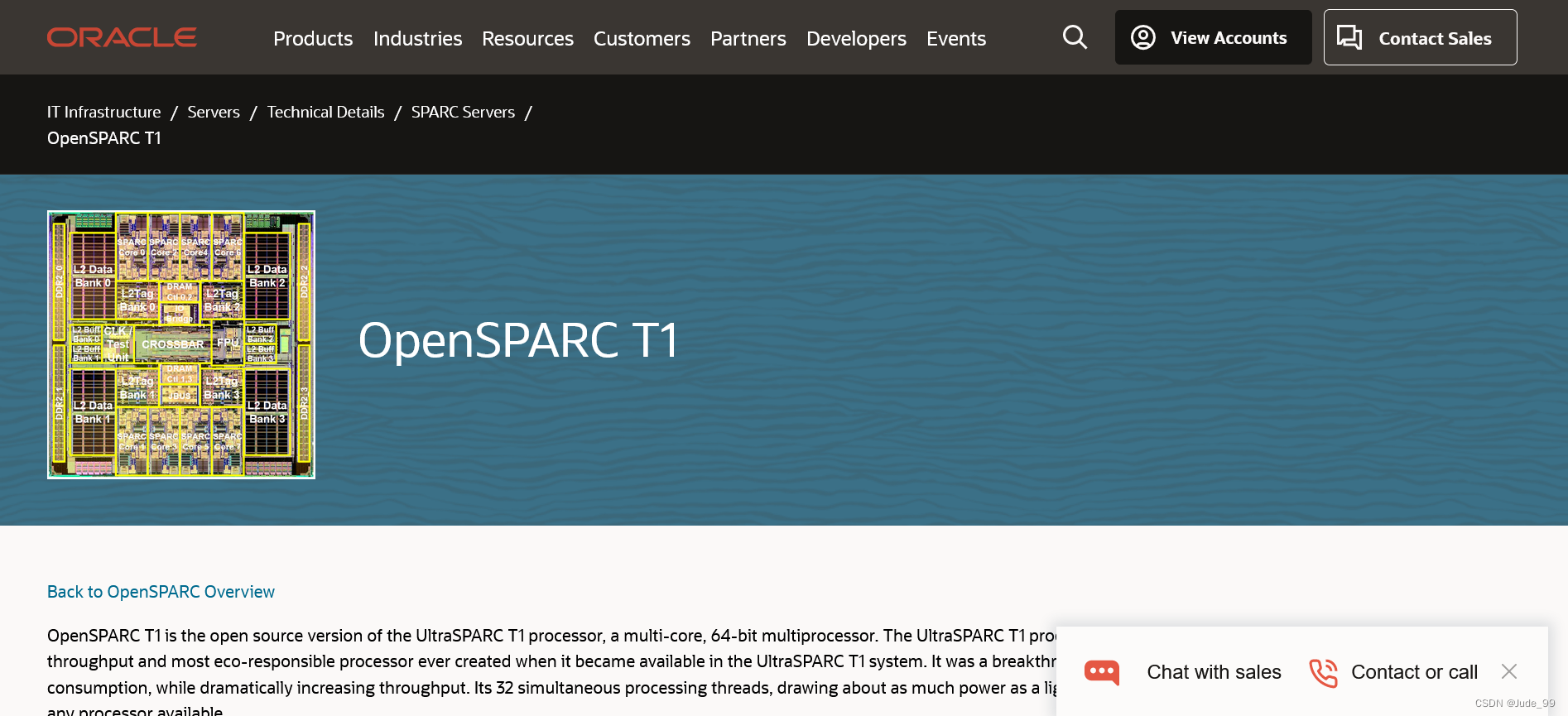

The OpenSPARC T1 processor is the first chip multiprocessor that fully implements

the Sun Throughput Computing Initiative. The OpenSPARC T1 processor is a highly

integrated processor that implements the 64-bit SPARC V9 architecture. This

processor targets commercial applications such as application servers and database

servers.

The OpenSPARC T1 processor contains eight SPARC® processor cores, which each

have full hardware support for four threads. Each SPARC core has an instruction

cache, a data cache, and a fully associative instruction and data translation lookaside

buffers (TLB). The eight SPARC cores are connected through a crossbar to an on-chip

unified level 2 cache (L2-cache).

The four on-chip dynamic random access memory (DRAM) controllers directly

interface to the double data rate-synchronous DRAM (DDR2 SDRAM). Additionally,

there is an on-chip J-Bus controller that provides an interconnect between the

OpenSPARC T1 processor and the I/O subsystem.

。

2909

2909

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?