目录

FEC Error Injection / FEC误码压力测试

Codeword & Symbol Error Configuration

Errored Symbol Per CW Configuration

FEC是什么

Codeword, Symbol and Bit Errors

-

FEC 是一种用于检测和纠正比特流中一定数量错误的技术,方法是在传输前将冗余比特和纠错码附加到信息块中。

-

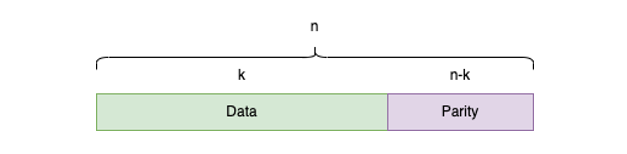

FEC 使用 n 个符号编码字(CW),由 k 个符号长的数据块和`n-k`符号长的奇偶校验块(编码和冗余比特)组成。我们用有序对 (n,k) 表示特定的FEC。

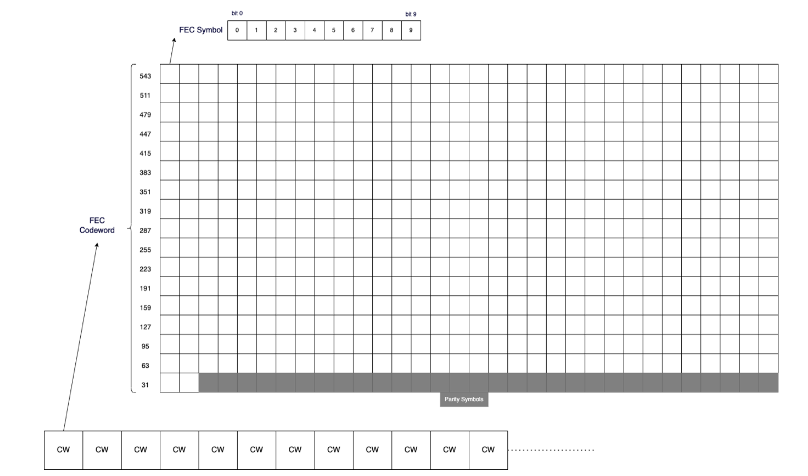

RS-FEC 符号

对于 RS-FEC KP (544,514) 和 RS-FEC-Int (544,514),10 个比特构成一个 FEC 符号,544 个符号构成一个 FEC 码元,其中 514 个是数据符号,30 个是奇偶校验符号,如下图所示。

FEC 码字、符号和比特

FEC测试需要关注哪些内容

基础的 FEC 性能监测

如今,大多数测试装置都在提供每个编解码字的错误符号表视图。下面的示例显示了一条 “坏 ”链路的输出(在这种情况下,链路被设计成会导致错误)。请注意,虽然编解码中的绝大多数符号都没有错误(0 个错误符号),但错误符号数迅速下降(每增加一个错误符号,错误符号数下降两个数量级以上),降至每个编解码 5 个错误符号。从 6 到 15 个错误符号计数的长尾以及每个码字仍有不可修正(>=16)的错误符号这一事实可以看出,这是一个坏链路。该链路可通过XenaManager“高级误码分析 ”套件工具进行进一步分析。

错误符号计数显示了系统在给定链路上的性能,但并不能验证或强调 FEC 的实现,而且对错误 “根源 ”的了解也很少。符号计数视图只显示使用测试集 FEC 块的链路测试集视图,而不是任何 DUT FEC 接收器的实现。

需要测试和验证的 FEC 特性

在研发和验证阶段,需要测试和验证柔性蚀刻电路的两个核心方面--柔性蚀刻电路的逻辑 “正确性 ”和实际实施的稳定性。虽然两者相互关联、相互交织,但都需要不同的测试方法来确保稳健性和可靠性。XENA通过其 FEC 测试应用集中的两个应用将这一概念体现出来:

FEC 压力测试

该测试重点关注 FEC 的逻辑验证,确保 FEC 在给定码字的错误计数和位置范围内具有现实的覆盖范围。鉴于潜在的组合不计其数,因此不可能涵盖所有组合,但这些应用足够 “智能”,能够提供可靠的覆盖范围。

XENA FEC 压力应用程序允许用户通过手动定位错误来精确探测 FEC,但它也支持全面的自动模式,该模式可扫描一个编解码中 1 到 15 个出错符号的巨大潜在错误位置范围,以提供可靠的覆盖范围,从而验证 FEC 的逻辑性能。虽然自动模式不可能覆盖所有出错符号位置和数量的组合,但该应用经过精心定制,可在合理的运行时间内提供最佳覆盖范围。用户可以调整测试的 “深度”,以匹配潜在的测试执行时间。如果自动测试显示出问题,则可以采用手动测试来调查逻辑的哪个区域以及在什么条件下没有按预期执行。

精准的 FEC 压力

即使 FEC 逻辑正确无误,被测硬件仍有可能因实施过程中的故障而失效,尤其是在电源完整性等方面。FEC 解码和检查块通常在宽并行总线结构中实施,其中包含许多基于与或非的逻辑门。错误检测和纠正会导致逻辑功

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

927

927

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?