最近项目因知识产权保密原因,需要生成网表提供给客户,上网查了vivado生成网表的方法主要有.edf网表和.dcp网表。但生成网表的方法要么不能用要么不全。经实践,以简单方便为主,介绍两种网表的生成及使用。

一、网表(.edf/.dcp)的生成

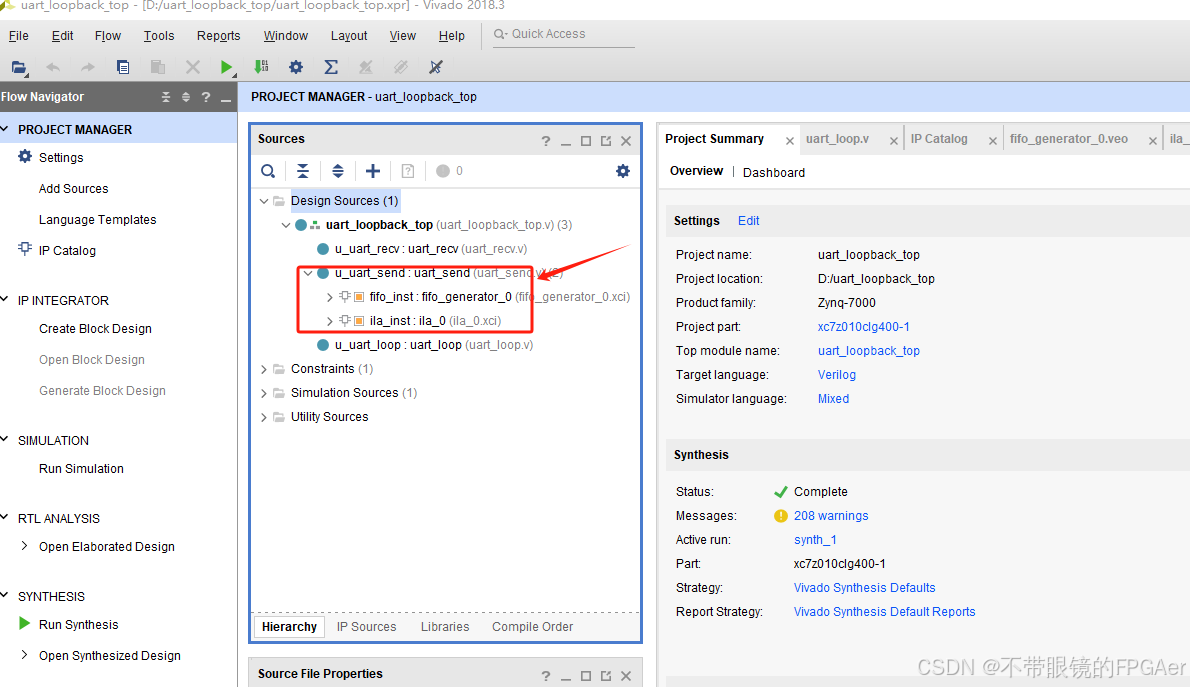

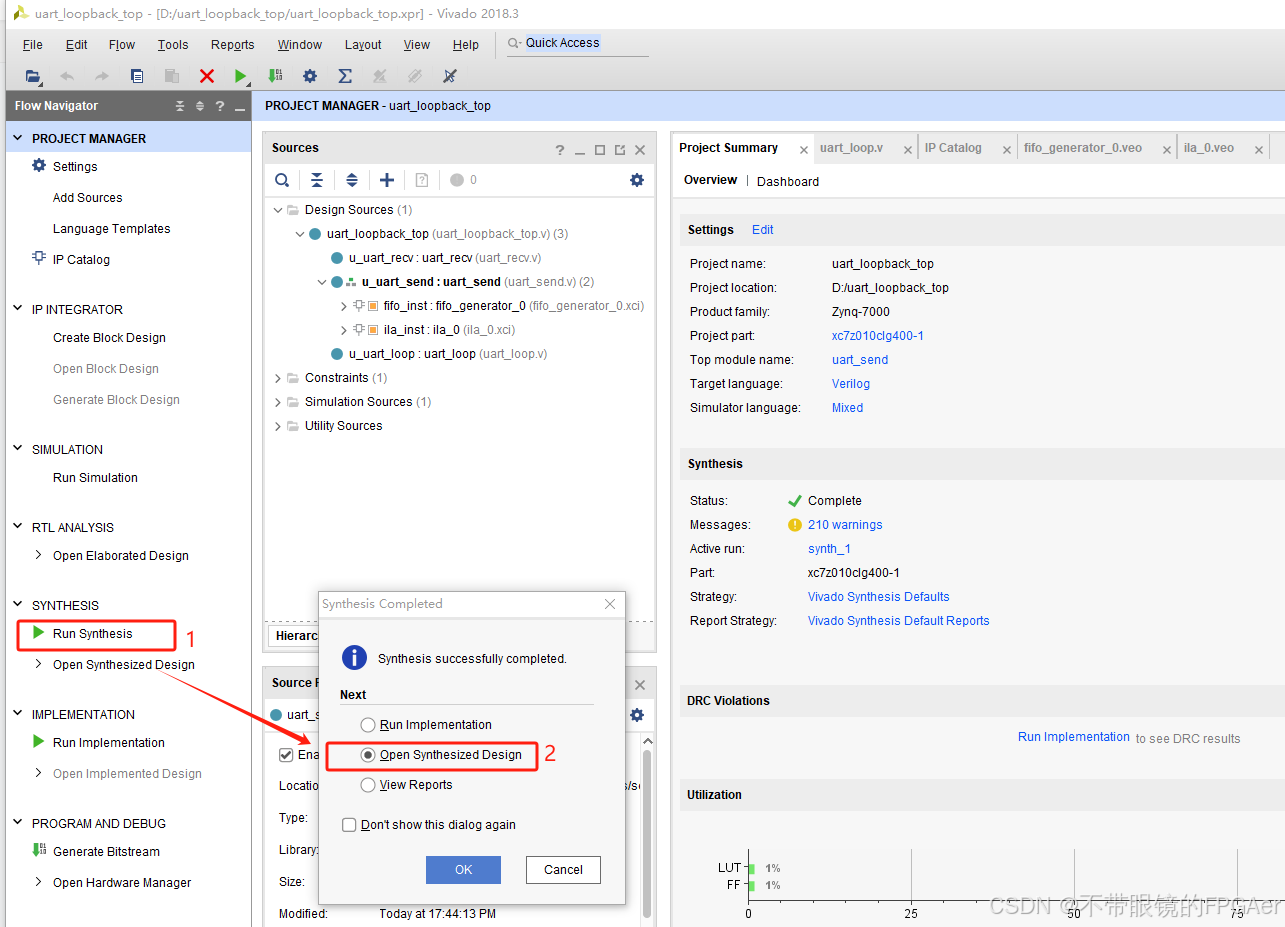

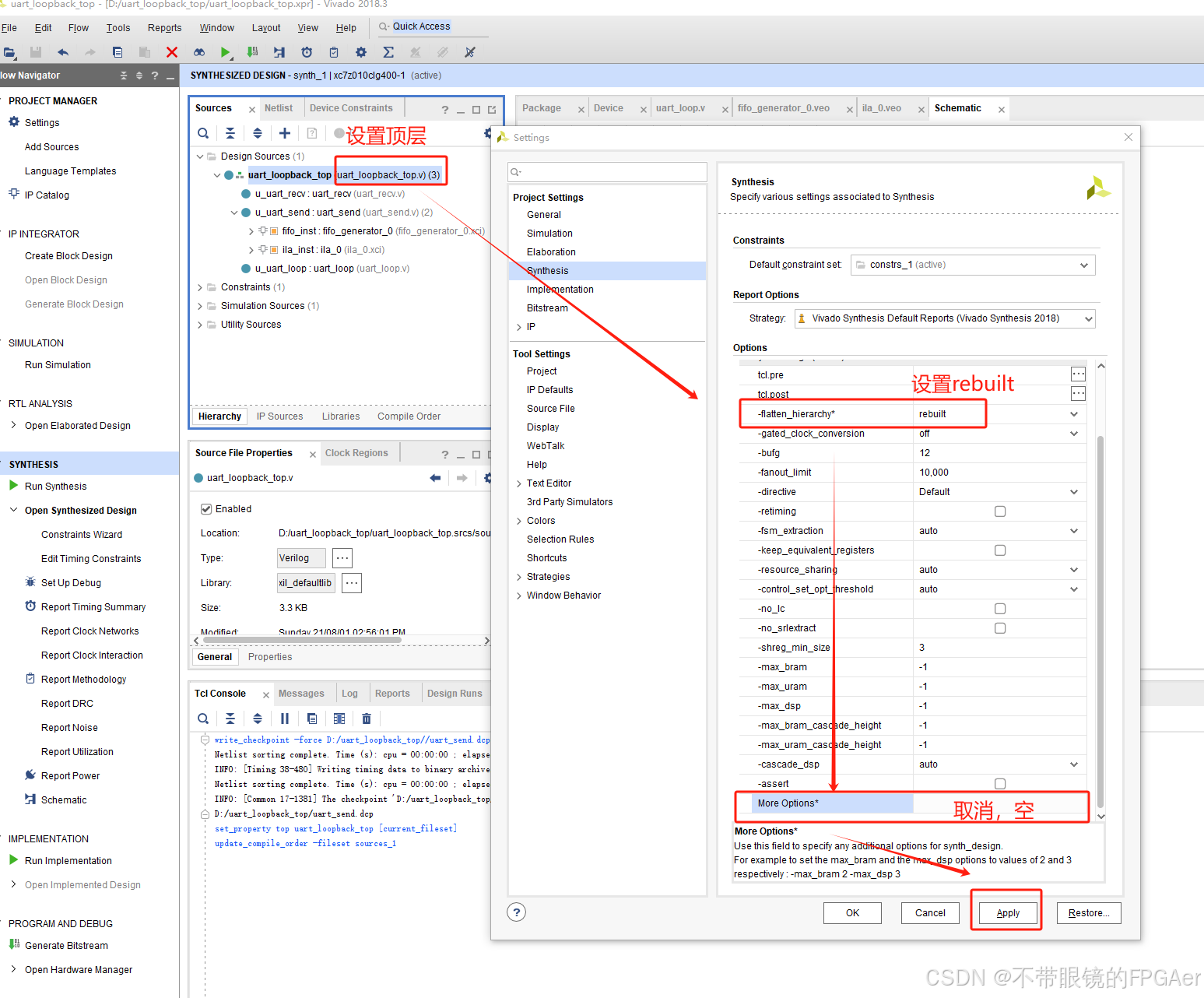

1、将工程中需要生成网表的模块(可以包含xilinx IP)设置为顶层(鼠标右键set as top),如下图。

设置前

设置后

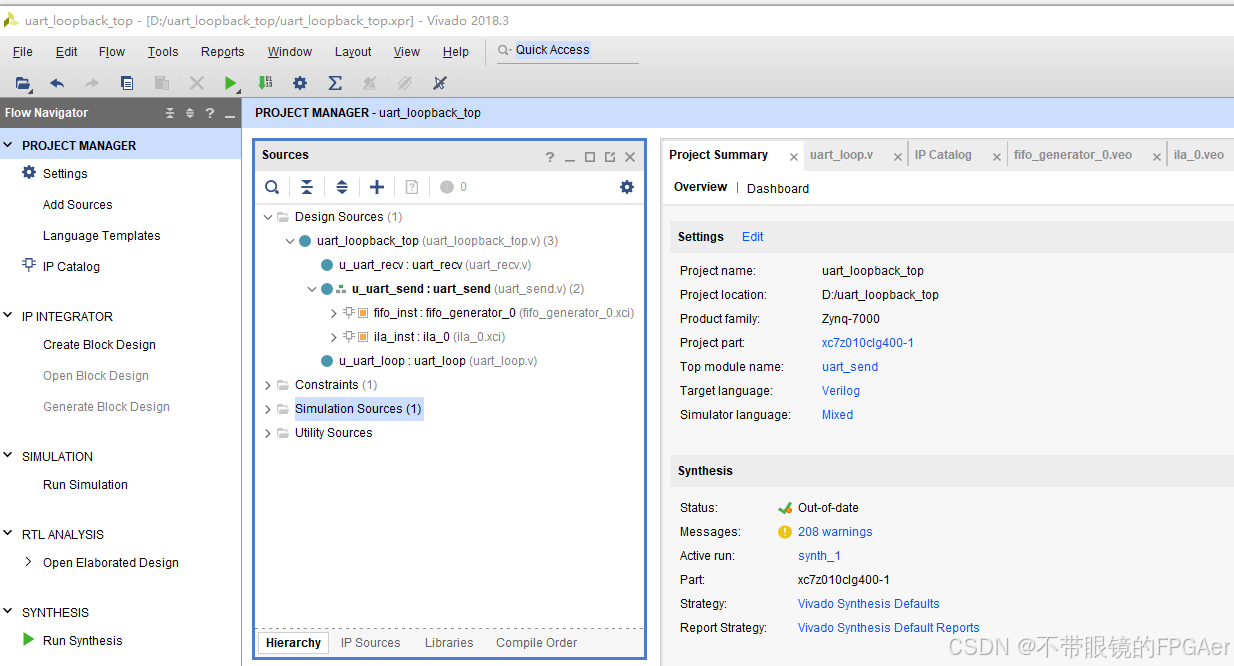

2、按下图顺序进行设置。

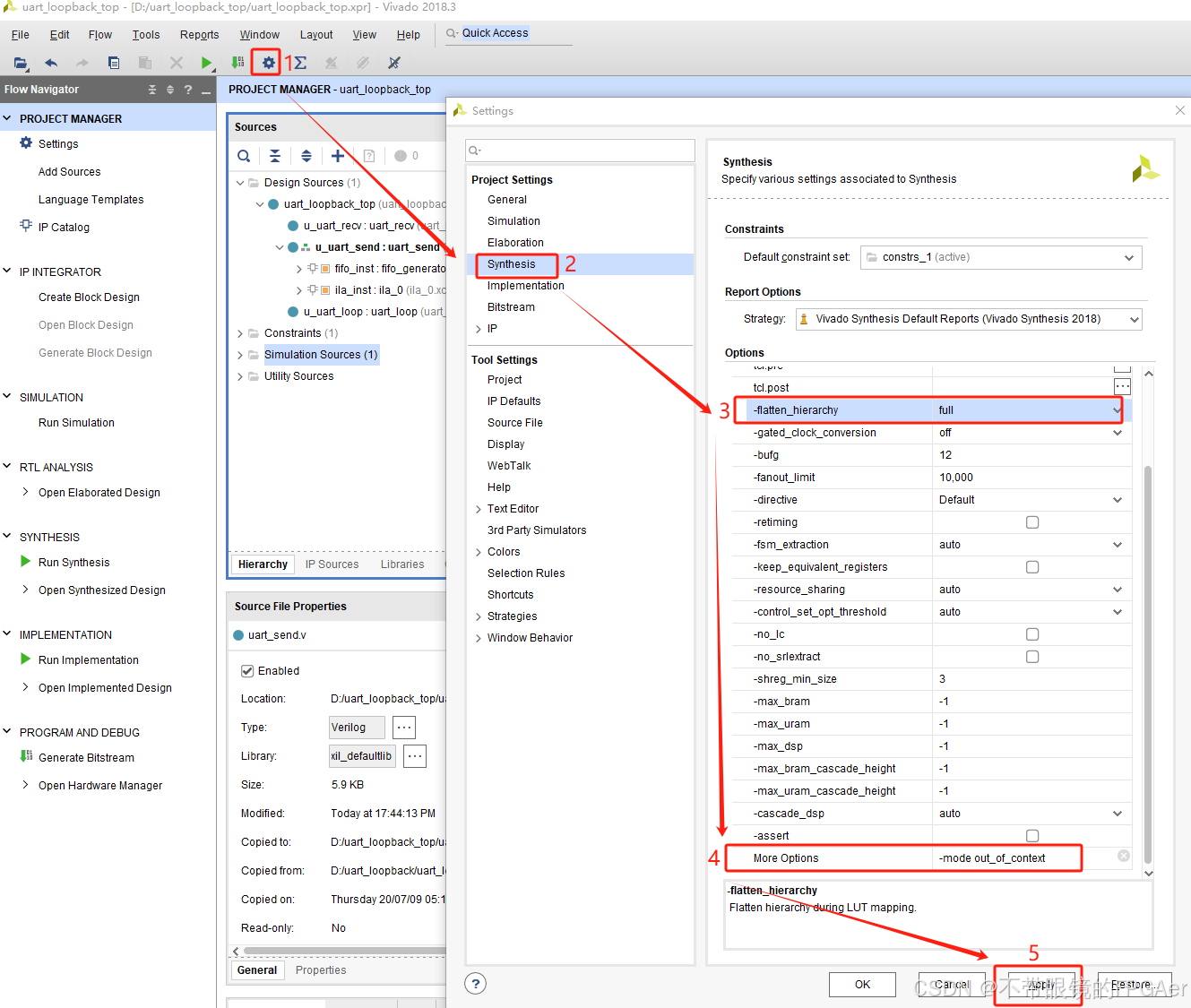

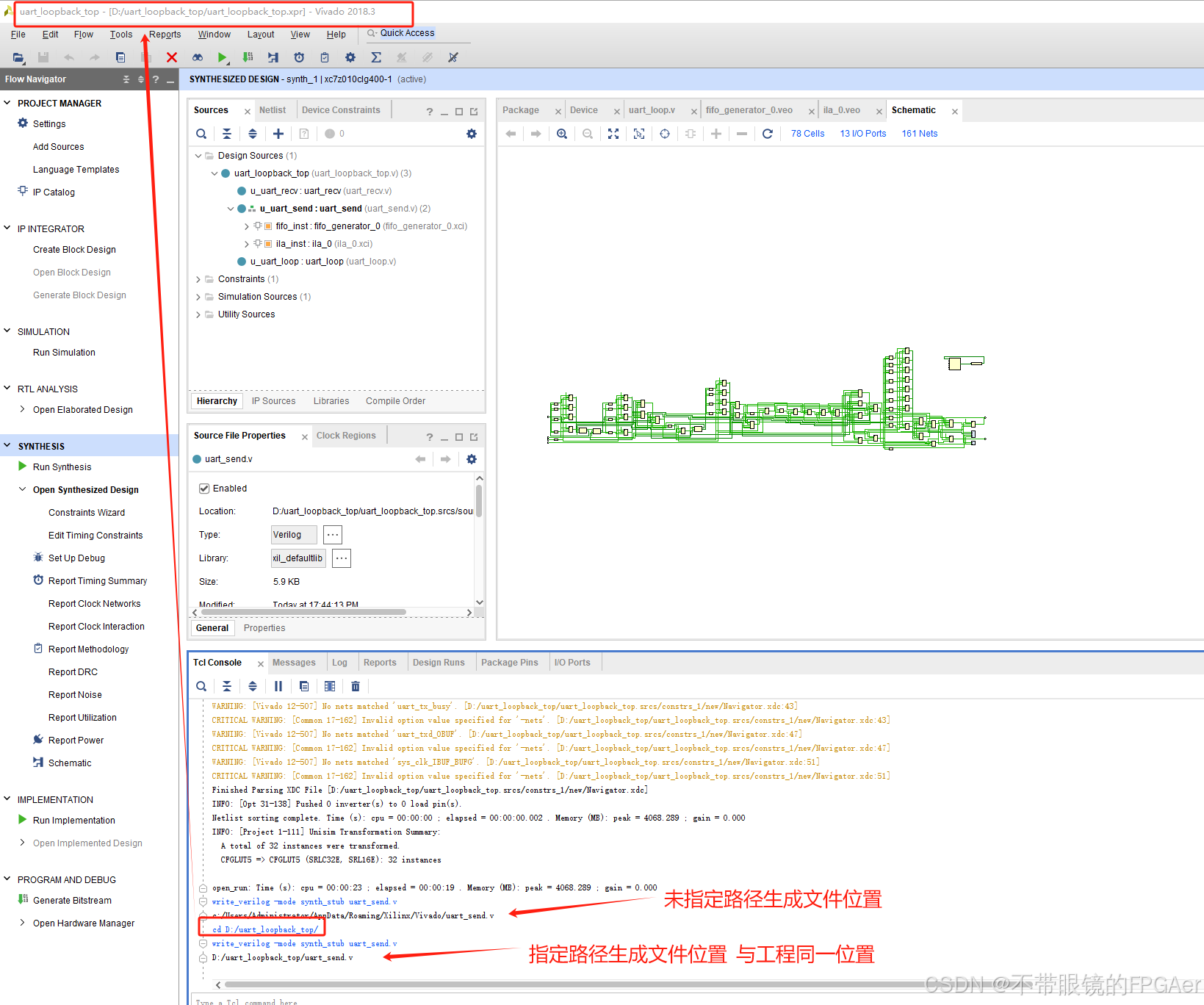

3、设置完成后,运行综合,综合完成后打开综合设计,如下图。

4、生成网表

4.1 生成edf网表:

4.1.1生成edf网表端口描述文件

当vivado版本低于18.1时,命令 write_verilog -mode port <design_name>.v

当vivado版本高于于18.1时,命令write_verilog -mode synth_stub <design_name>.v

生成文件的位置取决于是否指定生成文件的路径,路径命令:cd D:/xxx/xxx。如下图可看到差别。

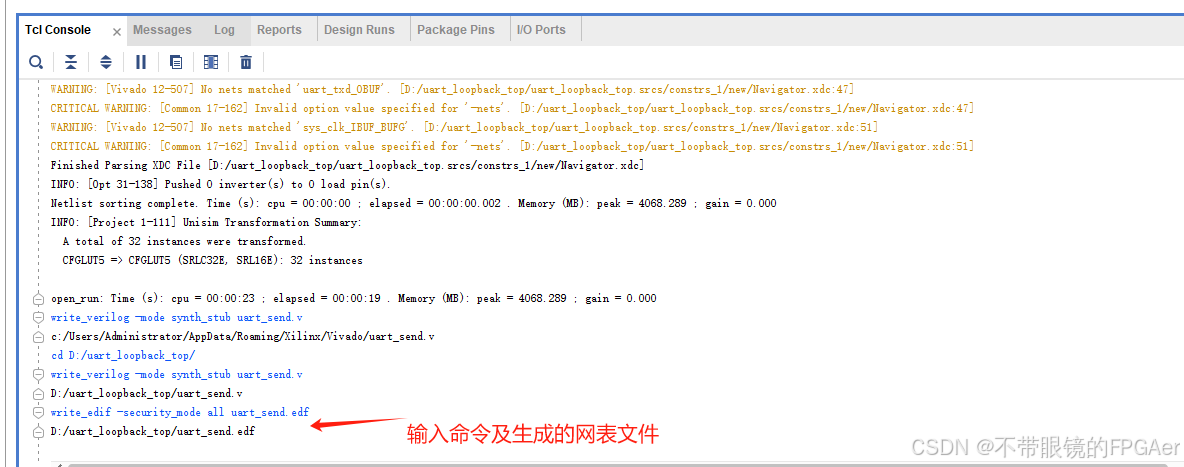

4.1.2生成网表文件

模块不包含xilinx IP 命令:write_edif <design_name>.edf

模块包含xilinx IP 命令:write_edif -security_mode all <design_name>.edf

生成的网表文件如下图,可在对应路径查看相关文件。

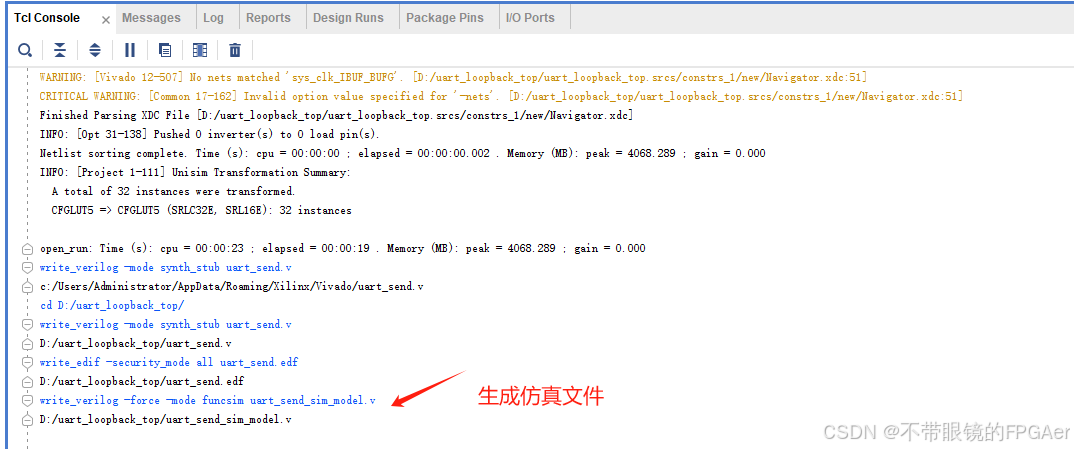

4.1.3 生成仿真文件

命令:write_verilog -force -mode funcsim <design_name>_sim_model.v

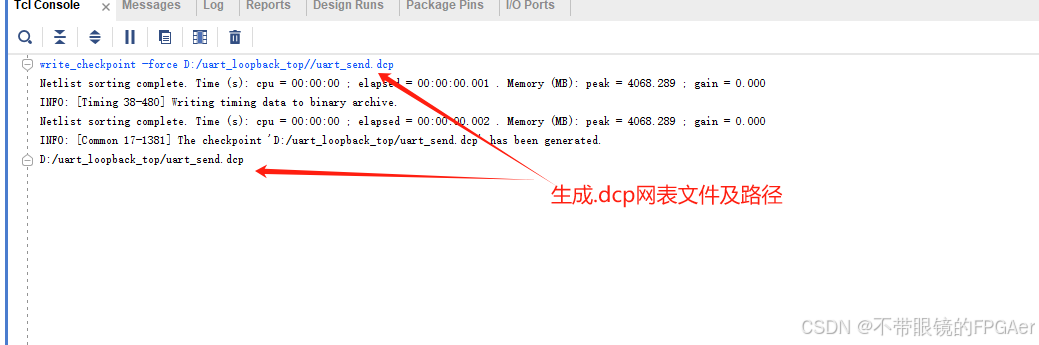

4.2 生成.dcp网表文件

前面1~3步骤完全一样,只是输入命令不一样而已。命令:write_checkpoint -force D:/x/xxx.dcp

如下图

5.将工程原顶层文件设置为top,并将设置还原,如下图

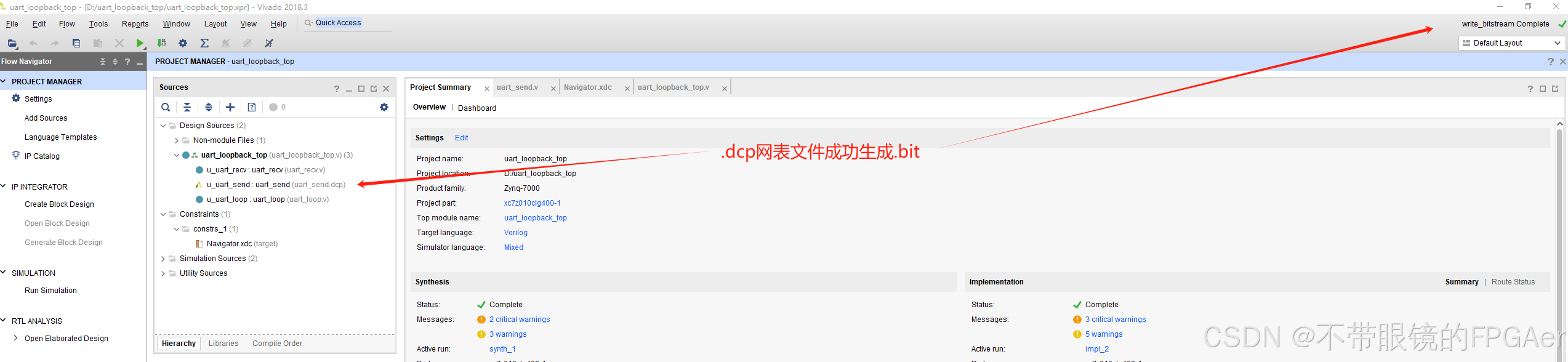

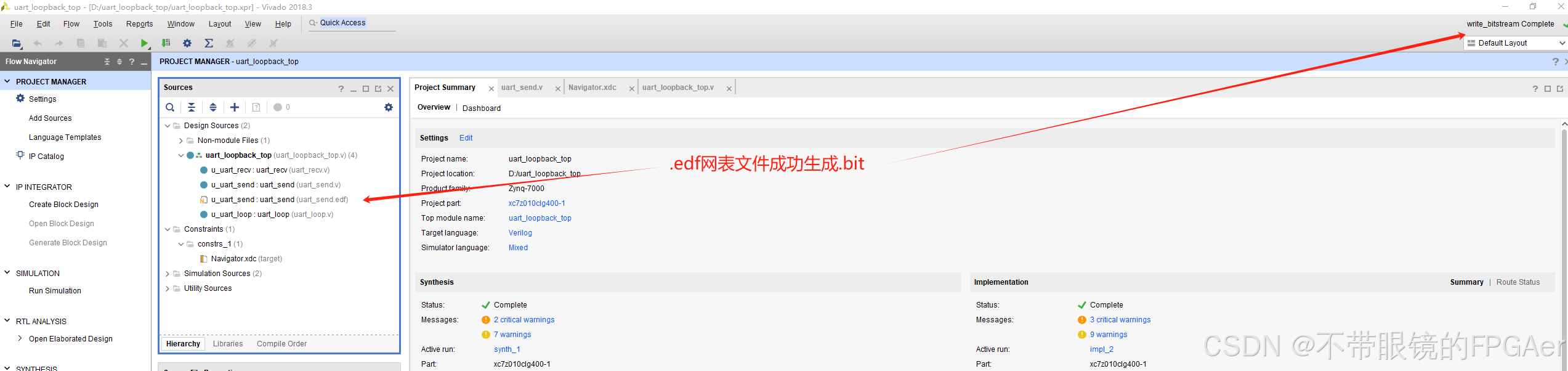

6、删除模块.v文件,添加2种网表文件,均可生成.bit,如下图。

7、.dcp网表文件生成仿真.v文件的一种方法。

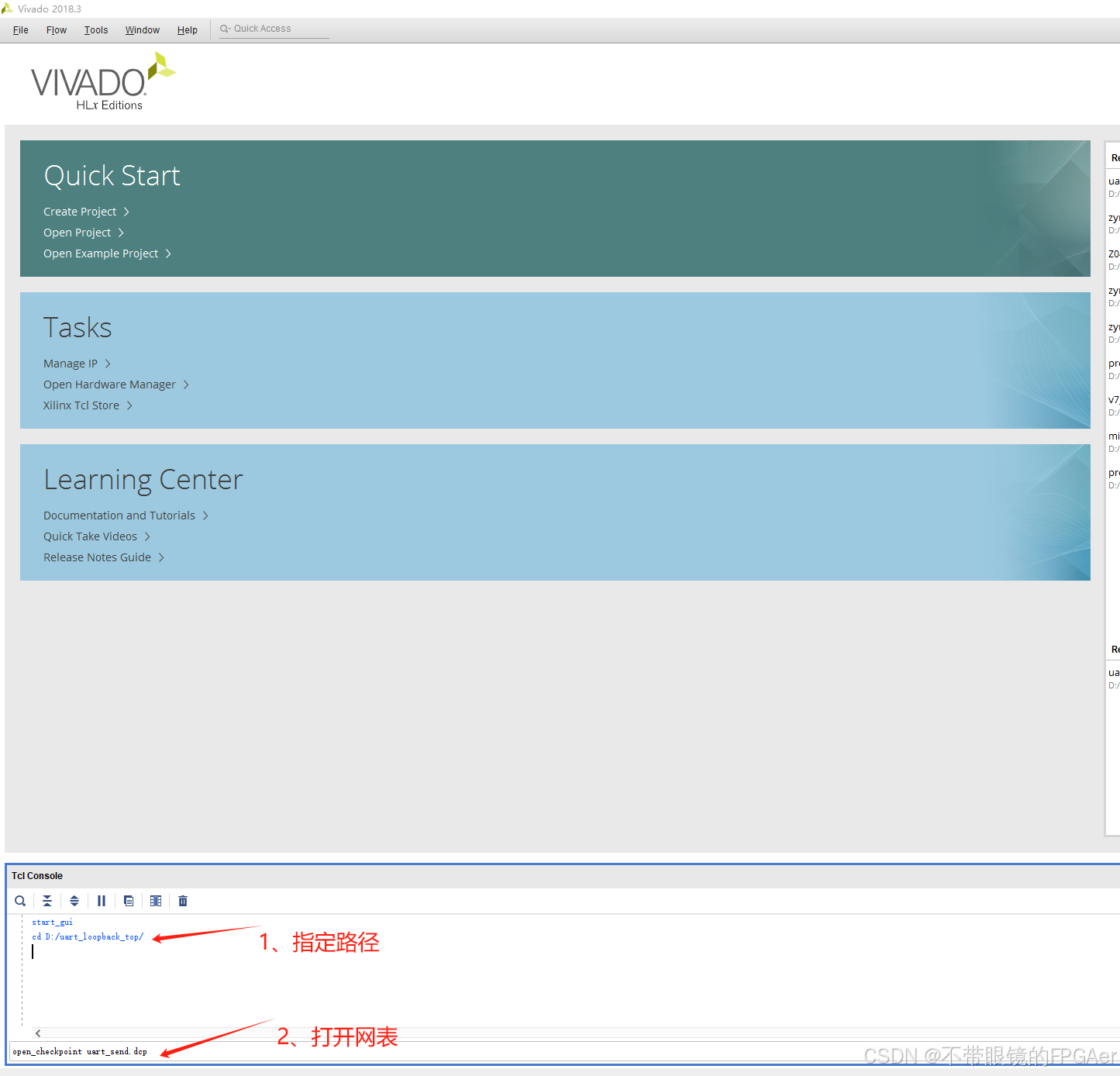

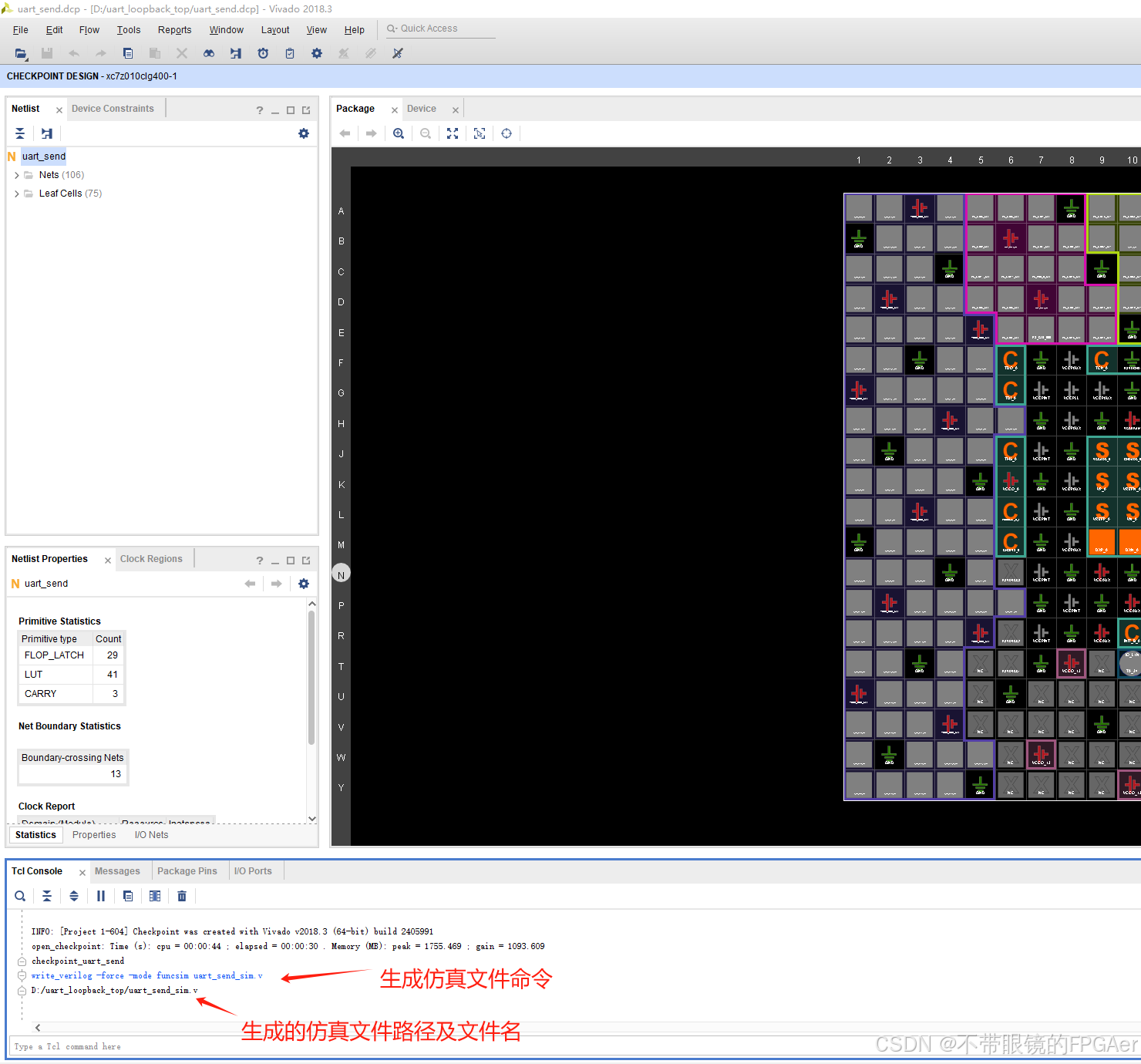

7.1 打开vivado软件,在开始界面的tcl命令栏中输入.dcp网表所在路径,命令:cd D:/xx/xx ,并打开网表文件,命令:open_checkpoint xx.dcp,如下图。

7.2 打开的工程界面,在tcl命令栏中输入:write_verilog -force -mode funcsim xxx.v 即可生成仿真文件,如下图。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?