PCB设计的具体内容

PCB设计的具体内容

建议PCB设计用4或者6层

4层定义:

第一层(顶层) -> 走线和地

第二层(内层) -> 走线和电源层

第三层(内层) ->完整的地层(可能有模拟地和数字地)

第四层(底层) -> 走线和地

说明:第二层和第三层可以互换,根据主要元件的布局层面确定.其紧邻层为地.

6层定义:

第一层(顶层) -> 走线和地

第二层(内层) -> 走线和电源层

第三层(内层) -> 信号

第四层(内层) -> 信号

第五层(内层) -> 完整的地层

第六层(底层) -> 走线和地

说明:第二层和第五层可以互换,根据主要元件的布局层面确定.其紧邻层为地.

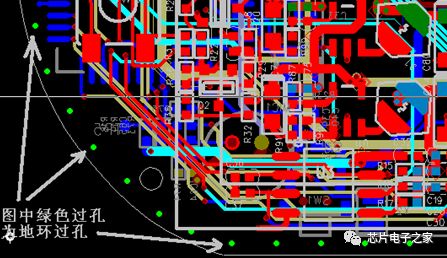

地层

用过孔创建一个地环在PCB的周围。使用的最小的过孔是0.254mm。建议使用0.3mm的过孔。每一个过孔的间距在1.27mm到2.5mm之间。尽可能的用通孔在每层每边都有。如图

电源层

分割电源层达到分配每个独立的电源. 独立的电源如下:

-

提供给DSP内核和模拟电源部分。

-

提供给数字I/O口和外围设备。

-

2.8V 和 VCC(提供给摄像头电源)该两路电源的纯度是获得好的图像质量的保证。

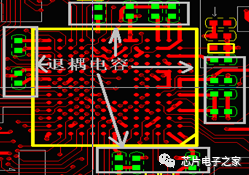

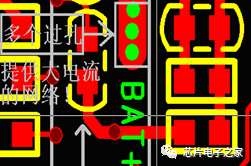

PCB走线如果可能的话,信号走线使用6mil, 走线间距使用6mil. 放置0.1uF的退耦电容在对应的DSP电源脚上,并尽可能的靠近.它的走线尽可能的粗.电源正极的走线最少要0.8mm,并尽可能的走在电源层上.因为电源上承载着大的电流.使用粗的走线能有助于电池的寿命和DC/DC转换的上电驱动以及降低纹波噪声.连接电池的正负极,最好使用3个以上的过孔,其中负极直接连到地层上.一个内层全部是整个地层。

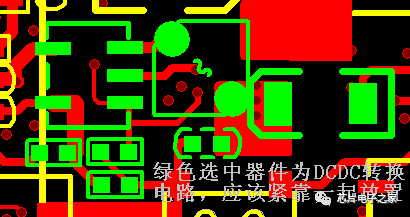

DC/DC转换器放置10uH的功率的电感在DC/DC的输出SW脚,并尽可能的靠近SW脚.并且尽可能的走线最少是0.6mm.一个好的建议是把DC/DC芯片跟功率电感尽可能的放在PCB的同一边.如果它们不在PCB的同一边的话.需要使用多个过孔连接功率电感到SW脚.DC/DC转换器的电源输入端的电源滤波电容最好是钽电容.当DC/DC芯片被使用,钽电容的值建议使用4.7uF或者是10uF.或者使用一个ESR值低的电容.而且功率电感的输出端最好连接0.1uF和10uF的电容.这些电容尽可能的靠近,并离DC/DC IC的输出端最多4mm远.被放置的0.1uF的退耦电容最好放在10uF的电容的前面。

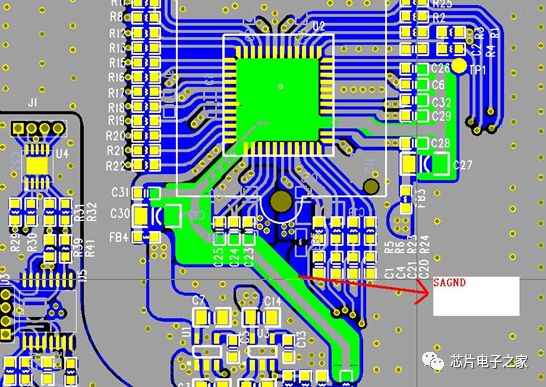

模拟地和数字地模拟地和数字地最好被分开,通过电感或0 欧电阻连接,如果板太小无法分割模拟和数字地,可以直接相连,但是要考虑数字信号的地回路不要影响到模拟部分。为了帮助提高模拟部分质量各自走自己的地环路.这样是避免模拟部分从数字地耦合数字信号.特别是对音频地和SENSOR的地.

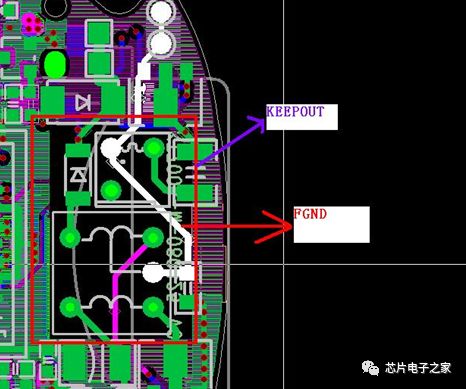

闪光灯的地:FGND请不铺铜,且此网络最好与其它的元件、网络保持3MM以上.

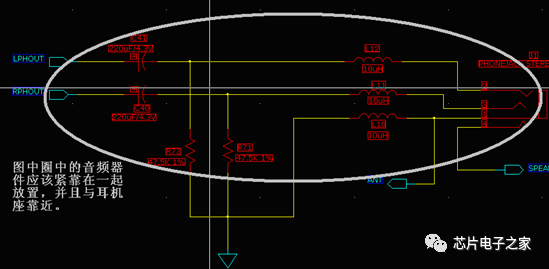

所有Audio部分的走线尽可能的宽。音频输出的所有元器件应该尽可能靠近耳机插座.建议把这些与音频有关的元器件和走线放在一起,并尽可能的与系统音频输出在PCB的同一部分.尽量避免从其他的信号耦合噪声.音频输出走线的宽度不少于0.254mm的宽度。耳机布局走音频信号线应该远离NAND Flash的数据线和控制线以及高频信号,也要远离晶振电路.如果音频信号线走线离这些信号线太近就会影响音频的质量.

(备注:上图中的音频器件应该都放在一起,并与音频输入、输出的插座尽可能的靠近。走线尽量的宽。避免过孔,避免跨越数字和模拟地。Audio部分的地环路不允许有多路返回和环状回路。)

·AUDC_VREFADC,AUDC_VREFDAC, AUDC_VCM信号的滤波钽电容10uF和瓷片电容0.1uF尽量靠近主控IC附近.其走线需要远离高频数字信号。如SDRAM,NAND FLASH的数据线,地址线和控制线。

麦克风走声音输入信号线应该远离NAND Flash的数据线和控制线以及高频信号,也要远离晶振电路.如果MIC输入信号走线离这些信号线太近就会影响音频输入的质量.走MICBIAS模拟线应该远离DC/DC的功率电感,数字信号线,控制线和晶振电路.放置滤波器件尽可能的靠近麦克风. MIC输入信号与MICBIAS电源信号需要隔开距离. 避免相互干扰.最好对MIC输入信号做包地处理.麦克风的地线应该分开数字地线.避免耦合数字噪声.

Line in 方面的考虑

Line in的输入耳机插座的信号线应该放置分离电阻在它的的输入端.保护芯片避免因为输入信号的冲击损坏芯片.与Line in有关的元器件也应该尽可能的放置在一起.地线也与数字地线分开.

Sensor方面的考虑

Sensor的供电要求很稳定且纯的2.8V和1.8V的电源.所以,建议LDO和大容值的胆电容被使用在该电源部分. Sensor的模拟地要求独立的地环.以避免从大地受到干扰噪声.

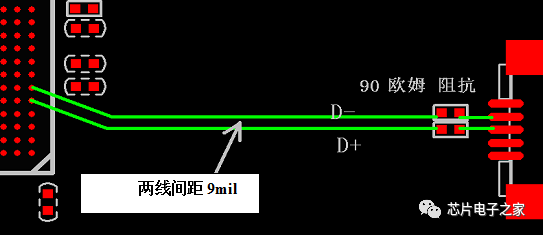

USB方面的考虑

USB的差分信号线保持平行走线,以达到90 ohm的差分阻抗.由于PCB和走线的因素这样的平行走线的要求是很难达到的.为了避免这样的偏差尽可能的减少.建议走线宽度不少于0.254mm,差分信号线的间距不少于0.254mm.这样尽可能的接近90 ohm的差分阻抗.

高速的USB

为了获得理想的信号质量建议高速USB的差分信号线与其他的信号线的间距最好是0.5mm以上.这样有助于避免交互干扰.另一种选择达到90 ohm的差分阻抗的方法.可以在USB的差分信号线对加上6pF到地.因为有些设计需要这些,但是当有些PCB设计达不到90 ohm的差分阻抗就需要这些.PCB布局时,这些焊盘需要保留在需要的时候.

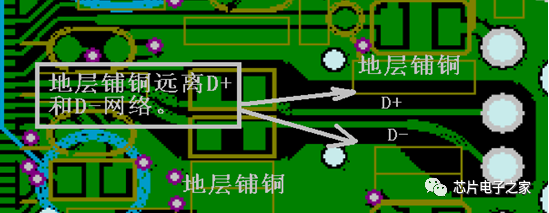

D+、D- 的线宽跟线距为9mil ,这两个信号线旁不可以铺铜,应该将地裸空。如下图:

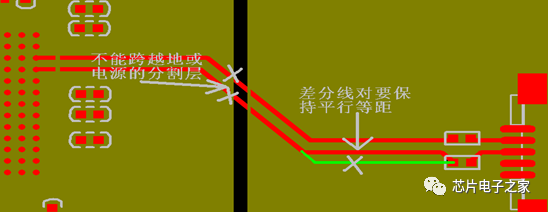

一些较差的USB走线

一些很普通的较差的USB走线是USB走线使用了过多的过孔.跨越电源和地线的分割层.USB的信号对的两边地线不对称.不平行的信号对和过多的过孔将会引起阻抗的不连续这样会导致较差的信号质量.

SDRAM部分走线考虑

1.SDRAM时钟信号

时钟信号频率较高,为避免传输线效应,按照工作频率达到或超过75MHz时布线长度应在1000mil以内的原则及为避免与相邻信号产生串扰,走线长度不超过1100mil,线宽10mil,与其他外部信号间距20mil。最好包地。

2.地址、片选及其它控制信号:

线宽5mil,同类型控制信号间距10mil,与其他外部信号间距20mil,过孔尽量少,最好在2个以内。与时钟信号做等长度走线处理。

3.SDRAM数据线:

线宽5mil,同类型数据信号间距5mil,与其他外部信号间距10mil,尽量在同一层布线,数据线与时钟线的线长做等长度走线处理。

ESD方面的考虑

-

要求有好的ESD的PCB设计建议使用6层的PCB设计,并有独立的电源层和地层.所有的元器件的地盘都应该连接到大地的地环盘.磁珠也应该连接到每个信号线和外围设备之间.压敏电阻也应该加到USB的各个信号线,音频信号线和按键的信号线到地.按键和开关尽量使用绝缘体的元器件.USB插座应该被非导体的胶体盖住.如果金属或者导体被使用的话,应该设计让静电电流均匀的分布在PCB板的四周.按键和开关与PCB间的空气的空隙尽可能的小.避免使用有金属外环的耳机插座.

-

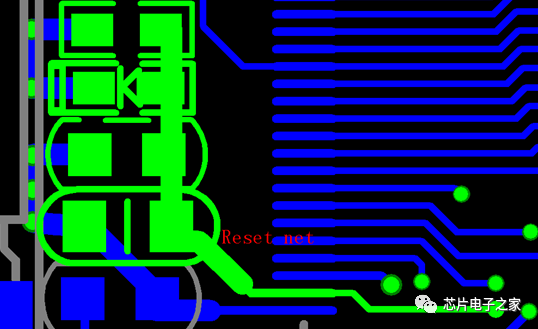

有关复位电路部分。在复位脚与大地之间串接68pF的陶瓷滤波电容。复位电路部分的所有元器件应该尽可能的都靠近芯片的复位脚。复位走线尽量的短。如果走线长的话要走中间层。如下图所示

-

-

在对PCB放静电时,为了更多的大地分布电荷。就需要在PCB的周围尽可能多的设置地VIA是非常有帮助的。

-

对USB_VDD33和VDD33的LDO的NC脚上都跨接0.01uF的滤波电容到地。滤除静电对电源的瞬间的影响。

-

芯片code 电源网络是芯片核心电源的抗静电的稳定性。需要增加68pF和0.01uF的陶瓷电容到地。并尽可能的靠近芯片的管脚。

-

尽可能的加大地的面积。并尽可能让地层完整。整机的电源走线要求尽量粗而短。电源与地的回路要尽量的小。只有这样才能保证静电很快的被释放掉。

-

晶振外壳要接地.USB外壳与DGND经过0.1uF电容连接.靠近USB附近的DGND尽量多打过孔。

EMI方面的考虑

放置0.1uF的滤波电容在各自对应的电源脚上. 放置10uH的DC/DC功率电感尽可能的靠近DC/DC转换器的SW脚,并使用有磁环包裹的功率电感.这有助于抑止DC/DC转换的高次谐波的噪声.放置0.1uF和10uF的滤波的电容,并尽可能靠近功率电感的输出端.数字信号线尽量走在内层.时钟信号线的走线尽量的短.一些EMI器件在必要的时候可以加在重要的信号线上.

6257

6257

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?