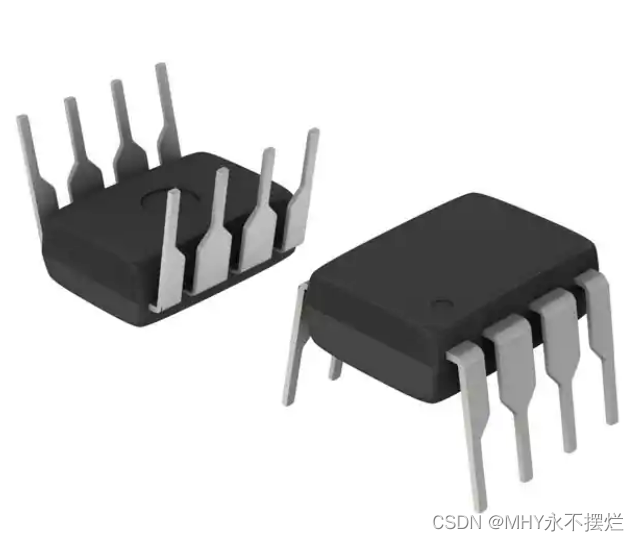

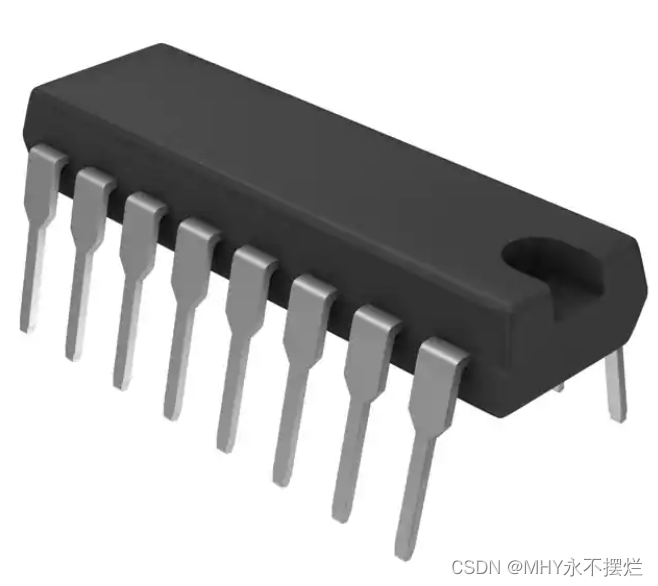

双列直插封装(英语:dual in-line package) 也称为DIP封装或DIP包装,简称为DIP或DIL,是一种集成电路的封装方式,集成电路的外形为长方形,在其两侧则有两排平行的金属引脚,称为排针。DIP包装的元件可以焊接在印刷电路板电镀的贯穿孔中,或是插入在DIP插座(socket)上。

DIP包装的元件一般会简称为DIPn,其中n是引脚的个数,例如十四针的集成电路即称为DIP14,概述图即为DIP14的集成电路。

DIP-8

DIP-16

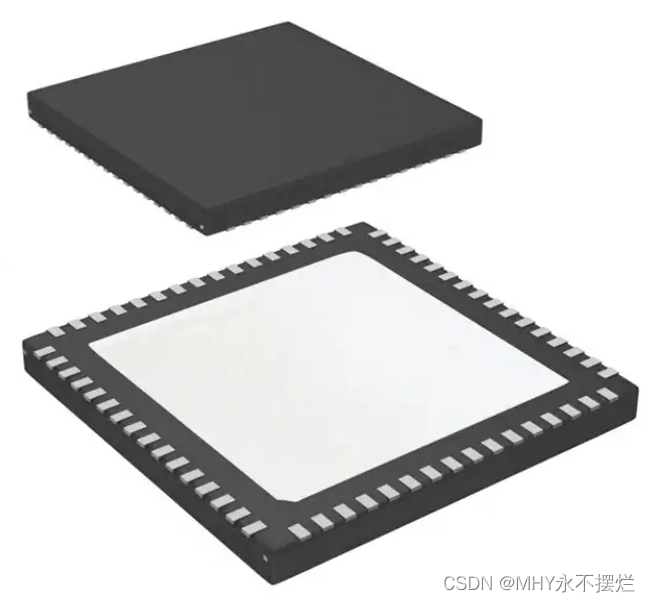

QFN是一种无引脚封装,呈正方形或矩形,封装底部中央位置有一个大面积裸露焊盘用来导热,围绕大焊盘的封装外围四周有实现电气连结的导电焊盘。由于QFN封装不像传统的SOIC与TSOP封装那样具有鸥翼状引线,内部引脚与焊盘之间的导电路径短,自感系数以及封装体内布线电阻很低,所以它能提供卓越的电性能。此外,它还通过外露的引线框架焊盘提供了出色的散热性能,该焊盘具有直接散热通道,用于释放封装内的热量。通常将散热焊盘直接焊接在电路板上,并且PCB中的散热过孔有助于将多余的功耗扩散到铜接地板中,从而吸收多余的热量。

QFN-64

这种技术的中文含义叫方型扁平式封装技术(Quad Flat Package),该技术实现的CPU芯片引脚之间距离很小,管脚很细,一般大规模或超大规模集成电路采用这种封装形式,其引脚数一般都在100以上。该技术封装CPU时操作方便,可靠性高;而且其封装外形尺寸较小,寄生参数减小,适合高频应用;该技术主要适合用SMT表面安装技术在PCB上安装布线。

QFP-64

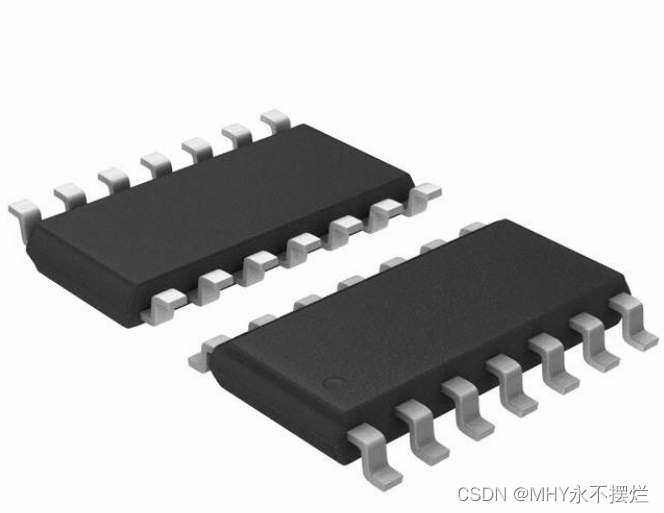

SOIC(Small Outline Integrated Circuit Package),小外形集成电路封装,指外引线数不超过28条的小外形集成电路,由SOP (Small Out-Line Package)封装派生而来,一般有宽体和窄体两种封装形式。其中具有翼形短引线者称为SOL器件,具有J型短引线者称为SOJ器件。

SOIC是表面贴装集成电路封装形式中的一种,它比同等的DIP封装减少约30-50%的空间,厚度方面减少约70%。与对应的DIP封装有相同的插脚引线。对这类封装的命名约定是在SOIC或SO后面加引脚数。例如,14pin的4011的封装会被命名为SOIC-14或SO-14。

SO-14

SO-8

SOT-23

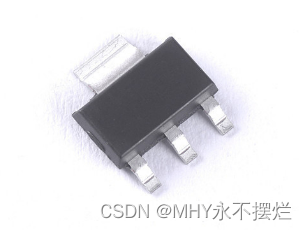

SOT-223

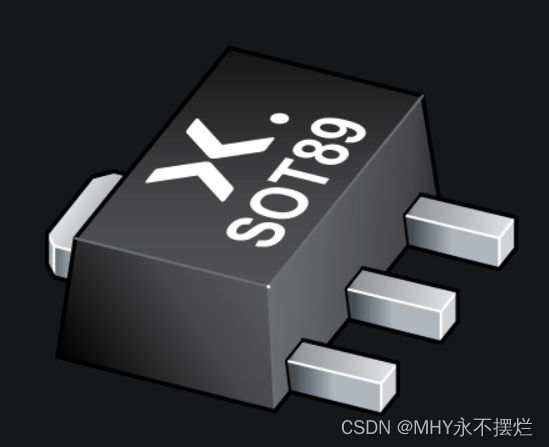

SOT-89

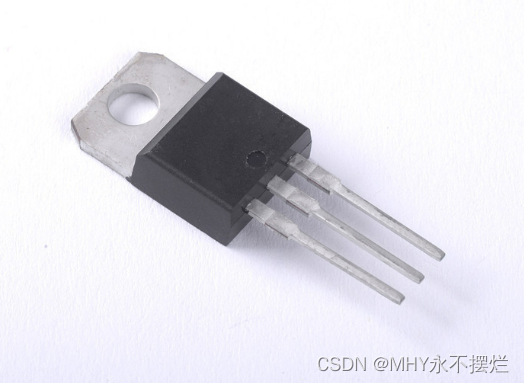

TO-220

TO-263,TO-252

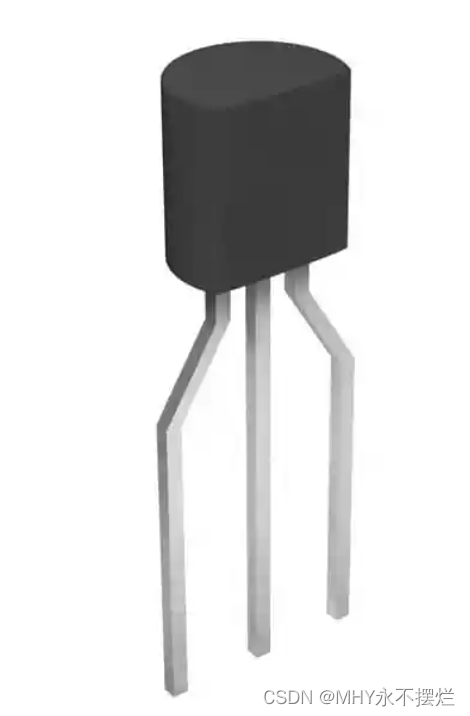

TO-92

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?