- Quartus是Intel的FPGA设计软件,主要用来对硬件引脚进行配置,以及写FPGA的配置文件

- 用Quartus来写FPGA实现流水灯程序步骤

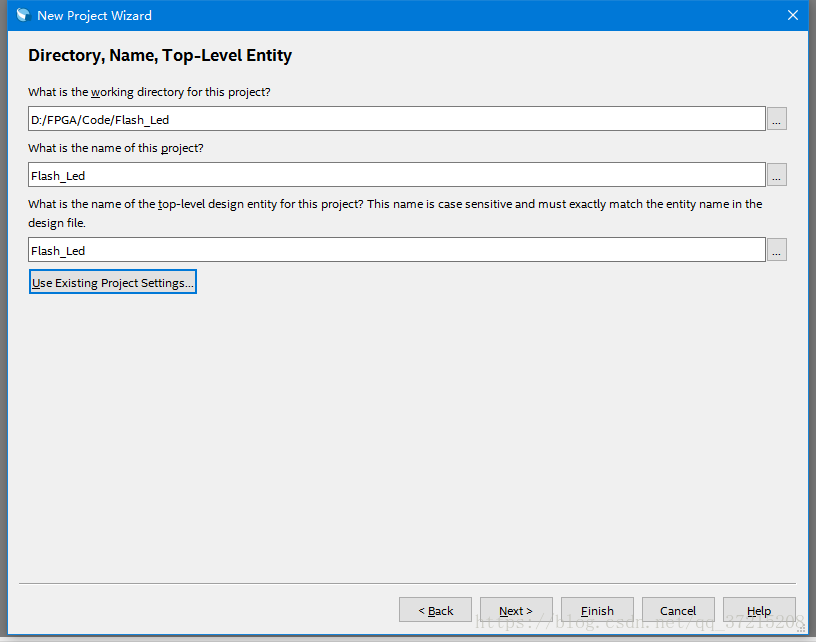

- 首先新建工程File->Project Wizard(记得保持工程名称和顶层文件名称保持一致)

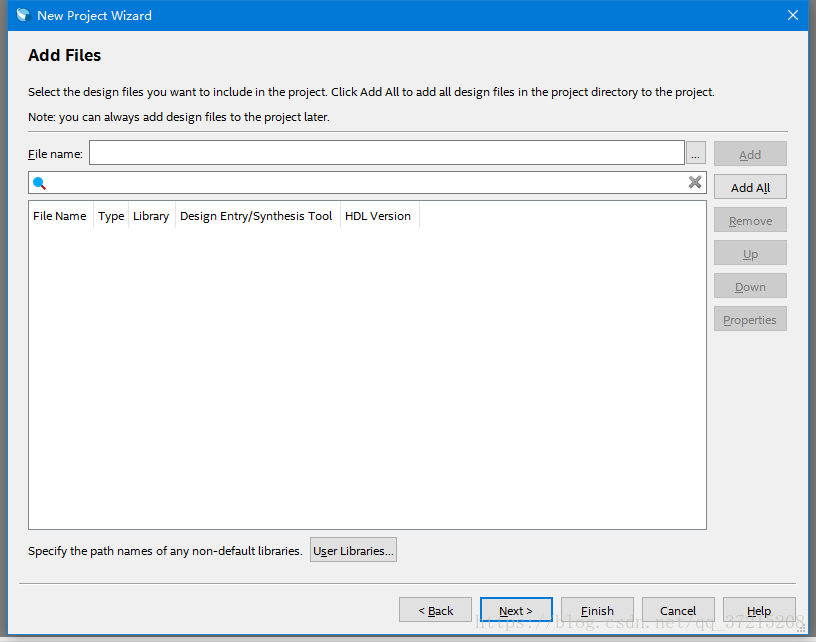

- 一路next到这里(在这里继续next,因为我们等下会继续添加新文件)

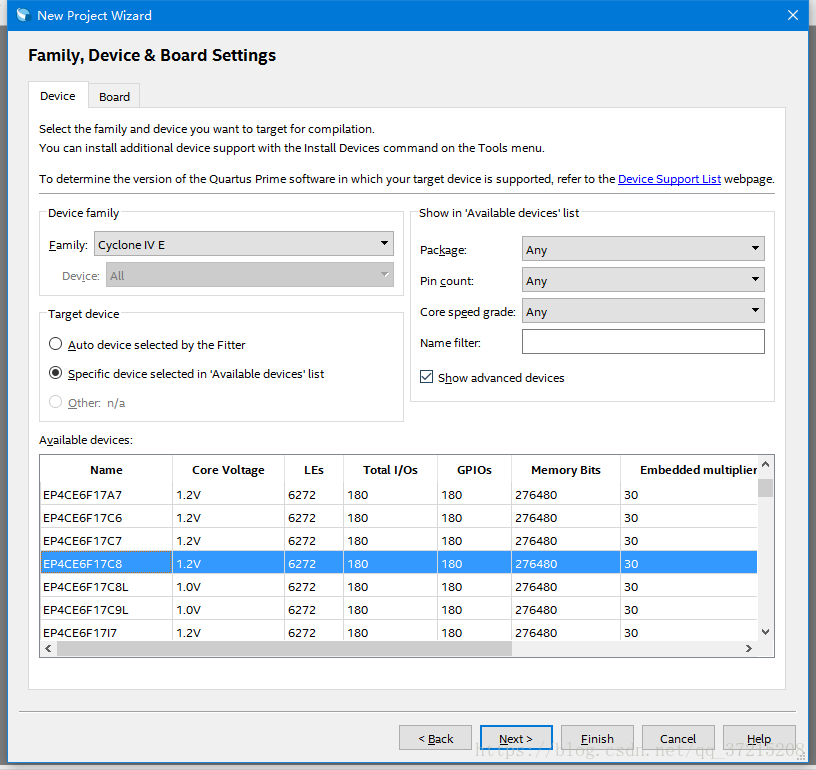

- 之后到了这里,选择自己的板子型号

- 在这里,一些基本资源:

-

CoreVoltage是内核电压,Cyclone IV的内核电压是1.2V。

-

LE是Altera最基本的逻辑单元,LEs表示FPGA的所有的逻辑资源, 我们这款芯片的逻辑资源数为6272。

-

User I/Os表示用户IO数,这里共有180个IO可以供用户使用。

-

Memory Bits与embedded multiplier 9-bit elements实际是一回事,

-

- 首先新建工程File->Project Wizard(记得保持工程名称和顶层文件名称保持一致)

FPGA ALTERA Cyclone IV实现流水灯

最新推荐文章于 2024-09-26 19:43:28 发布

这篇博客介绍了如何利用Intel的FPGA设计软件Quartus,创建一个针对ALTERA Cyclone IV FPGA的流水灯程序。从新建工程到配置硬件资源,再到编写代码和烧录程序,详细阐述了整个流程。文中还提及了FPGA的基本资源,如LEs、User I/Os、Memory Bits和PLL,并提到了最终的仿真工具Modelsim。

这篇博客介绍了如何利用Intel的FPGA设计软件Quartus,创建一个针对ALTERA Cyclone IV FPGA的流水灯程序。从新建工程到配置硬件资源,再到编写代码和烧录程序,详细阐述了整个流程。文中还提及了FPGA的基本资源,如LEs、User I/Os、Memory Bits和PLL,并提到了最终的仿真工具Modelsim。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3072

3072

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?