转自:https://blog.csdn.net/MyArrow/article/details/8500155

一、 主机控制器(Host Controller)

1.1 主机控制器简介

• UHCI: Universal Host Controller Interface (通用主机控制接口, USB1.0/1.1)

• OHCI: Open Host Controller Interface (开放主机控制接口,USB1.0/1.1)

• EHCI: Enhanced Host Controller Interface (用于USB2.0高速设备的“增强主机控制接口”)

USB的拓扑结构决定了主机控制器就是最高统帅,没有主机控制器的要求设备永远不能主动发数据。所以主机控制器在USB的世界里扮演着重要的角色,它是幕后操纵者。

问题:比如说Host发送Setup包获取设备描述符是怎么发出去的?

这个过程包含很多信息,比如:如何在D+和D-这两根线上传过去的、又传过来的。 这一切的工作都是主机控制器给我们做的。USB Host控制器的规范有很多种,这里只介绍混得不错的EHCI和OHCI。这个EHCI主要针对高速的USB设备。如果要操作全速和低速可以考虑OHCI。

问题:什么是USB controller?

USB 设备和主机的接口就是host controller,一个主机可以支持多个host controller,比如分别属于不同厂商的。USB host controller的作用:控制所有的USB设备的通信。

CPU把要做的事情分配给主机控制器,然后自己想干什么就干什么去,主机控制器替他去完成剩下的事情,事情办完了再通知CPU。否则让CPU去盯着每一个设备做每一件事情,那是不现实的。

控制器的主要工作是什么? 把数扔出去,把数拿回来。绝对不应该偷偷加工数据。

主机控制器控制总线上包的传输, 使用1ms或125us的帧。在每帧的开始时,主机控制器产生一个帧开始包(SOF: Start of Frame)。

SOF包用于同步帧的开始和跟踪帧的数目。包在帧中被传输,或由Host到Device(out事务),或由Device到Host(in事务)。传输总是由Host发起(轮询传输)。回此每条USB总线只能有一个Host。每个包的传输都有一个状态阶段同(同步传输除外),数据接收者可以在其中返回ACK(应答接收),NAK(重试),STALL(错误条件)或什么也没有(混乱数据阶段,设备不可用或已经断开)。

问题: 主机控制器Driver的工作是什么?

让主机控制器工作起来,发挥它的潜力。 让控制器发数据、收数据 。主机控制器主要包含以下几步:

- 按照主机控制器的要求组织结构体

- 将结构体在合适的时间、放在合适的地方

- trigger

- 等待完成信号

主机控制器Driver开发过程就是上面这几步。

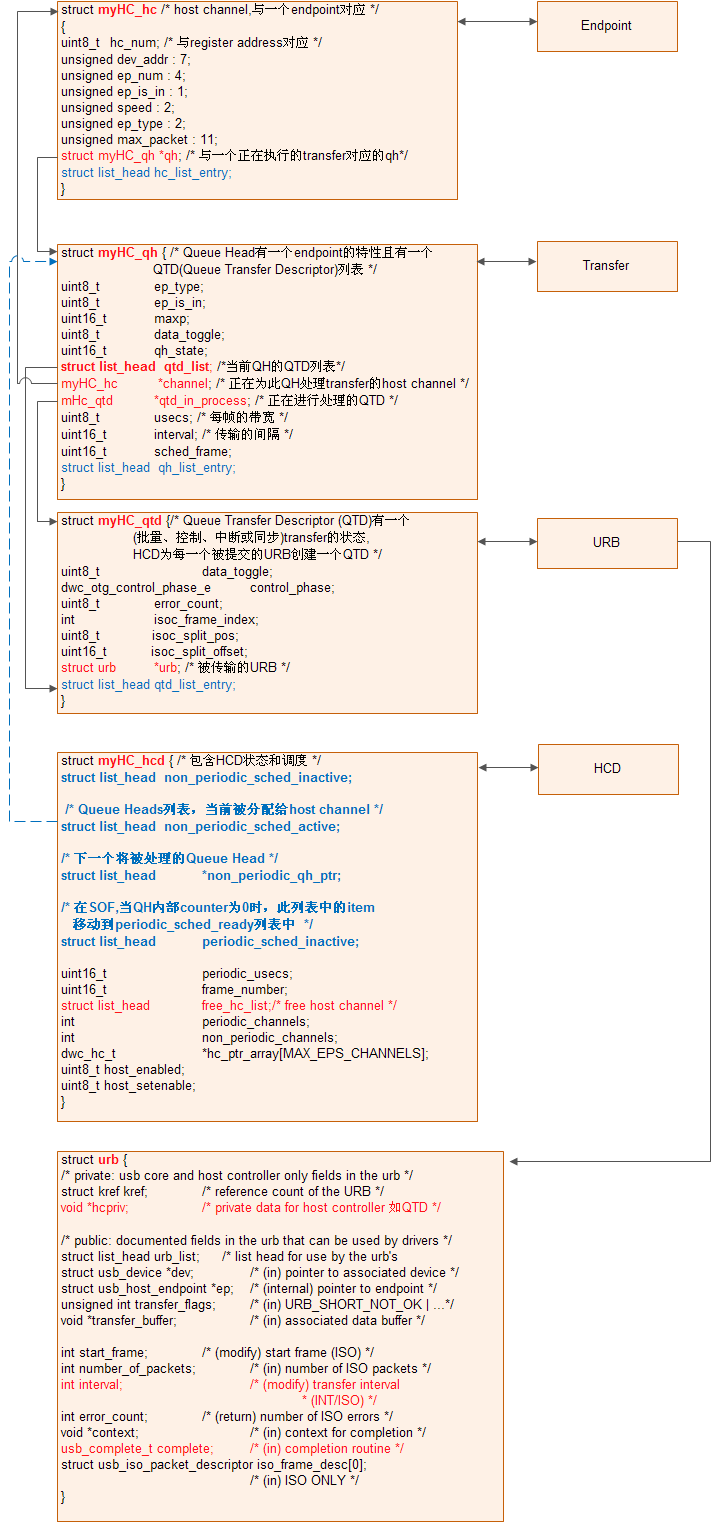

二、 关键数据结构

关键数据结构关系如下图所示:

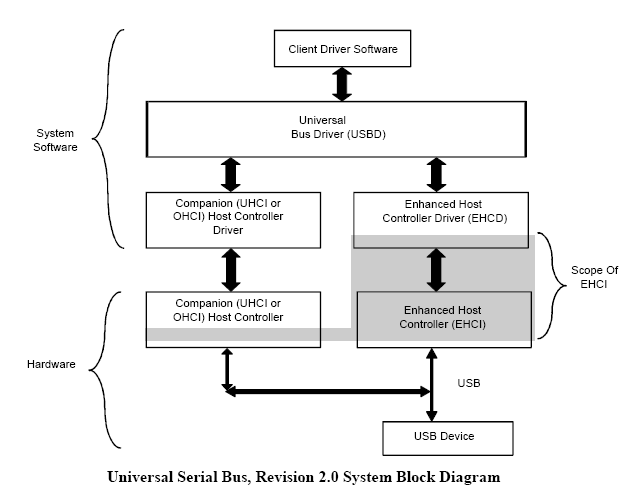

三、系统架构

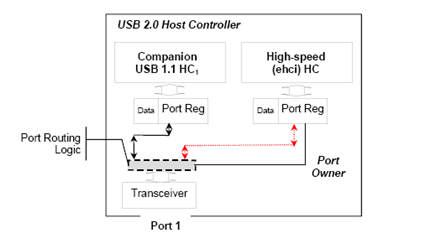

EHCI负责处理高速设备,OHCI负责处理全速/低速设备。上面这张图描述了USB控制器在route USB设备时的操作。

一个port 多个主人,OHCI的角色是companion,伴侣。地位低点。EHCI处理不了再给它处理。

关于端口逻辑这块需要特别注意,Driver设计者要注意:当前端口正在属于谁。当端口被OHCI所拥有时,你插入个高速设备怎么办?没办法!在没有插入设备时,就不应该让OHCI拥有这个端口。只有EHCI控制器才能识别出设备是全速、高速还是低速。

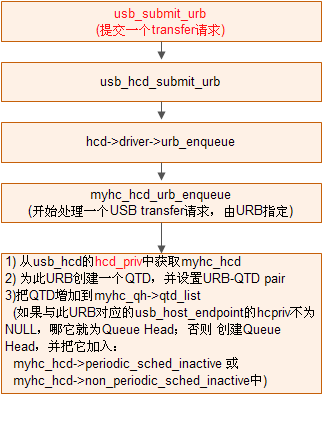

四、 usb_submit_urb

usb_submit_urb处理流程如下图所示:

本文介绍了USB主机控制器在USB设备通信中的重要角色,包括UHCI、OHCI和EHCI的区别和功能。EHCI主要处理高速设备,OHCI处理全速和低速设备。主机控制器驱动负责组织数据传输,并通过触发和等待完成信号来管理USB事务。此外,文章还提到了关键数据结构和usb_submit_urb处理流程。

本文介绍了USB主机控制器在USB设备通信中的重要角色,包括UHCI、OHCI和EHCI的区别和功能。EHCI主要处理高速设备,OHCI处理全速和低速设备。主机控制器驱动负责组织数据传输,并通过触发和等待完成信号来管理USB事务。此外,文章还提到了关键数据结构和usb_submit_urb处理流程。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?