一个能计数的电路必定需要触发器。

最简单:RS触发器

两个或非门构成

我们只考虑同一时间R和S仅有一个能输入1

当R按下时或门必然输出1,或非门必然输出0,Q必然为0

因为规定R、S不能同时输入1,R输入1时,S输入为0,Q和S都为0,经过或非门后QS为1

R

| R | S | Q | QS |

|---|---|---|---|

| 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 0(最后一次输入1的是R) | 0 | 0 | 1 |

| 0 | 0(最后一次输入1的是S) | 1 | 0 |

RS触发器的好处在于:输出端可以记忆最后一次置1的输入端是哪一个。(输入置零,输出不变;输入值1,输出刷新)。

2022/5/26 23:36 明日再学

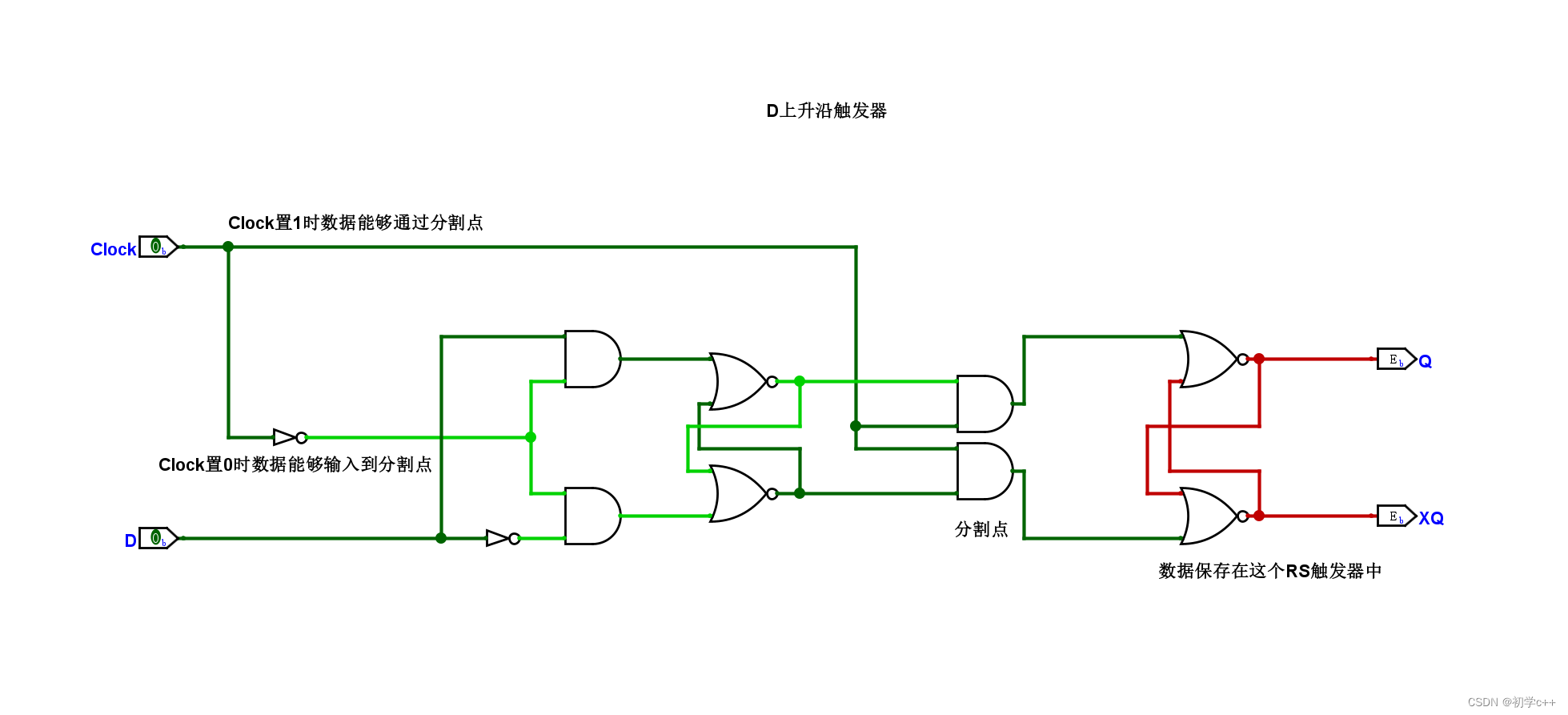

D型触发器

结构更复杂,使用更简单

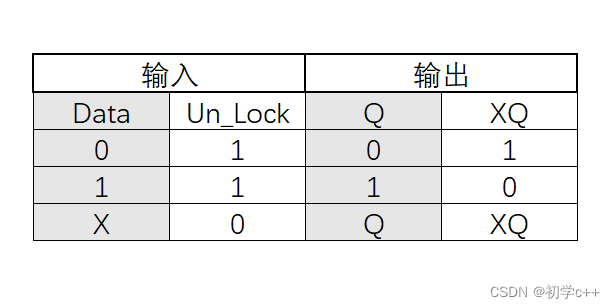

X表示(当Un_Lock为0时)输入不影响输出。

D型锁存器,是一个1bit存储器,它表示电路锁存住一位数据并保持,以便将来使用。

看看电路实现和效果(这与门很妙啊,有点修仙的玄妙感了。其实此时一个输出端口就够了)

这样一句C代码

bool love = true;

是否可以使用D型触发器保存love这个变量?

2022/5/27/ 23:00

这样一句C代码

char a=1+2+3;

要如何使用硬件实现呢?

我们有8bit加法器,但是它只能输入两个值进行运算,而不是三个。

所以我们第一次计算1+2的结果S12,保存到能够存储8bit数据的法阵中,

第二次计算将S12从缓存法阵中取出并+3,得到结果S123

实现8bit缓存法阵:8bit锁存器

char a = 10; 这样一条C语句意思是:把10(1010B)存入变量a,a是内存中的一个存储单元。

假设这个存储单元是8bit锁存器实现,存入过程可以是这样的。

(封装之后的样子)

很好!我感觉这个8bit锁存器很好用!

明天把8bit加法器和8bit锁存器组合成更强法阵,使得可以处理C语言中a+b+c+d这样的求多个数值相加的语句。

2022/5/28 0:10

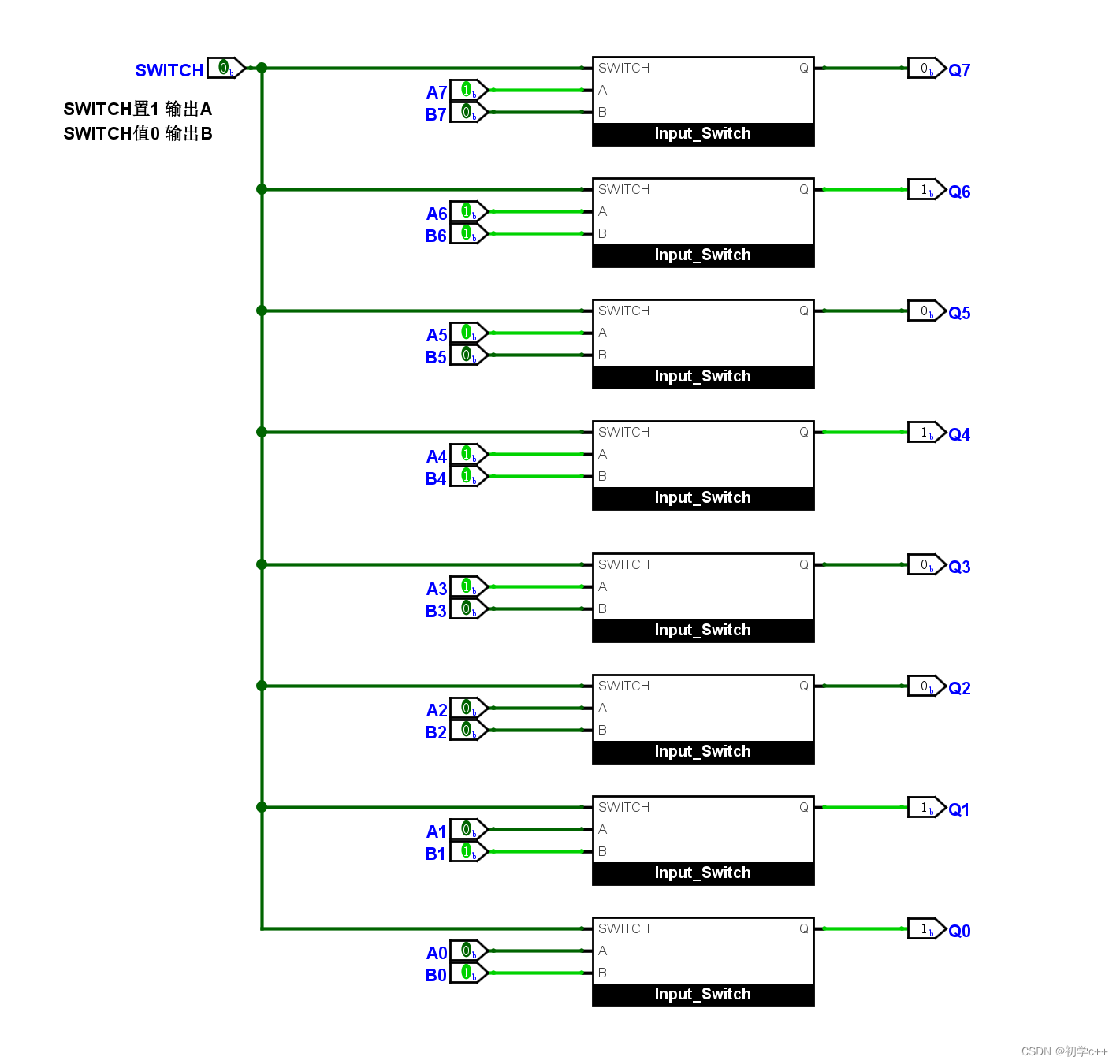

1bit 2-1信号选择器.

SWITCH起信号选择器的作用

当SWITCH置1时,选择信号A输出

当SWITCH置0时,选择信号B输出

两个输出可以等效为一个输出。

2022/5/28 中午 这个信号选择器马上就会只用到

8bit 2-1信号选择器

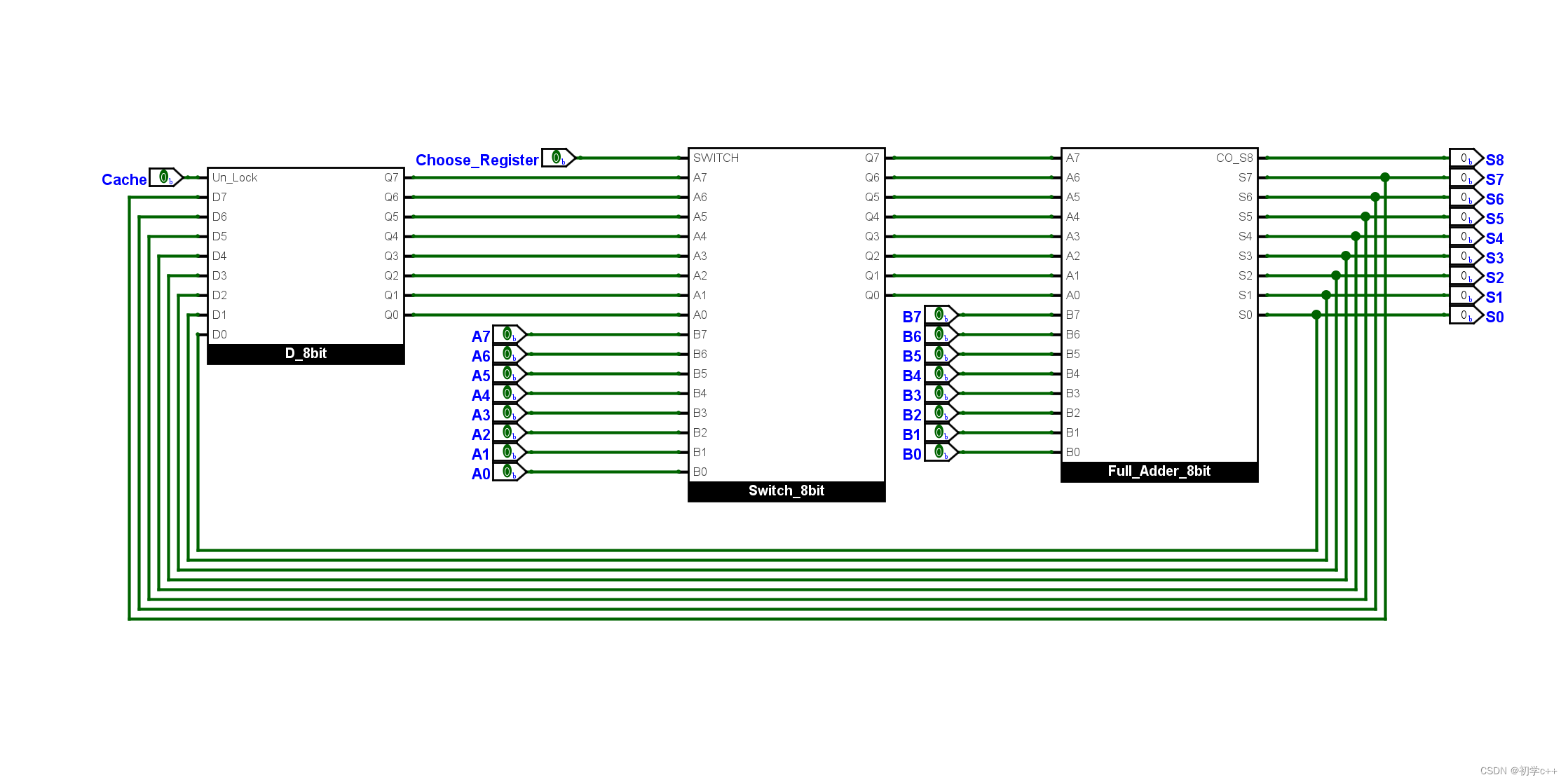

对于 a=1+2+3;这样一条C语句

需要8bit加法器做两次加法才能求得最终结果,第一次加法的结果在电路中没有保存的地方,我们得用人脑记住第一次的结果做为第二次加法的输入。

现在创建一个新的法阵完成a=1+2+3;中的加法,新法阵能够使用8bit锁存器保存第一次加法的和,

能够使用8bit 2-1选择器选择加法的输入来自于8bit锁存器或是输入端A。

演示1+2+3 (1B+10B+11B)

呃…有点bug,明天再搞…

2022/5/29 0:30

为什么会产生明显震荡?

Choose_Register和Cache同时值1时,Full_Adder_8bit的输出直接与输入向连接了:

加法器不停的将输出当作新的输入持续的做加法1+2,3+2,5+2,7+2,9+2…。这不是我们想要的结果。

解决方法:

将D_8bit这个锁存器中的D触发器升级为D边沿触发器。

用更新后的法阵完成1+2+3

OK啦,大功告成!

2022/5/30 0:34 睡觉

练气四要分P写了,还不想升级到练气五哦

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?