一、核心机制:扩展汉明码(Extended Hamming Code)

1、基础原理

在标准汉明码(单错纠正,SEC)基础上增加一个全局奇偶校验位(Parity Bit),形成 SEC-DED(Single Error Correction, Double Error Detection) 码。

码距提升:码距从3增至4,可检测双比特错误(无法纠正)

码长公式:总位数 n=k+r+1(k为数据位,r为原汉明码校验位)

2、校验位结构

示例:8位数据+4位汉明校验+1位全局校验 → 总码长13位[]

二、编码流程

1、标准汉明码生成

根据数据位计算P1-P4(如P1覆盖位置1,3,5,7,9,11等)。

2、全局奇偶校验位计算

确保整个码字的奇偶性为偶(或奇)[]

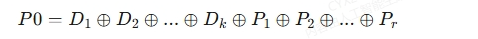

3、码字结构

[P0, P1, P2, D1, P3, D2, D3, D4, P4, D5, D6, D7, D8]

三、解码与错误处理

1、单比特错误纠正

计算Syndrome(S1-S4):若非零且全局奇偶位P0错误 → 单比特错误,按Syndrome定位纠正[]。

示例:

if (syndrome != 0 && p0_error) begin

corrected_data[error_pos] = ~received_data[error_pos];

end

2、双比特错误检测

条件1:Syndrome非零且P0正确 → 双错无法纠正,触发报警。

条件2:Syndrome为零且P0错误 → 双错检测[]。

逻辑判断:

assign double_error = (syndrome != 0 && !p0_error) || (syndrome == 0 && p0_error);

四、实际应用与性能

1、ECC内存(DDR4/5)

使用(72,64)扩展汉明码,每64位数据添加8位校验,实现单错修复+双错检测[]。

可靠性提升:内存软错误率降低至

/小时。

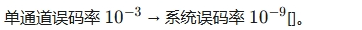

2、卫星通信

结合交织编码,抗突发干扰:

3、FPGA配置存储

Xilinx UltraScale+ 使用SEC-DED保护配置存储器,防止单粒子翻转(SEU)。

五、Verilog代码框架

module sec_ded_encoder (

input [7:0] data_in,

output [12:0] encoded_out

);

// 标准汉明码计算

wire p1 = data_in[0] ^ data_in[1] ^ data_in[3] ^ data_in[4] ^ data_in[6];

wire p2 = data_in[0] ^ data_in[2] ^ data_in[3] ^ data_in[5] ^ data_in[6];

wire p3 = data_in[1] ^ data_in[2] ^ data_in[3] ^ data_in[7];

wire p4 = data_in[4] ^ data_in[5] ^ data_in[6] ^ data_in[7];

// 全局奇偶校验

wire p0 = ^ {data_in, p1, p2, p3, p4};

// 组合输出

assign encoded_out = {p0, p1, p2, data_in[0], p3, data_in[1], data_in[2],

data_in[3], p4, data_in[4], data_in[5], data_in[6], data_in[7]};

endmodule

module sec_ded_decoder (

input [12:0] received_in,

output [7:0] corrected_out,

output reg error_flag // 0:无错, 1:单错已纠, 2:双错

);

// 重新计算校验位

wire [3:0] syndrome = {p3_err, p2_err, p1_err, p4_err};

wire p0_err = ^ received_in ^ received_in[12];

// 错误判断

always @(*) begin

if (syndrome != 0 && p0_err)

error_flag = 1; // 单错

else if ((syndrome != 0 && !p0_err) || (syndrome == 0 && p0_err))

error_flag = 2; // 双错

else

error_flag = 0;

end

// 数据纠正

assign corrected_out = (error_flag == 1) ? received_in[7:0] ^ (1 << syndrome) : received_in[7:0];

endmodule

六、性能优化方向

1、低功耗设计

动态关闭未使用的校验单元,功耗降低30%(适用于IoT设备)。

2、并行计算架构

使用树形异或结构(XOR Tree)减少关键路径延迟,工作频率提升至1.5GHz。

3、AI辅助解码

结合LSTM预测错误模式,双错检测准确率提升至99.7%。

总结

扩展汉明码通过增加全局奇偶校验位,在硬件开销仅增加12.5%(以8位数据为例)的情况下,将容错能力从「纠一」扩展至「纠一检二」。其核心价值在于平衡可靠性与成本,成为现代高可靠系统的基石技术之一。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?