实验内容:

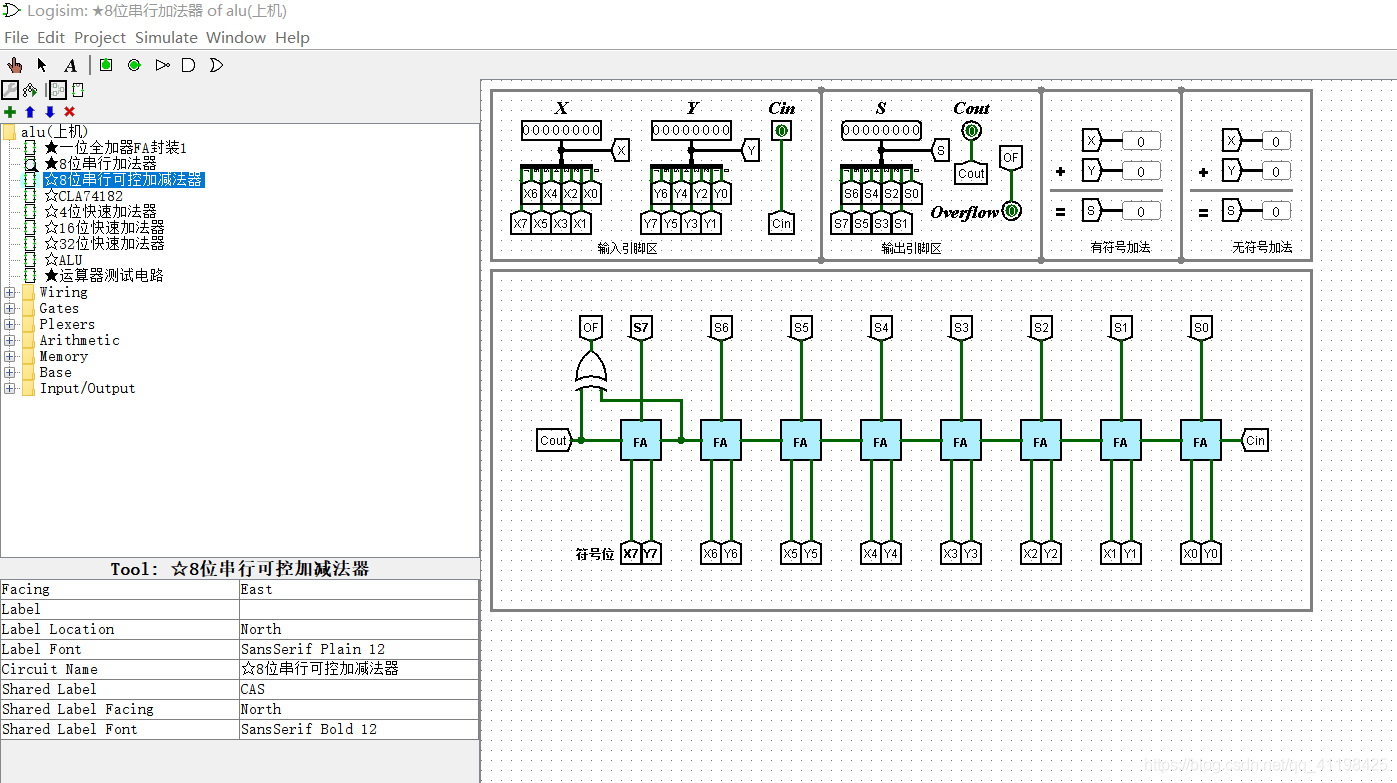

0. 八位串行加法电路设计

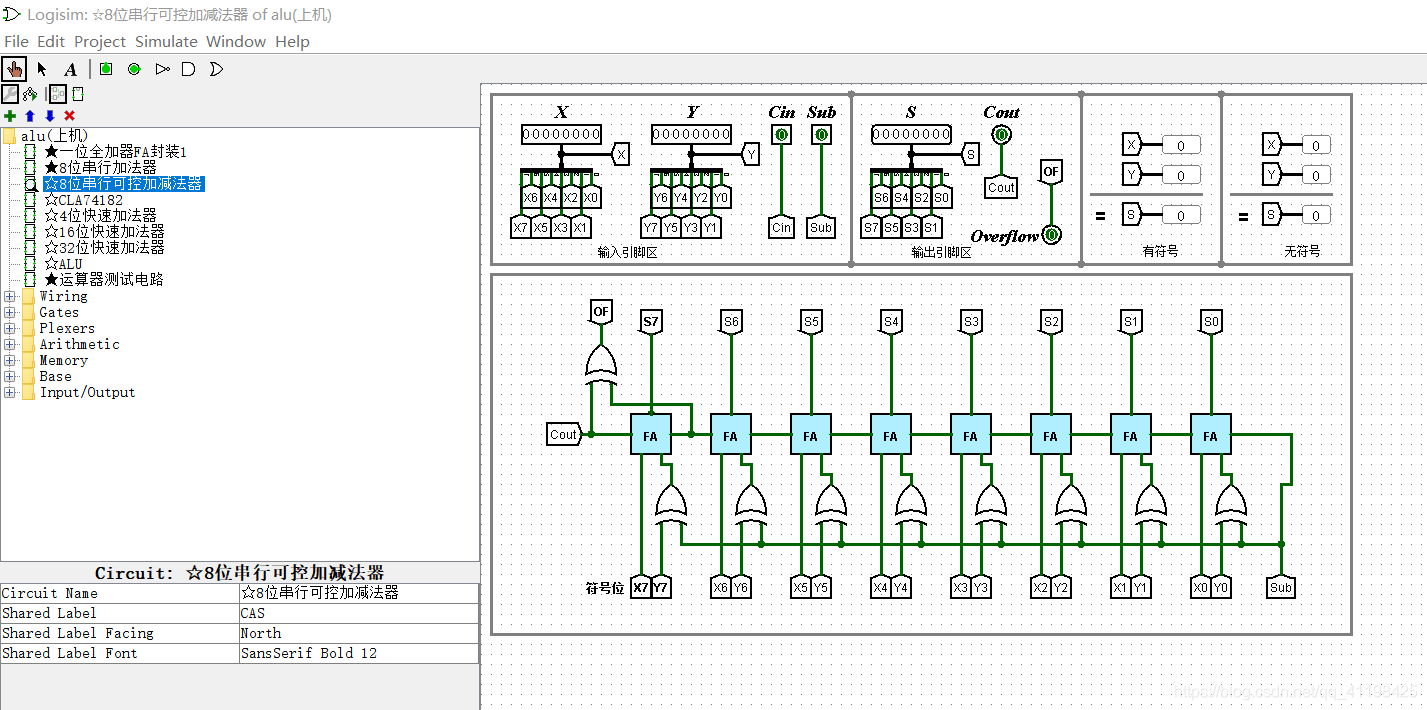

1.八位串行可控加减法法电路设计

利用已经封装好的全加器(封装 1)设计 8 位串行可控加减法电路

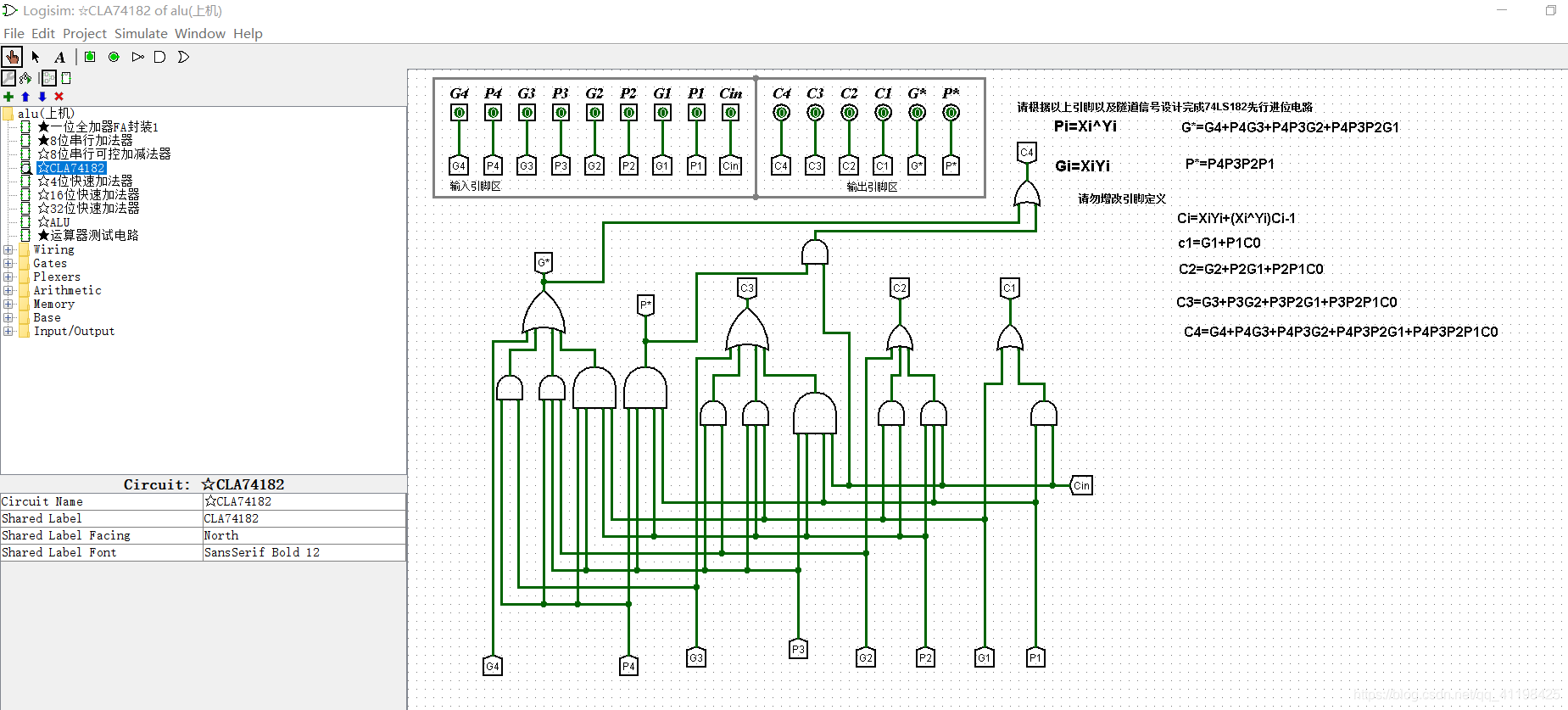

2. 四位先行进位电路

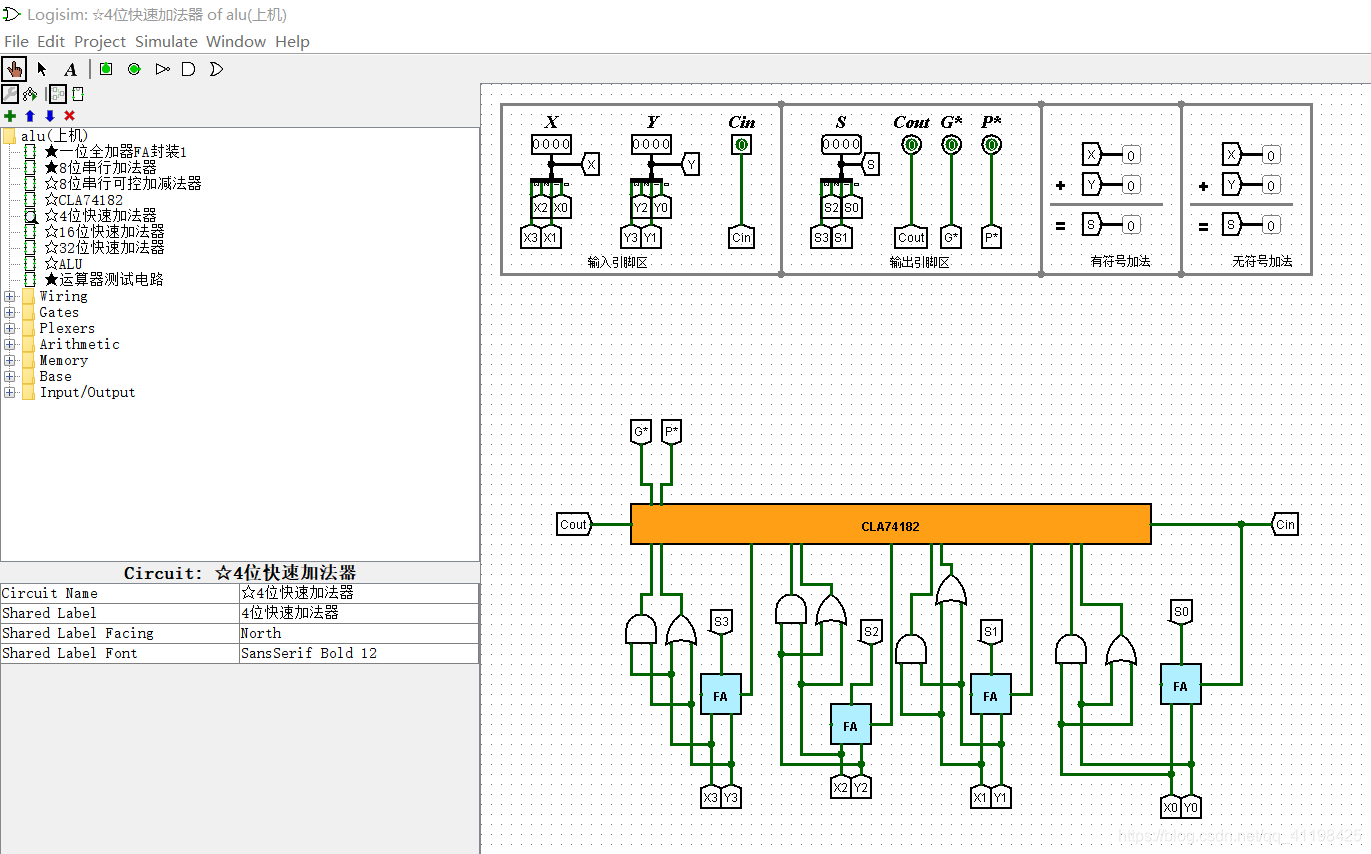

3.(1) 四位快速加法器设计

利用已经前一步设计好的四位先行进位电路构造四位快速加法器

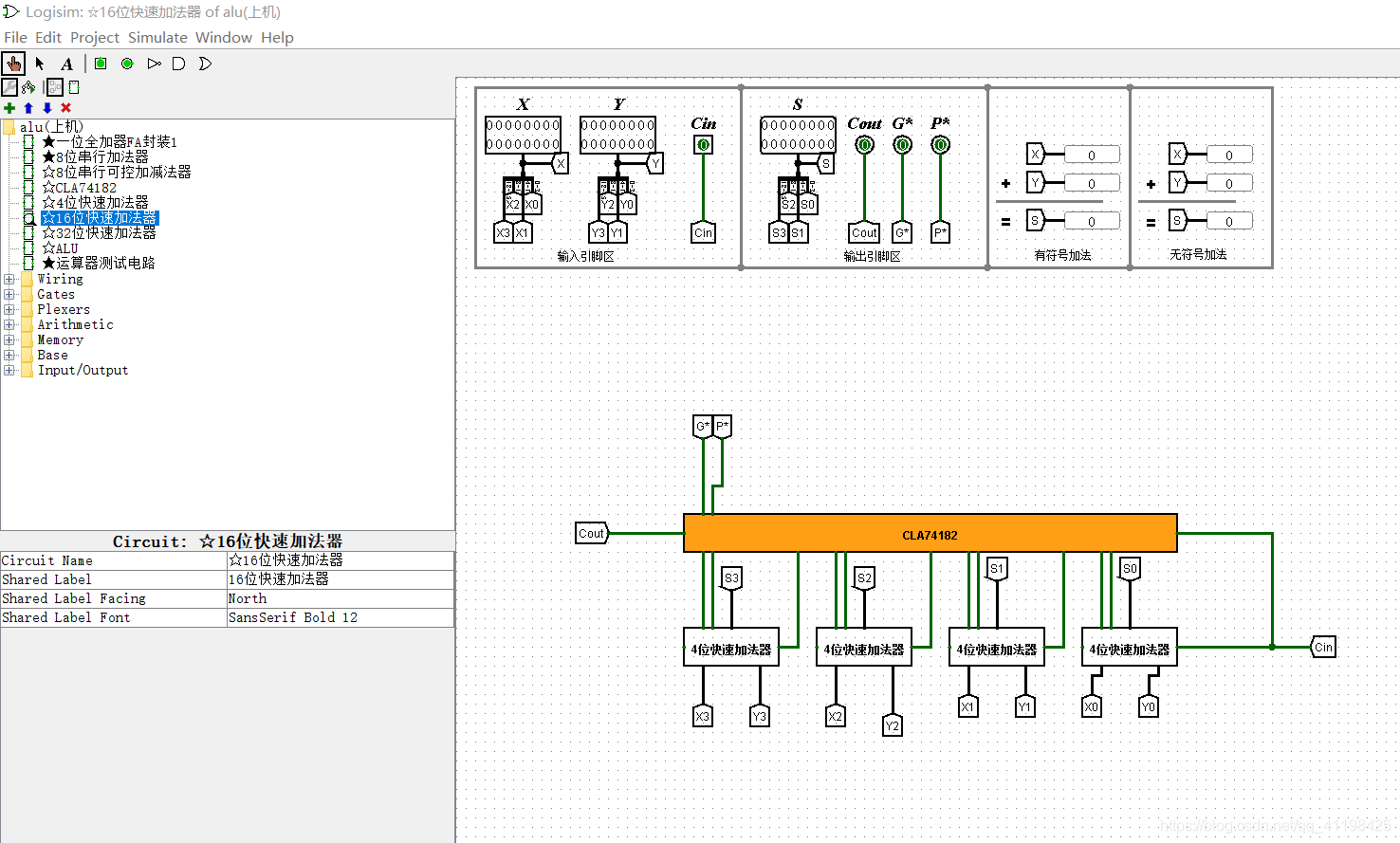

(2) 十六位快速加法器设计

利用四位先行进位电路和四位快速加法器构造十六位组间先行进位,组内先行进位快速加法器

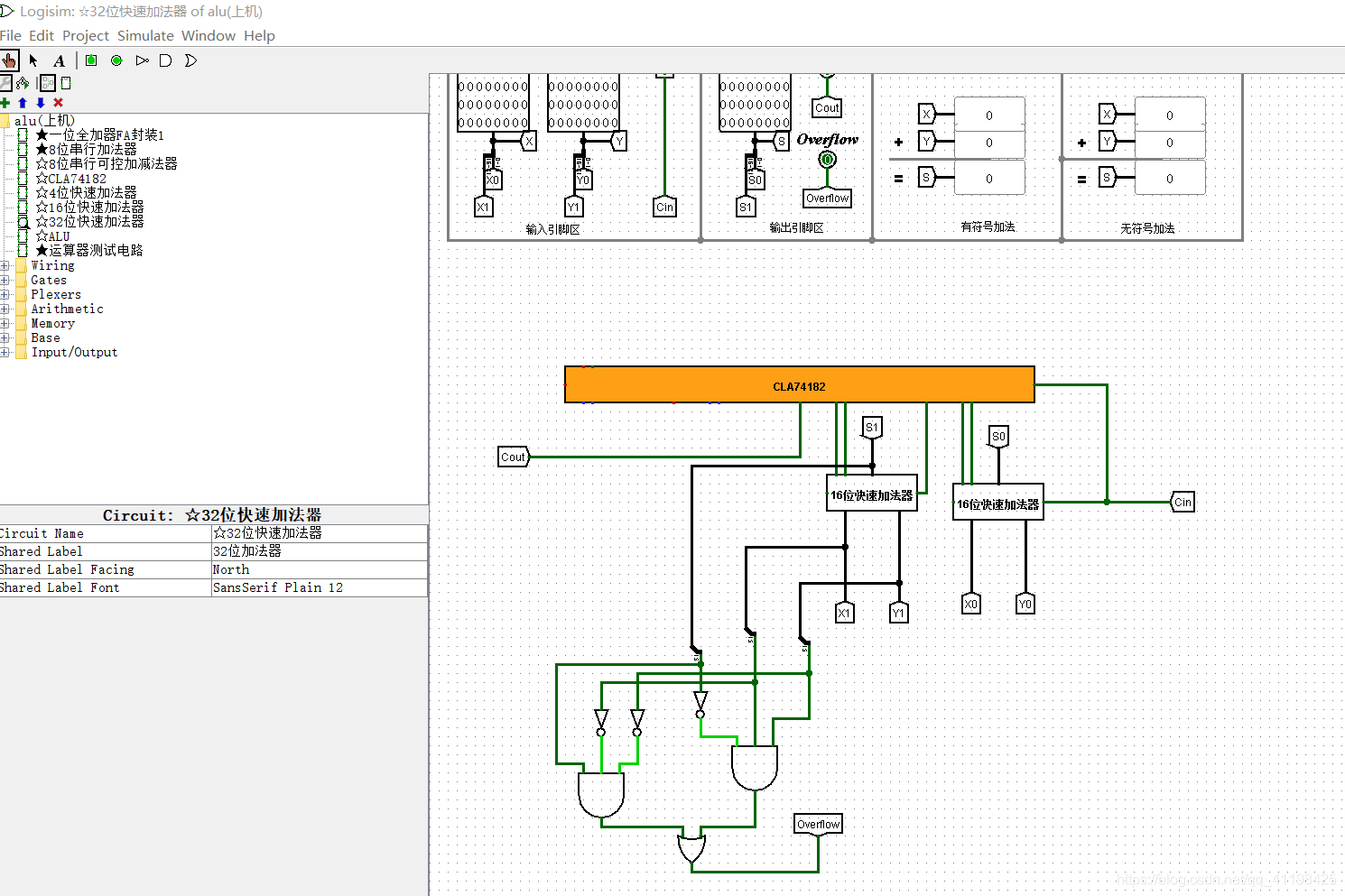

(3)32位快速加法器设计

利用前面构建的部件完成 32 位快速加法器,并分析其时间延迟

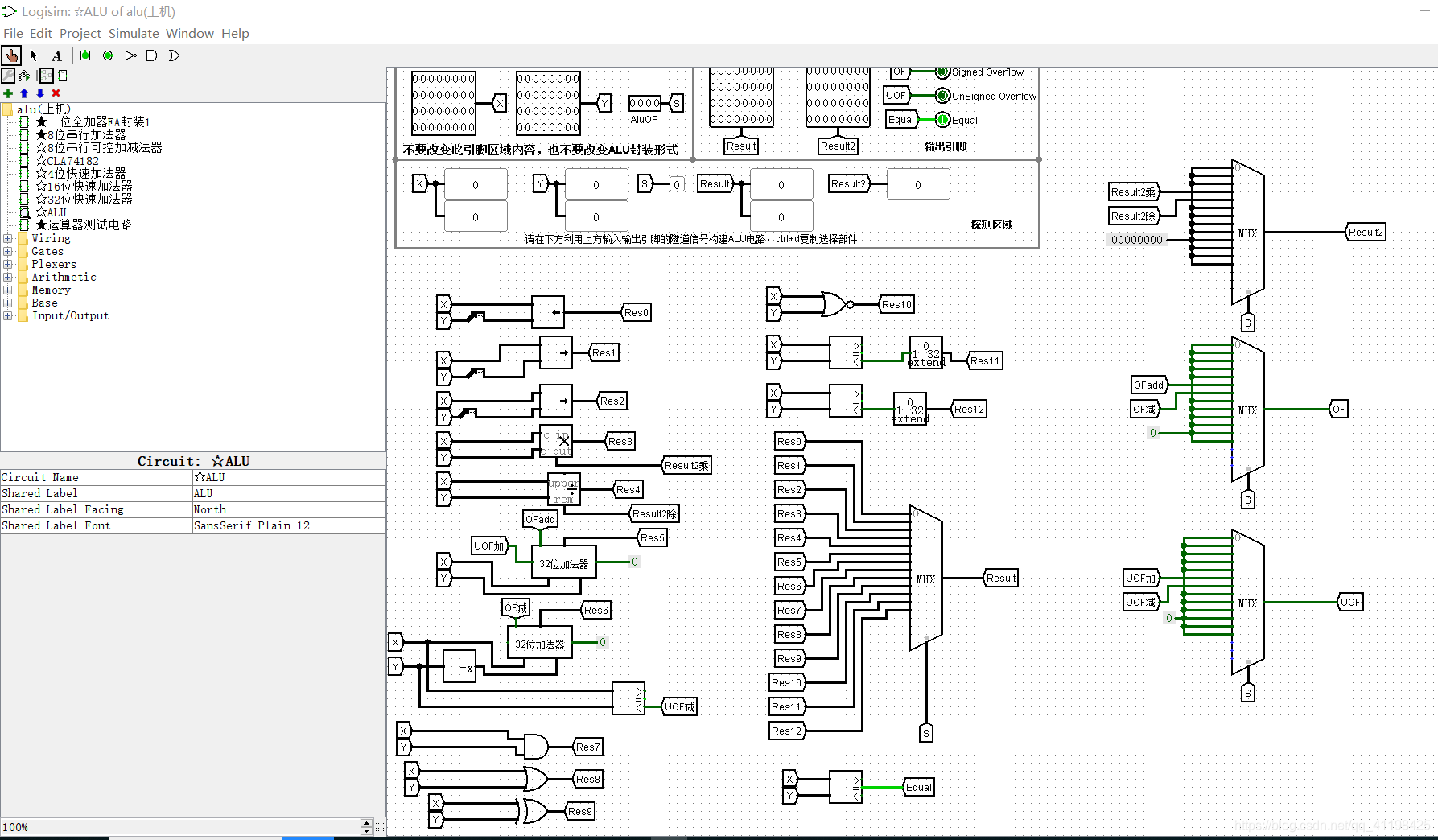

4. 32 位 MIPS 运算器设计

构建 32 位运算器。利用封装好的 32 位加法器以及 logisim 平台中现有运算部件(禁用系统自带的加法器,减法器)构建一个 32 位运算器,可支持算术加、减、乘、除,逻辑与、或、非、异或运算、逻辑左移、逻辑右移,算术右移运算,支持常用程序状态标志(有符号溢出 OF、无符号溢出 CF,结果相等 Equal),运算器功能以及输入输出引脚见下表,在主电路中详细测试自己封装的运算器,在报告中分析该运算器的优缺点。

本文详细介绍了一种32位MIPS运算器的设计与实现过程,包括八位串行加法电路、八位串行可控加减法电路、四位及十六位快速加法器的设计,以及32位快速加法器的时间延迟分析。进一步,文章深入探讨了如何使用这些部件构建一个支持多种算术与逻辑运算的32位运算器,同时分析了其优缺点。

本文详细介绍了一种32位MIPS运算器的设计与实现过程,包括八位串行加法电路、八位串行可控加减法电路、四位及十六位快速加法器的设计,以及32位快速加法器的时间延迟分析。进一步,文章深入探讨了如何使用这些部件构建一个支持多种算术与逻辑运算的32位运算器,同时分析了其优缺点。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?