本文主要介绍svf文件构造,一些简单的cpld的TAP状态,以及sir,tdi,tdo如何工作,以及如何对级联多链路cpld进行固件升级。更详细的TAP状态机,硬件设计,信号质量不在本文讨论范围内。

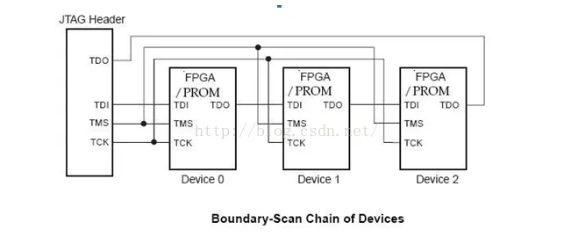

上图是一个串联cpld的线路拓扑结构,可以看到TDI和TDO串联,TMS和TCK并联的一种特殊结构。相信各位的硬件设计也是如此,如果采用的是TDI并联的模式,那么本文不适用。

看到这里,问题是我们如何把数据穿透第一个cpld器件,传递到下一个呢?在讨论工作原理之前,我们先看看安路提供是svf文件(虽然最终使用的是aje进行升级,但是svf文件可读性更高,所以看这个理解一下)

SVF文件内容

TRST OFF;

ENDIR IDLE;

ENDDR IDLE;

STATE RESET;

STATE IDLE;

FREQUENCY 1E6 HZ ;

TDR 1 TDI (0) ;

TIR 8 TDI (ff) ;

HDR 0 ;

HIR 0 ;

//Disable Dual boot loop.

SIR 8 TDI (80) ;

SDR 64 TDI (00800000000000a5) ;

RUNTEST 200 TCK ;

//Loading device with 'bypass' instruction.

SIR 8 TDI (ff) ;

SIR 8 TDI (ff) ;

//Loading device with 'idcode' instruction.

SIR 8 TDI (06) ;

RUNTEST 15 TCK ;

SDR 32 TDI (00000000) TDO (03004C37) MASK (FFFFFFFF) ;

//Loading device with 'refresh' instruction.

SIR 8 TDI (01) ;

//Loading device with 'bypass' & 'spi_program' instruction.

SIR 8 TDI (FF) ;

SIR 8 TDI (39) ;

RUNTEST 50000 TCK ;

这是是一个尾部cpld的svf文件,可以看到开头这几十行,存在若干的指令,主要是SIR为主,可以看到安路cpld的SIR指令宽度是8bit。

同时也发现存在TDR,TIR,HDR,HIR这些指令,这些指令就是拿来提示这个文件是用来升级头部或尾部的器件用的,没有这个东西也可以,但是指令长度不只是8了,而是8 * 器件数量。jtag规范使用这些指令是为了简化文件,否则svf文件就会像下面这样

TDR 0 ;

TIR 0 ;

HDR 0;

HIR 0;

//Disable Dual boot loop.

SIR 16 TDI (80FF) ;

SDR 65 TDI (0010000000000014A) ;

RUNTEST 200 TCK ;

//Loading device with 'bypass' instruction.

SIR 16 TDI (FFFF) ;

SIR 16 TDI (FFFF) ;

//Loading device with 'idcode' instruction.

SIR 16 TDI (06FF) ;

RUNTEST 15 TCK ;

SDR 33 TDI (000000000) TDO (00600986E) MASK (1FFFFFFFE) ;

//Loading device with 'refresh' instruction.

SIR 16 TDI (01FF) ;

//Loading device with 'bypass' & 'spi_program' instruction.

SIR 16 TDI (FFFF) ;

SIR 16 TDI (39FF) ;

可以看到,这里SIR指令长度16bit,所以有两个cpld器件。一般升级都是用携带TDR,TIR,HDR,HIR的svf文件。

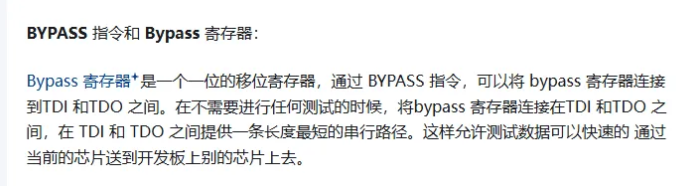

BYPASS模式

在上面的svf文件中,我们可以发现出现很多次的bypass指令,这个指令是干什么的呢

//Loading device with 'bypass' instruction.

SIR 8 TDI (ff) ;

SIR 8 TDI (ff) ;

通过查看JTAG IEEE 1149.1协议标准,可以看到对bypass指令及寄存器的介绍:

</

</

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

235

235

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?