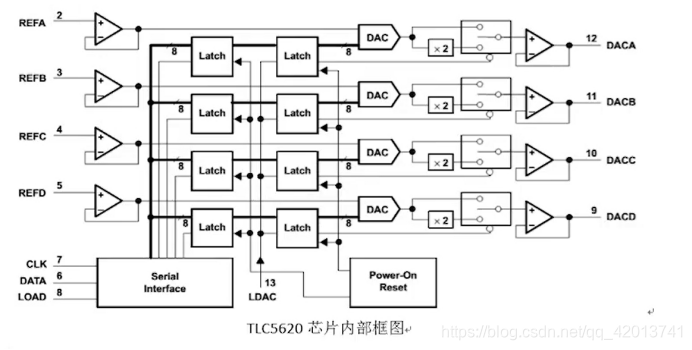

用TLC5620芯片,TLC5620内部有4个DAC,全部都是8位电压输出型。每个DAC有一个高输入阻抗的参考电压输入端口,每个DAC可以输出一倍或者两倍的参考电压与GND之间的电压值。

TLC5620接受11位数据,2位的DAC选择位,8位的数据位,1位的电压倍增控制位。

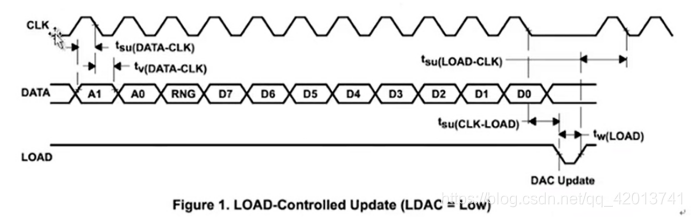

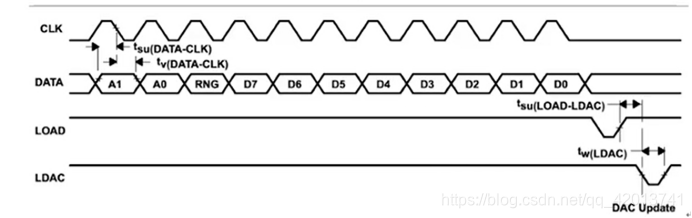

先有load控制将信号存储到latch中,再由ldac控制,将存储的信号交由DAC输出。clk是位串行接口时钟,每个时钟的下降沿,输入数字总线上的数据被移入内部的接口寄存器中。只有当ldac由高电平变为低电平时,数据才会跟新到DAC上。当ldac为低电平时,load的下降沿将带输出数据所存到输出锁存器并立即产生输出电压。每个DAC通道的输出可由下列公式计算得出:

Vo(DAC|A|B|C|D)=REFCODE/256(1+RNG bit value)

两种输出方式如下:

A0A1两位指定了被选中的DAC,00为DACA,01为DACB,10为DACC,11为DACD。

基于FPGA的dac控制

最新推荐文章于 2025-03-13 17:26:05 发布

本文介绍了如何使用FPGA控制TLC5620芯片进行8位电压输出型DAC的操作,详细阐述了信号传输过程和时序控制,并通过计数器实现DAC输出。在遇到问题后,对代码进行了调整,最终达到预期的仿真波形。

本文介绍了如何使用FPGA控制TLC5620芯片进行8位电压输出型DAC的操作,详细阐述了信号传输过程和时序控制,并通过计数器实现DAC输出。在遇到问题后,对代码进行了调整,最终达到预期的仿真波形。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2951

2951

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?