Support for Internal Clock Control

可以使用测试过程文件中的时钟控制定义来指定捕获周期期间片上/内部时钟的操作。时钟控制定义是测试程序文件中的一个或多个块,其通过指定源时钟和扫描单元输出处的条件来定义内部时钟操作。ATPG解释这些定义,并确定在捕获周期中脉冲哪个时钟以检测最多的故障。

当定义时钟控制时,时钟控制位被包括在链测试模式中,以在受控时钟没有源时钟时或者在受控时钟中定义的源时钟是始终脉冲时钟时关闭捕获时钟。

默认情况下,在ATPG工具中,如果没有always脉冲时钟,或者脉冲始终时钟既不驱动观察点也不驱动总线,则链测试模式中包含一个捕获周期。

可以手动创建时钟控制定义,或使用stil2mgc工具从包含ClockStructures块的STIL过程文件(SPF)自动生成时钟控制定义。

要指定明确的启动/捕获序列或外部/内部时钟关系定义,必须使用命名捕获程序(NCP)。

Per-Cycle Clock Control

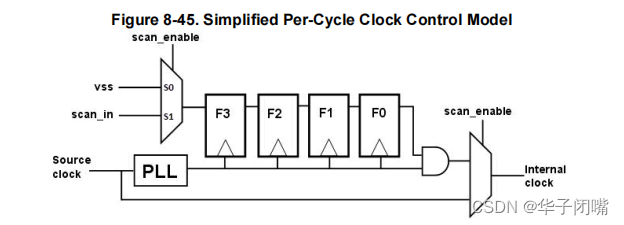

Per-cycle时钟控制允许您使用扫描单元值基于单个捕获周期定义内部时钟输出。Per-cycle时钟控制通常用于基于流水线的时钟生成,其中一位控制Per-cycle的时钟。

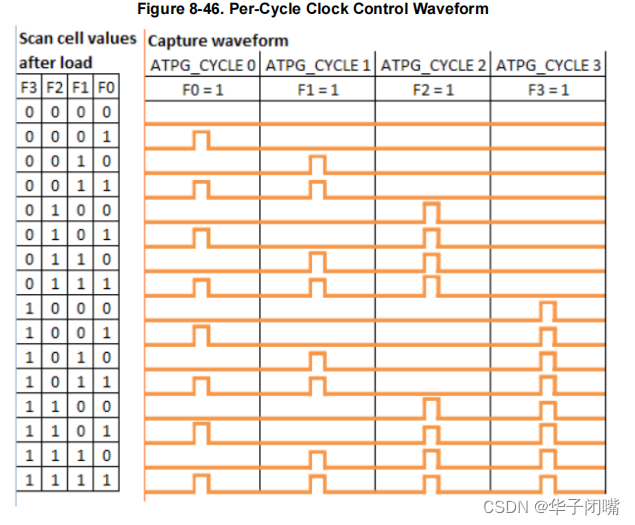

移位寄存器(F3-F2-F1-F0)上的值确定“与”门是否在每个周期(在该电路中为4个周期)通过时钟。这个电路中的所有触发器都是扫描触发器。在扫描链移动结束时,扫描单元被初始化为一个值。该值决定电路可以产生的时钟数。

该电路中的硬件被定义为,基于四个扫描单元的值,电路可以提供多达四个捕获周期。如下图所示

Using “ATPG_CYCLE” you can represent the above circuit and waveforms as follows:

// Define clock control for internal clock “/clk_ctrl/int_clk1”

CLOCK_CONTROL /clk_ctrl/int_clk1 =

// Define a source clock if one exists

SOURCE_CLOCK ref_clk;

// Define specific local conditions

ATPG_CYCLE 0 =

CONDITION /clk_ctrl/F0/q 1;

END;

ATPG_CYCLE 1 =

CONDITION /clk_ctrl/F1/q 1;

END;

ATPG_CYCLE 2 =

CONDITION /clk_ctrl/F2/q 1;

END;

ATPG_CYCLE 3 =

CONDITION /clk_ctrl/F3/q 1;

END

END;

Sequence Clock Control

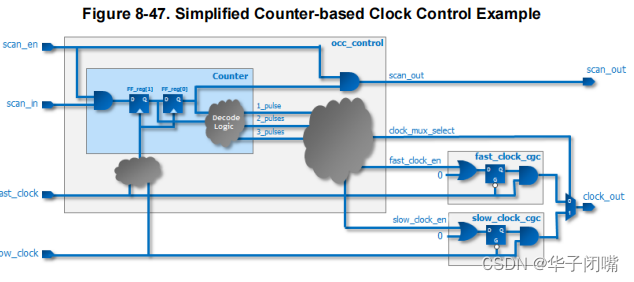

Sequence时钟控制允许您使用扫描单元值根据捕获周期序列定义内部时钟输出。Sequence时钟控制通常用于基于counter-based

时钟生成电路。

组合如下图8-48

在这种情况下,加载到OCC触发器中的值确定连续时钟脉冲的数量。可以生成三种不同的序列:一个时钟脉冲、两个时钟脉冲和三个时钟脉冲。

ATPG_SEQUENCE描述如下:

// Define clock control for internal clock “/clk_ctrl/int_clk1”

CLOCK_CONTROL /clk_ctrl/int_clk1 =

// Define a source clock if one exists

SOURCE_CLOCK ref_clk;

// Define specific local conditions

ATPG_SEQUENCE 0 0 = // ‘0 0’ is a 1 clock pulse sequence

CONDITION /clk_ctrl/FF_reg[1]/q 0;

本文介绍了Mentor DFT工具中关于内部时钟控制和松弛计算的概念。通过示例解释了如何用'ATPG_CYCLE'表示电路和波形,并讨论了源时钟类型对捕获周期的影响。此外,还探讨了延迟测试覆盖率(DTC)的计算方法,它是衡量测试模式质量的指标,与静态和动态松弛相关。

本文介绍了Mentor DFT工具中关于内部时钟控制和松弛计算的概念。通过示例解释了如何用'ATPG_CYCLE'表示电路和波形,并讨论了源时钟类型对捕获周期的影响。此外,还探讨了延迟测试覆盖率(DTC)的计算方法,它是衡量测试模式质量的指标,与静态和动态松弛相关。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?