设计任务及方案论证

方案一:采用计数器(74LS192)作为核心部分。同时选择(74LS47)作为BCD码译码器来对7段数码显示管进行译码驱动,两个七段共阳数码显示管进行显示。采用计时器(NE555)制成的多谐振荡器,进行秒脉冲的输入。因为我们需要对其进行暂停、清零、报警和自动清零等控制,所以我们使用了三个开关来控制计数器的各功能的实现,从而实现各种功能。

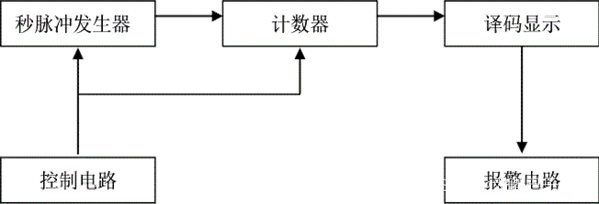

方案二:秒信号产生电路由定时器(NE555)构成的多谐振荡器和(74LS90)构成的分频器构成,为计数电路提供计数秒脉冲。攻方24秒倒计时,当比赛准备开始时,屏幕上显示24秒字样,当比赛开始后,倒计时从24逐秒倒数到00。这一计时模块主要是利用双向计数器(74LS192)来实现;控制电路主要利用SR锁存器的锁存功能。当计数器计时到零时,警报电路给出发光提示和提示音。这部分电路主要通过一些门电路来实现。

设计原理

通过计数器(74LS192)进行24秒倒计时,经过译码器(74LS47)译码,在共阳数码管上显示出来。

方案描述

系统组成:该系统的控制电路由74LS192芯片和74LS47芯片组成组成,外围电路由NE555多谢振荡电路电路、独立按键、数码管、蜂鸣器组成,达到24秒计时器的要求。

本文详细介绍了两种24秒倒计时计时器的设计方案。方案一利用74LS192计数器和74LS47译码器驱动共阳数码显示管,结合NE555定时器实现秒脉冲。方案二则通过74LS90分频器和双向计数器74LS192,结合SR锁存器进行控制。计时结束时,系统通过门电路触发报警提示。设计方案涵盖了电路原理、数码显示和计时进制等方面,适用于电子工程和数字系统设计的学习与实践。

本文详细介绍了两种24秒倒计时计时器的设计方案。方案一利用74LS192计数器和74LS47译码器驱动共阳数码显示管,结合NE555定时器实现秒脉冲。方案二则通过74LS90分频器和双向计数器74LS192,结合SR锁存器进行控制。计时结束时,系统通过门电路触发报警提示。设计方案涵盖了电路原理、数码显示和计时进制等方面,适用于电子工程和数字系统设计的学习与实践。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?