Intel Kaby Lake Microarchitecture

这部分内容主要来自于Wikipedia/Wikichip。

Kaby Lake微架构是Intel Skylake Client微架构的继任者,面向与主流的桌面和移动设备。Kaby Lake是Intel PAO模式的第一个“Optimization”版本,本质上是Skylake微架构的优化版本。

注:Intel PAO模式, Intel在2016年发布了新的处理器版本发布模式,即Process-Architecture-Optimization模式,用来取代先前的Tick-Tock模型。下面这个路线图来自于Wikichip,最终可能会有变化。

| Intel PAO Roadmap | |||

| Cycle | Introduction | Microarchitecture | |

| Process | 2014 | ||

| Architecture | 2015 | ||

| Optimization | 2016 | ||

| Optimization | 2017 | ||

| Optimization | 2018 | ||

| Optimization | 2018 | ||

| Optimization | 2019 | ||

| Process | 2018 | ||

| Architecture | 2019 | ||

| Optimization | 2020 | ||

| Optimization | 2021 | ||

| Optimization | 2021 | ||

CPUID signature

下表是Keby Lake微架构的CPUID签名,可以看出这代微架构的DisplayFamily_DisplayModel是06_8EH和06_9EH.

https://en.wikichip.org/wiki/intel/microarchitectures/kaby_lake#CPUID

| Core | Extended | Family | Extended | Model |

| 0 | 0x6 | 0x8 | 0xE | |

| Family 6 Model 142 (8E) | ||||

| 0 | 0x6 | 0x9 | 0xE | |

| Family 6 Model 158 (9E) | ||||

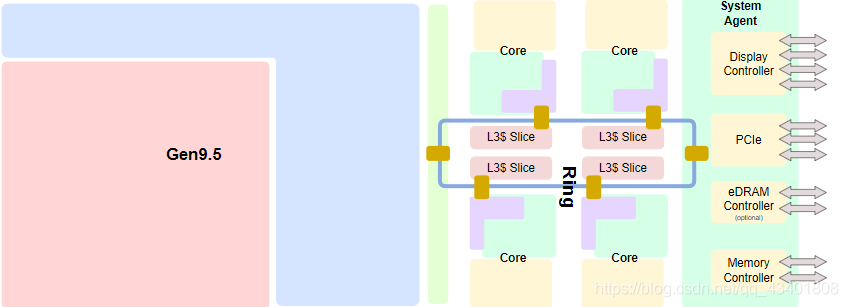

下图是一个基于Kaby Lake的4核处理器的功能框图。从图中可以看到图形处理单元Gen9.5,4个处理器核,L3缓存(通过环相连),最右侧的System Agent中包含了显示控制器,PCIe接口,eDRAM控制器和内存控制器。

Key Changes from Skylake microarchitecture

TODO: https://en.wikichip.org/wiki/intel/microarchitectures/kaby_lake

KabyLake作为IntelSkylake微架构的优化版本,标志着IntelPAO模式的开始。它是面向主流桌面和移动设备的处理器,继承了Skylake的特性并进行优化。本文详细介绍了KabyLake微架构的发展历程,包括其CPUID签名和关键变化。

KabyLake作为IntelSkylake微架构的优化版本,标志着IntelPAO模式的开始。它是面向主流桌面和移动设备的处理器,继承了Skylake的特性并进行优化。本文详细介绍了KabyLake微架构的发展历程,包括其CPUID签名和关键变化。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?