1.方法一:异或实现

module d3(

input clk,

input reset,

output div_three

);

reg [1:0] cnt=2'b00;

reg div_clk1;

reg div_clk2;

always @(posedge clk or negedge reset)begin

if(reset == 1'b0)begin

cnt <= 0;

end

else if(cnt == 2)

cnt <= 0;

else begin

cnt <= cnt + 1;

end

end

always @(posedge clk or negedge reset)begin

if(reset == 1'b0)begin

div_clk1 <= 0;

end

else if(cnt == 0)begin

div_clk1 <= ~div_clk1;

end

else

div_clk1 <= div_clk1;

end

always @(negedge clk or negedge reset)begin

if(reset == 1'b0)begin

div_clk2 <= 0;

end

else if(cnt == 2)begin //注意:此处cnt==1的话可以实现占空比为1/6的波形

div_clk2 <= ~div_clk2;

end

else

div_clk2 <= div_clk2;

end

assign div_three = div_clk2 ^ div_clk1;//相同为0,相异为1.

a1:assert property( //SVA断言语句

@(posedge clk)

div_three ##2(!div_three));//断言

endmodule

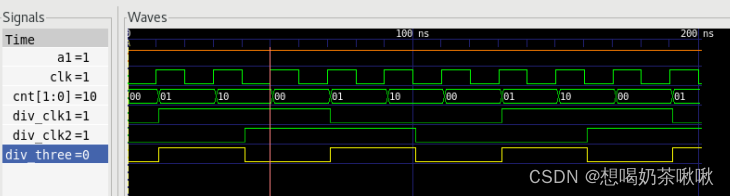

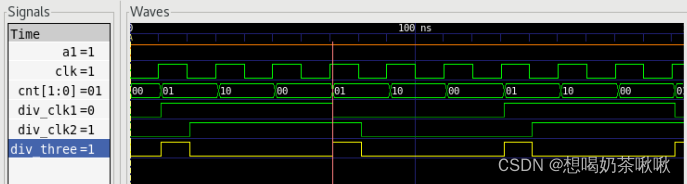

我用的是我们公司的EDA软件,不用写testbench就可以查看波形:

上图为cnt==2的波形,

上图为cnt==1时的波形,可以说是占空比为1/6,也可以说是5/6。

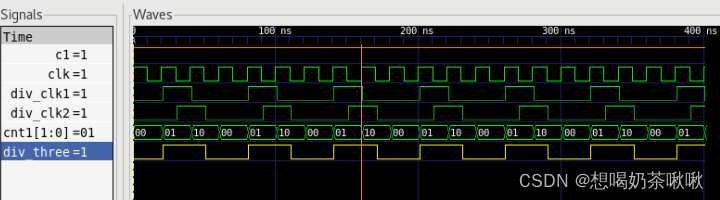

2.方法二:或实现

module d3(

input clk,

input reset,

output div_three

);

reg [1:0] cnt1=2'd0;

reg div_clk1;

reg div_clk2;

always @(posedge clk or negedge reset)begin

if(reset == 1'b0)begin

cnt1 <= 0;

end

else if(cnt1 == 2)

cnt1 <= 0;

else begin

cnt1 <= cnt1 + 1;

end

end

always @(posedge clk)begin

if(reset == 1'b0)begin

div_clk1 <= 0;

end

else if(cnt1 == 0)

div_clk1 <= ~div_clk1;

else if(cnt1== 1)

div_clk1 <= ~div_clk1;

else

div_clk1 <= div_clk1;

end

always @(negedge clk)begin

if(reset == 1'b0)

div_clk2 <= 0;

else if(cnt1 == 1)

div_clk2 <= ~div_clk2;

else if(cnt1==2) //注意计数值选择

div_clk2 <= ~div_clk2;

else

div_clk2 <= div_clk2;

end

assign div_three = (div_clk2 | div_clk1);//或运算

c1:cover property(

@(posedge clk)

div_three |=>(!div_three));

endmodule

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?