目录

hspice仿真Verilog-a,放大器。例如:输入5V电压,要求输出放大5倍

hspice仿真Verilog-a,放大器。例如:输入5V电压,要求输出放大5倍

1 新建一个名为 .va 文件,例如:amp_5x.va 。编辑文本,添加以下Verilog-a代码:

注:文件名称必须和model名称相同

`include "constants.vams" // 包含标准常量定义

`include "disciplines.vams" // 包含电学域定义

module amp_5x(in, out); // 模块名:amp_5x,端口:in(输入)、out(输出)

input in; // 声明输入端口

output out; // 声明输出端口

electrical in, out; // 定义端口为电学节点

parameter real gain = 5; // 可选:定义增益参数(默认值5)

analog begin

// 核心公式:输出电压 = 输入电压 × 增益

V(out) <+ gain * V(in); // 使用 <+ 表示连续时间赋值

end

endmodule

2 新建一个sp网表,调用amp_5x.va模块,例如:test_amp_5x.sp,并添加以下代码:

* Inverter Circuit

.hdl amp_5x.va

.OPTION POST

* 输入信号:1V正弦波(频率1kHz)

* Vin in 0 SIN(0 1 1k)

VS in 0 PWL (

+ 0.0n 0

+ 30.0n 0

+ 30.2n 5

+ 45.0n 5

+ 45.2n 0

+ 60.0n 0

+ 60.2n 5

+ 75.0n 5

+ 75.2n 0

+ 90.0n 0)

* 调用放大器模型

X1 in out amp_5x // X<实例名> <输入节点> <输出节点> <模型名>

* 输出负载电阻(可选)

Rload out 0 1k

* 瞬态仿真:0~2ms,步长1us

.tran 0.2n 100n 0 0.1n

* 输出波形

.print V(in) V(out)

* 关闭仿真

.end

3 打开hspice软件仿真

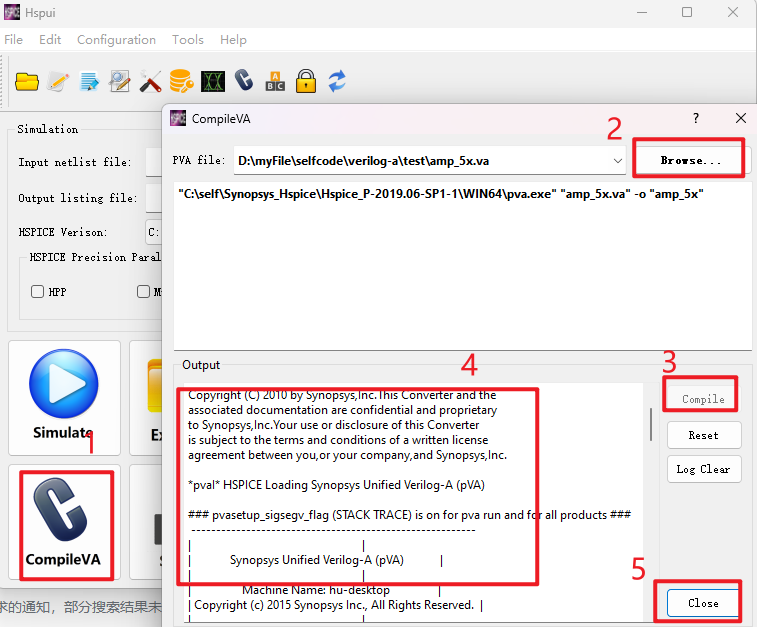

3.1 编译Verilog代码,查看是否存在错误(可以跳过)

点击CompileVA → 点击Browse选择要相应的.va文件 → 点击 Compile → 查看是否存在错误 → Close。

注:编译后会生成amp_5x.pvadir文件夹,通过pvaCG.log文件可以查看编译结果,存在错误时,需要修改代码,重复步骤3.1

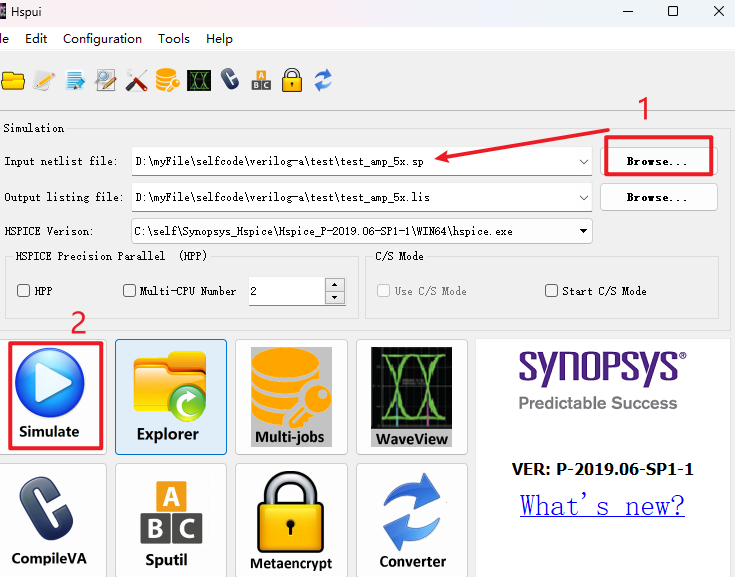

3.2 仿真verilog

回到Hspui界面,点击Browse,选择test_amp_5x.sp文件,点击Simulate

注:点击Simulate仿真结束后,弹出的对话框会自动消失,同时会生成 .lis .st0 .tr0 .pa0等文件。若只有.lis 文件表明存在错误,可以打开 .lis文件 查看错误原因,修改代码,重复步骤3.2。

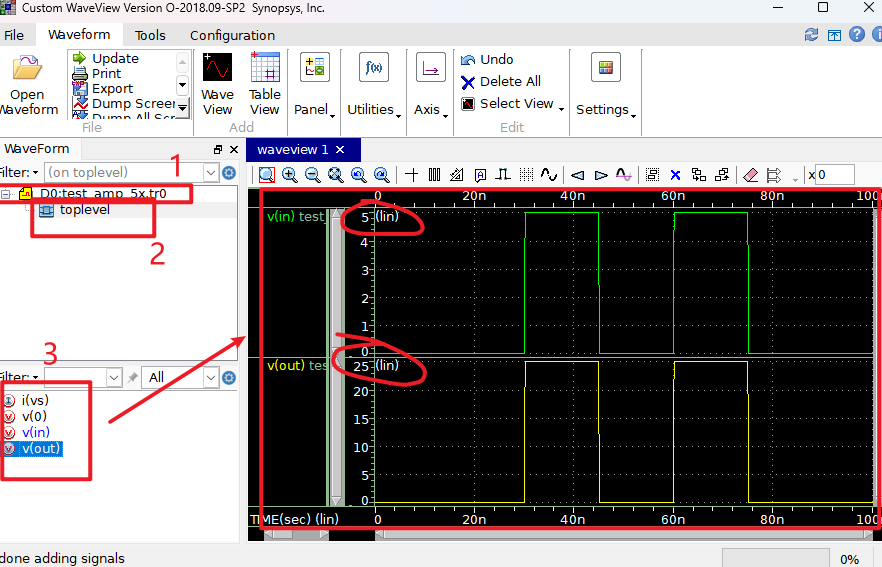

3.3 查看结果波形

在步骤3.2之后,直接点击WaveView![]() ,弹出WaveView框并自动显示test_amp_5x.tr0文件,点击test_amp_5x.tr0→toplevel,双击对应波形名称即可查看波形。

,弹出WaveView框并自动显示test_amp_5x.tr0文件,点击test_amp_5x.tr0→toplevel,双击对应波形名称即可查看波形。

Verilog-a数组赋值注意事项

`include "constants.vams" // 包含标准常量定义

`include "disciplines.vams" // 包含电学域定义

module t111(in, out); // 模块名:amp_5x,端口:in(输入)、out(输出)

input in; // 输入端口

output out; // 输出端口

electrical in, out;

real numer[0:2] = {1, 0.2, 0.3}; // 分子(默认值1)

real denom[0:2] = {1, -1}; // 分母(默认值1)

real gain = 1; // 增益(默认值1)

real ic = 0; // 初始条件(默认值0)

real zero[0:2] = {0, 0, 0};

analog begin

// 传递函数:H(s) = gain / s (积分器)

// 使用 Laplace变换实现,多项式系数由低到高排列

numer = {2, 2, 2}; // 此赋值方式错误,赋值后numer结果为[0.00, 1.00, 0.00]

$display("numer0: %.2f, numer1:%.2f, numer2: %.2f", numer[0],numer[1],numer[2]);

numer[0] = 3; numer[1] = 3; numer[2] = 3; // 此赋值方式正确,赋值后numer结果为[3.00, 3.00, 3.00]

$display("numer0: %f, numer1:%f, numer2: %f", numer[0],numer[1],numer[2]);

numer = zero; // 此赋值方式正确,赋值后numer结果为[10.00, 10.20, 10.30]

$display("numer0: %f, numer1:%f, numer2: %f", numer[0],numer[1],numer[2]);

// denom[0:2] = {1.0, 0.0, 0.0};

V(out) <+ zi_nd(V(in), numer, denom, 0.2e-9);

end

endmodule

更多Verilog-A表达式可以参考:

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?