Vivado2019.1仿真FIFO ip,存储255个数据再读出。

1:fifo ip核复位信号rst=只能为高电平有效

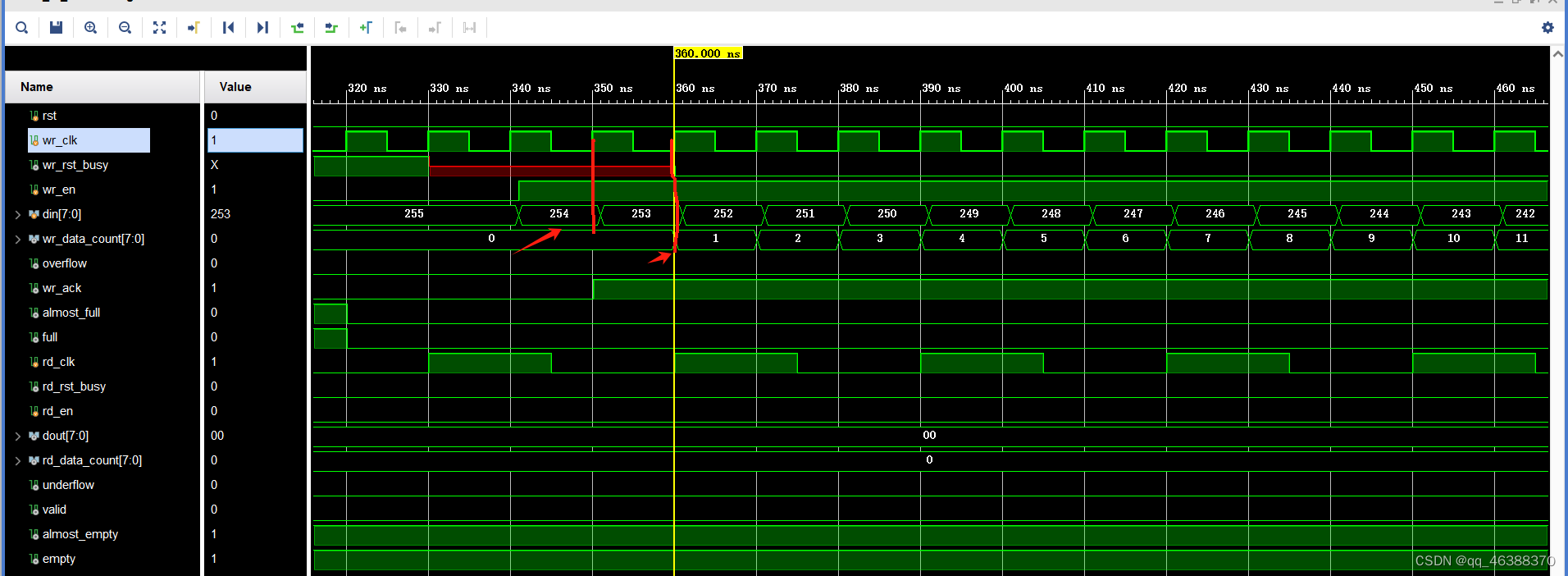

2:wr_data_count延迟写入数据一个周期

3:wr_rst_busy信号出现不定态是正常的,信号会被正常读取

仿真FIFO时,wr_rst_busy信号出现未知态的原因

http://www.corecourse.cn/forum.php?mod=viewthread&tid=29541

(出处: 芯路恒电子技术论坛)

4:almost_full相对full提前一个周期

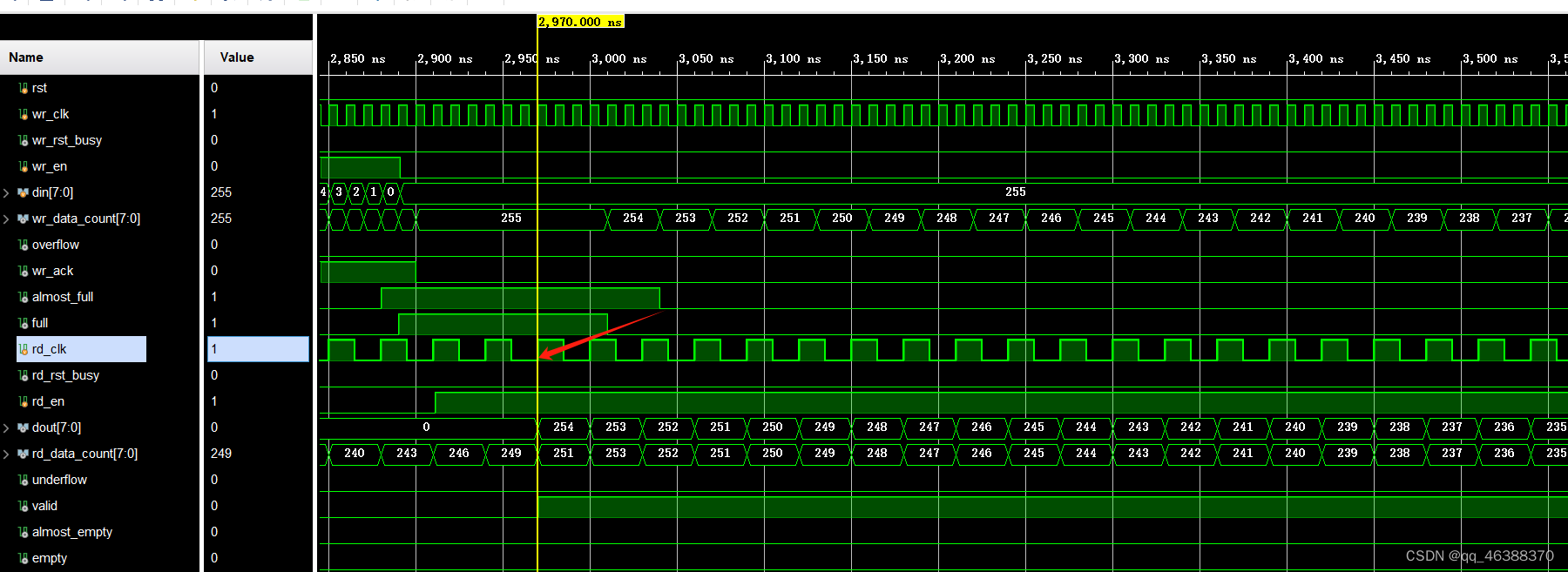

5:读出的数据和valid信号延迟rd_en一个周期

6:almost_empty提前empty一个周期

FWFT功能会将FIFO的有效深度增加两个读取字。

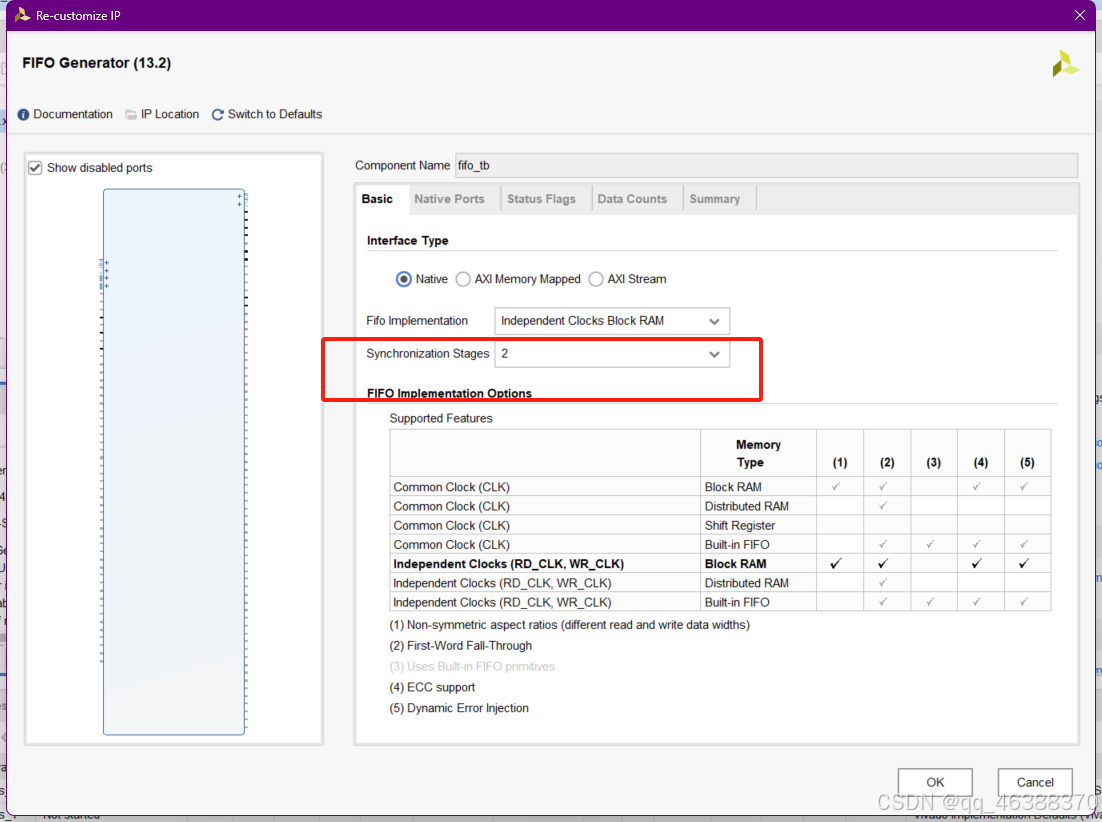

syncgornization stages:异步fifo跨时钟域时的同步阶数,即缓冲2个时钟周期进行同步

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?