本栏博客目录

软考-软件设计师 笔记一(计算机组成与体系结构)

软考-软件设计师 笔记二(操作系统基本原理)

软考-软件设计师 笔记三(数据库系统)

软考-软件设计师 笔记四(计算机网络)

软考-软件设计师 笔记五(系统安全分析与设计)

软考-软件设计师 笔记六(数据结构与算法基础)

软考-软件设计师 笔记七(程序设计语言与语言处理程序基础)

软考-软件设计师 笔记八(法律法规)

软考-软件设计师 笔记九(多媒体基础)

软考-软件设计师 笔记十(软件工程)

软考-软件设计师 笔记十一(面向对象设计)

软考-软件设计师 笔记十二(数据流图)

软考-软件设计师 笔记十三(数据库设计)

软考-软件设计师 笔记十四(UML建模)

软考-软件设计师 笔记十五(数据结构及算法应用)

软考-软件设计师 笔记十六(面向对象程序设计)

文章目录

浅谈软设备考

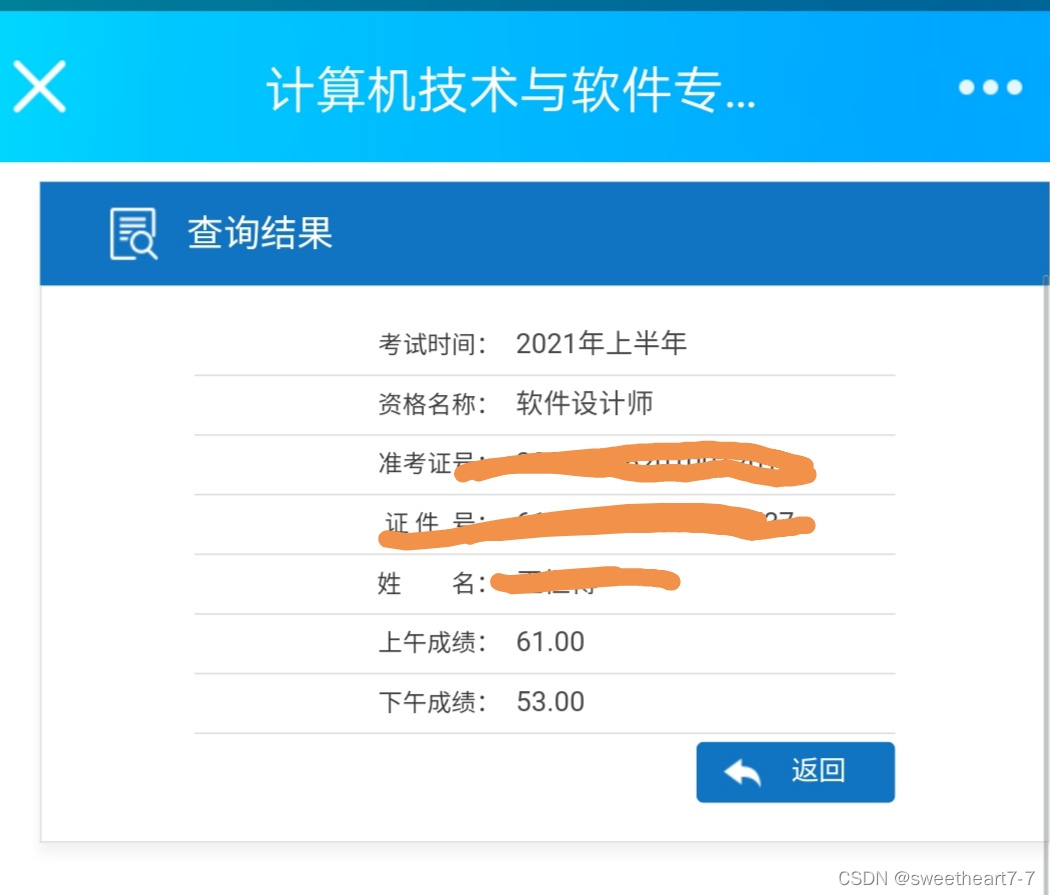

软设一般需要上午下午各 45+ (包括 45)即可获得证书,证书如下图,总体来说,对科班出身的人,难度不大(甚至可以说比较简单)(当然非科班的也不要慌,只要认真学,问题不大!),但是广度还是比较可以滴,涉及各种专业课的基础知识(可以查看上面的目录),建议考证时间为大二下,大三上(因为这个时候已经学完了大部分课程)。blog 主是大二下和同学一起考的(我两都过了),没学过的专业课也不要怕,软设专业课知识考的还是比较浅滴!你跟着 b 站那些老师学一遍(推荐希赛网的软设视频),然后对应刷题就行了!

注意:刷题很重要!!!

对于书是否需要购买,可以看个人情况(我没买,感觉视频 + 刷题就够了),刷题的话推荐几个 app:希赛网,软考通,软考真题(在应用商店下载即可,记得进去把科目选成 软考中级 - 软设)

刷题的话建议反复刷,把错的地方记录下来,抽时间复习!!!

重要的事情说三遍:

刷题很重要!

刷题很重要!

刷题很重要!

上午题把正确率稳到 45/75 就差不多了!下午题相对容易,总结套路,然后多刷几套题,把它拿捏了(狗头)

最后祝大家顺利拿证!!!

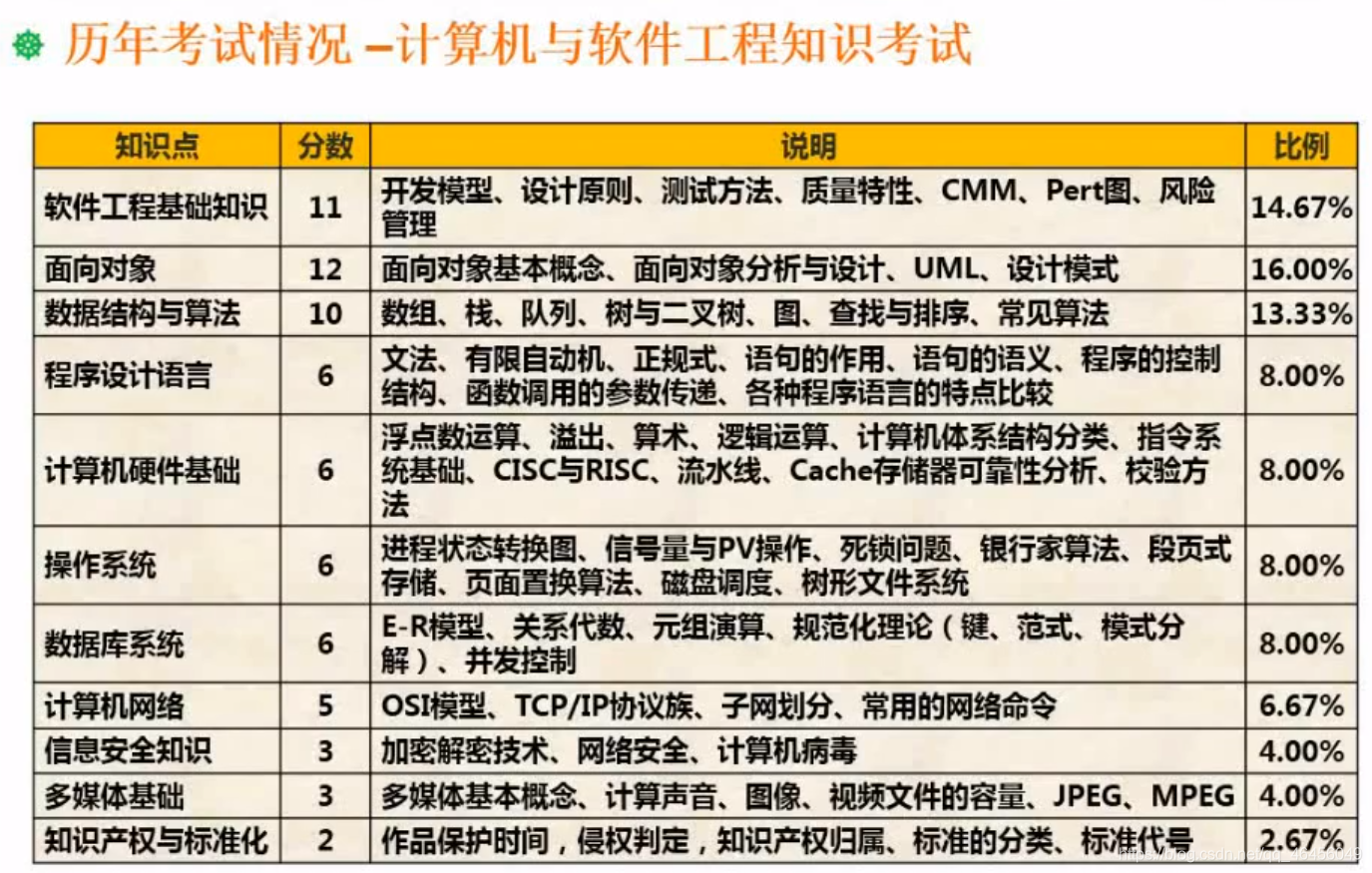

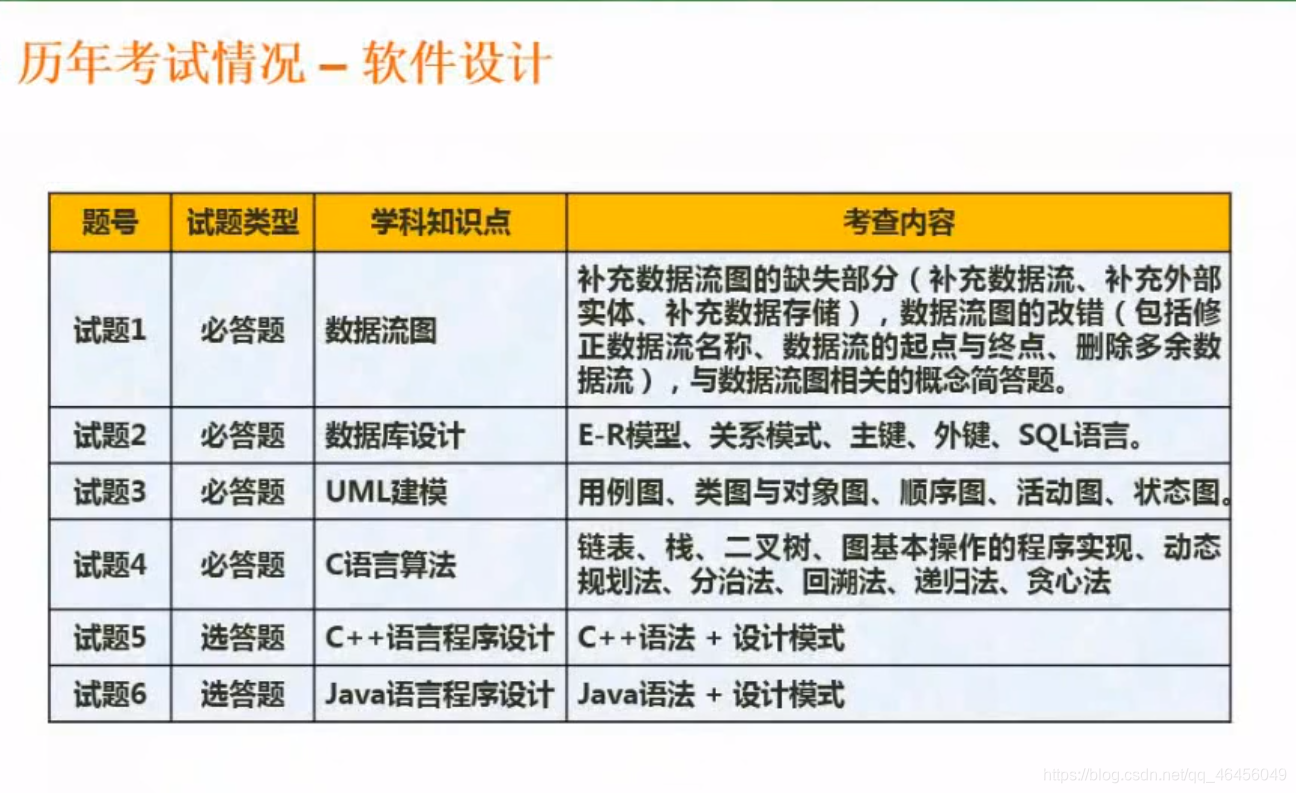

历年分值分布情况

数据的表示

进制的转换

X进制转十进制 : 按权展开

例如: 七进制转十进制: 604.01 = 6 * 72 + 4 * 70 + 1 * 7 -2

十进制转R进制 : 整数位短除法逆序,小数点后乘二取整正序

二进制转八进制与十六进制 : 从小数点处向两边,3位为一位 / 4位为一位转换,不够则补零

原码反码补码移码

原码: 二进制形式,一般为一个字节(八位),最高位为符号位,正的符号位为0,负数的符号位1.

反码: 正数的跟原码一样,负数的反码除符号位外取反。

补码: 正数的跟原码一样,负数的补码为反码 + 1。

移码: 作浮点运算的介码,不管是正数还是负数,都在补码的基础上对符号位取反。

数值的表示范围

n为位数

原码: - (2 (n - 1) - 1) ~ (2 (n - 1) - 1)

反码: - (2 (n - 1) - 1) ~ (2 (n - 1) - 1)

补码: - 2 (n - 1) ~ (2 (n - 1) - 1)

补码的表示范围多一个是因为 +0 和 -0 的补码相同,少占用一个编码。

浮点数运算

浮点数表示:

N = M * Re

M称为尾数,e是指数,R为基数

对阶 =》 尾数计算 =》 结果格式化

对阶: 让指数相同(阶数化大),M化小

格式化: 1~9

计算机结构

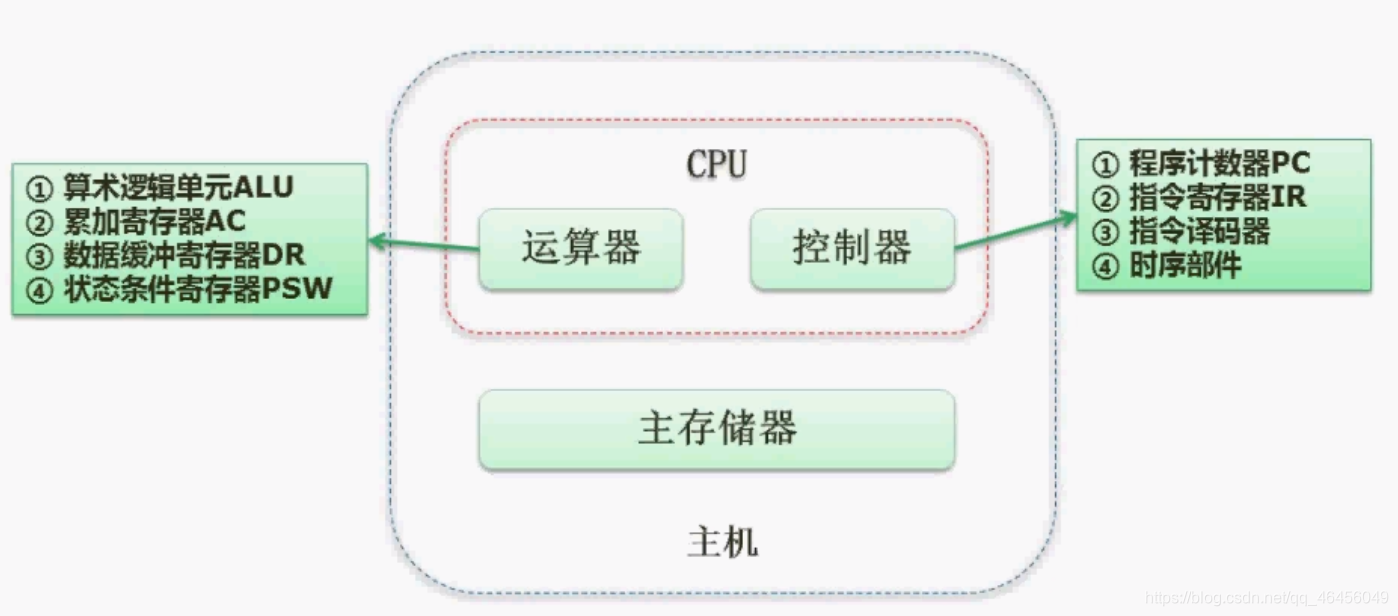

CPU结构(运算器与控制器的组成)

算术逻辑单元ALU: 跟运算相关

累加寄存器AC: 通用寄存器,运算的过程中存一些需要运算的值,不仅是加法,减法也要用到AC这样的寄存器

数据缓冲寄存器DR: 对内存储器进行读写操作的时候,用来暂存数据的寄存器

状态条件寄存器PSW: 用来存储在运算的过程中,相关的标志位(进位,溢出,中断…),涉及到一些状态的信息需要保存。

程序计数器PC: 我们在进行程序运行的时候运行了当前指令之后要运行下一条指令,我们需要了解下一条指令在什么位置,这就是由PC来完成的。

指令寄存器IR

指令译码器

时序部件

指令相关的往往与控制器的部件相关

Flynn分类法

指令对应控制部分,数据流对应处理器。

一种计算机体系结构的分类方法 ,根据flynn分类法,我们可以把常见的计算机进行分类,它的分类依据为两个指标,1. 指令流 2. 数据流

无论是指令流还是数据流,它们都分为两种类型,一种是单的,一种是多的。

组合成了4种结构,包括单指令流单数据流、单指令流多数据流、多指令流单数据流、多指令流多数据流

单指令流单数据流: 指令流和数据流都是单个的,控制部件只有一个,处理器也只有一个,它的典型代表是单处理器系统,像以前用到的PC机,386、486、586(奔腾),这都属于单处理器系统。

单指令流多数据流: 控制部件只有一个,但处理部件会有多个,也就是说,发了一条指令,会有多个运算部件同时去做同样的运算,只是每一个部件的输入有差异而已。主要在阵列处理机应用,陈列处理机适合处理数组类型的运算,比如二维数组,要对数组与数组之间进行操作的时候,我们发现对很多数据作同样的操作,比如加法,对应进行加,一条加法指令,通过输入不同的数据,得到一组不同的结果。

多指令流单数据流: 有多个控制部件,而处理部件只有一个,属于一种理论模型。并不具备实际的意义与价值。

多指令流多数据流: 目前非常常见,有多个处理器,或者说把多个处理机(计算机)连起来,来共同完成一些任务,比如说集群的形式。

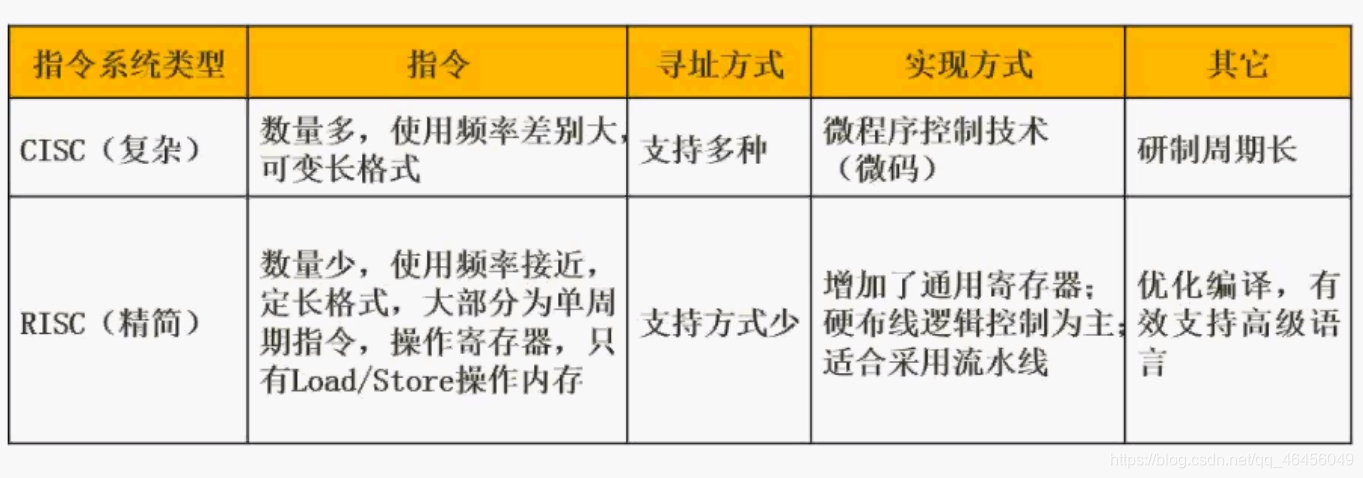

CISC和RISC

CISC是以前提出来(计算机还没有大规模的通用化的使用)的比较常用的系统,此时企业的计算机从硬件到指令系统都是定制的,CISC根据不同的用户会做不同的指令,而且指令本身系统很复杂,数量多。在计算机发展的历程中,原来基本上都是各个单位的专用设备,后来计算机成为了通用设备,每一个机构买一台计算机,装上软件就想之间跑,所以人们考虑把计算机的指令系统进行精简化,让它适应力更强一些,而且要作优化。这个时候就把繁杂的指令系统进行开始简化,简化到最基本的操作,然后复杂的操作都用基本的操作来替代。 例如:将乘法指令看成多个加法指令的累加…这样就降低了整个系统的指令数量,所以叫精简指令集。

CISC —— 指令数量多,使用频率差别大,可变长格式(指令在系统中有一个二进制的编码,编码的长度可以不同)。

——寻址方式: 支持多种

RISC数量少,使用频率接近,定长格式(所有的指令的长度是一样的),大部分为单周期指令,操作寄存器,只有Load/Store操作内存。

精简指令集为了提升效率,所以大量的引入了寄存器。绝大部分操作都是针对寄存器来操作的。(寄存器速度极快,效率极高)

——寻址方式: 支持方式少,考虑硬部件逻辑为主(效率高)

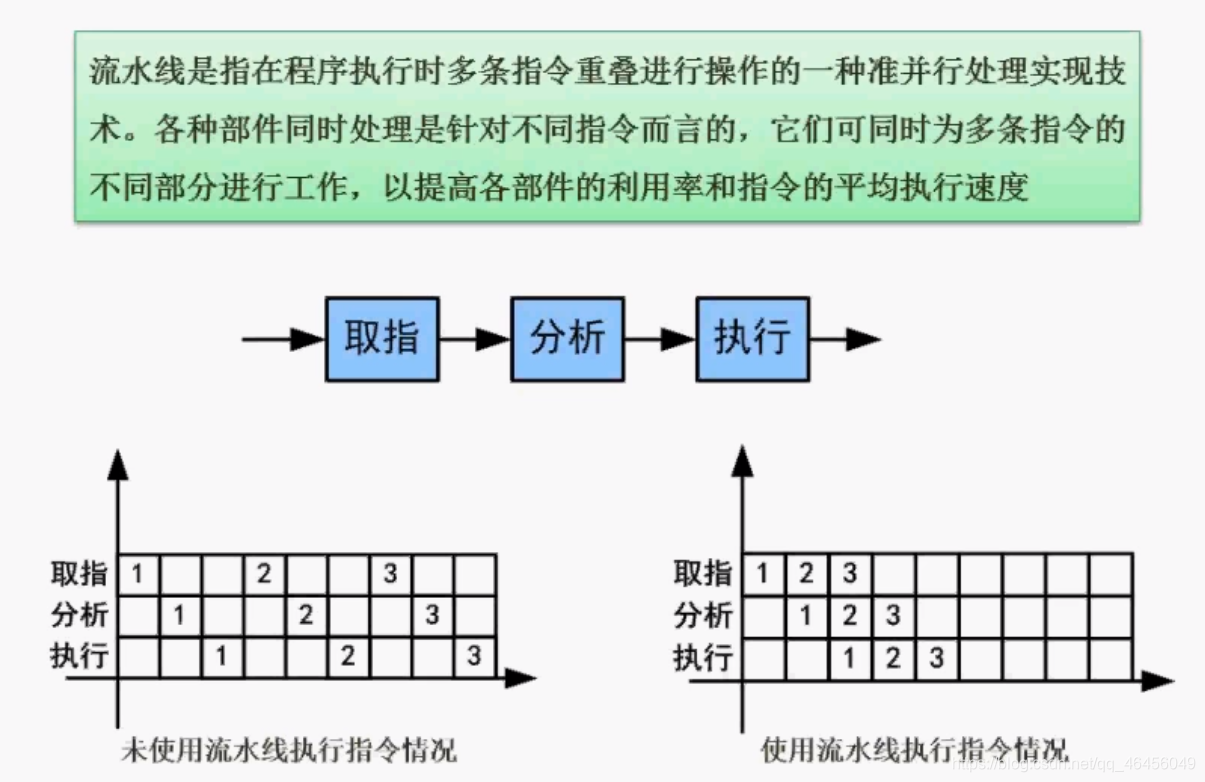

流水线

(主要考计算)

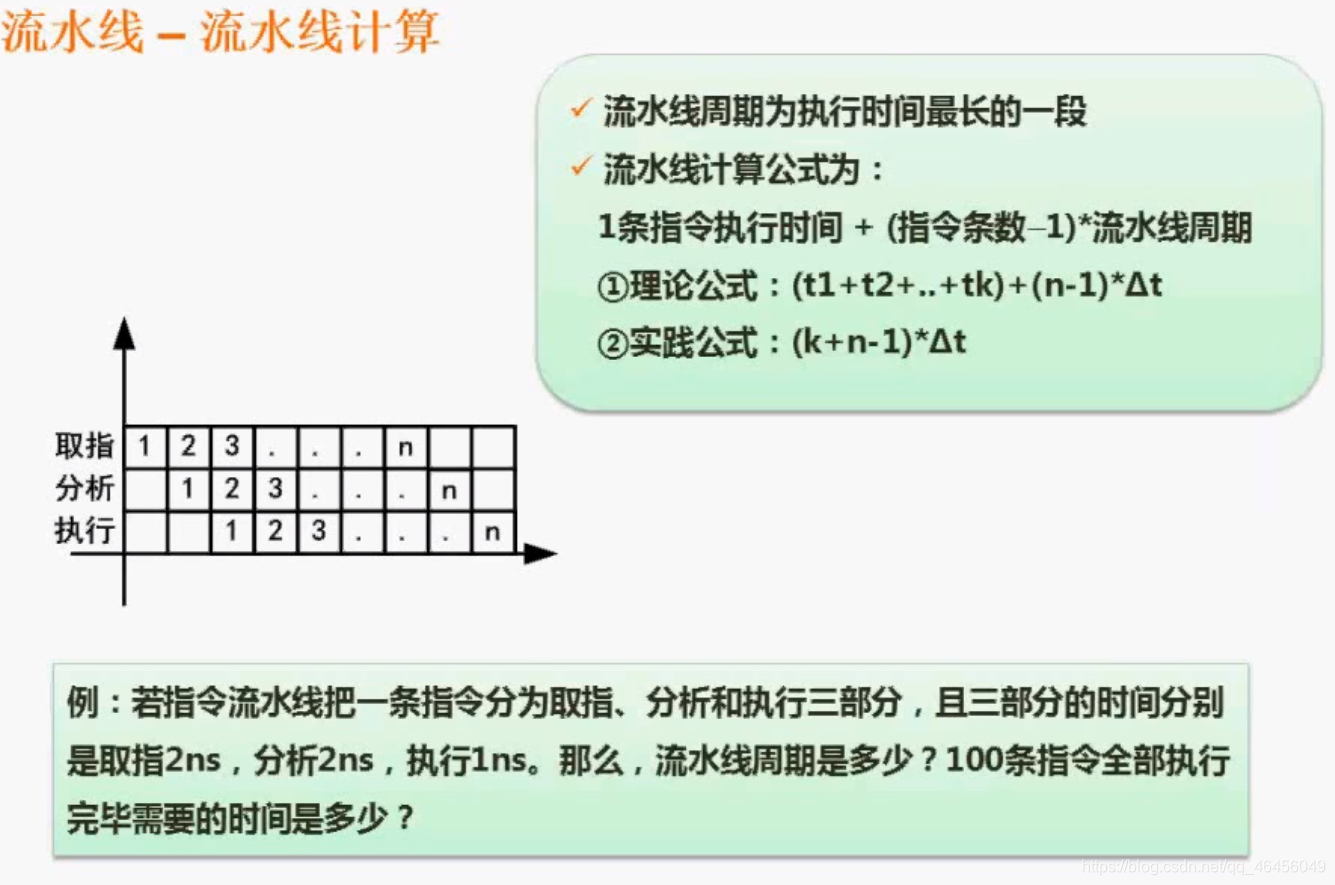

流水线计算

流水线周期为执行时间最长的一段(在整个的执行过程中,会分三个段: 取指、分析、执行,这三个段中最长的一段就是流水线周期),则上图中的流水线周期为2ns。

理论公式: 第一条指令执行完需要完成取指、分析、执行三段,用到的时间为(2 + 2 + 1),在第一条指令执行完后,第二条指令只需要一个周期即可执行完,在第二条指令执行完后,第三条指令只需要一个周期即可执行完…依次类推,所以后面的n-1条指令的执行在第一条指令执行完后需要 (n - 1) * t 时间,所以理论公式的计算为: 第一条指令的执行时间 + (n - 1) * t

实践公式是在理论公式的基础上,将第一条指令执行的每个段的时间都看作一个周期,所以总执行时间就等于 (k + n - 1) * t k为段数

所以上面的题按理论公式算下来是(2 + 2 + 1) + 99 * 2 = 203 ns

按实践公式算下来是(3 + 99) * 2 = 204 ns

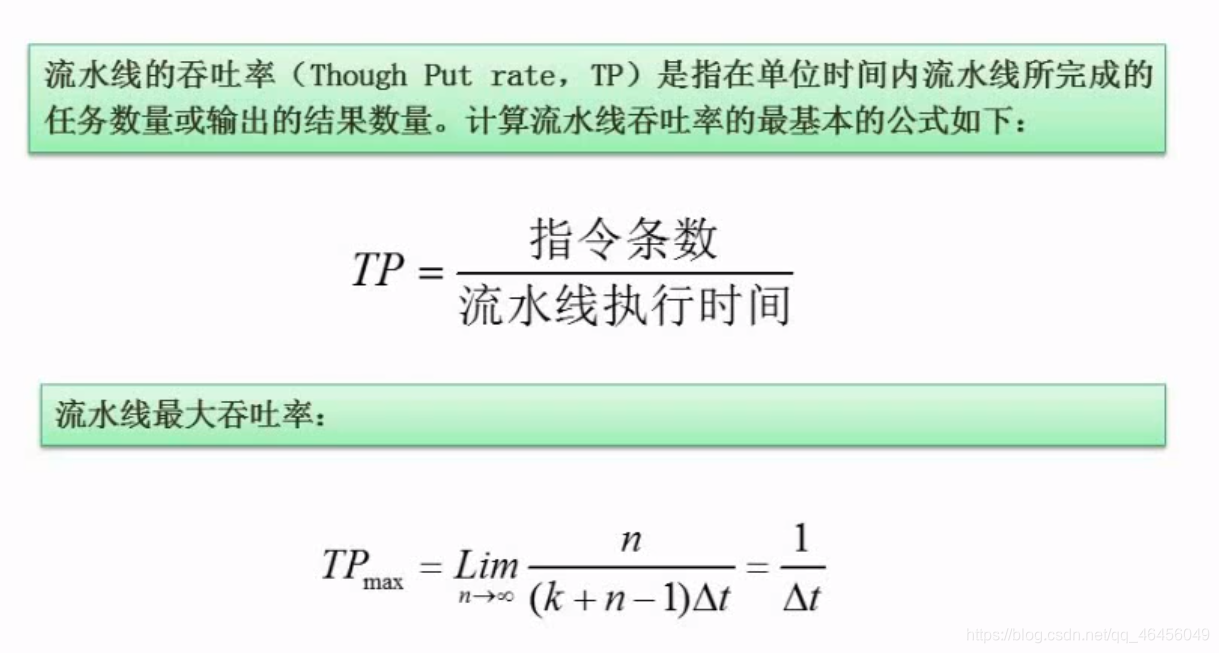

流水线吞吐率计算

TP = 执行条数 / 流水线执行时间,拿上个题的数据来计算就是 100 / 203

TPmax = 1 / t ⇒ 对应于上题就是1 / 2 ,(理想)状态,忽略流水线建立时间(即第一条指令执行所需的时间)比平常多用的时间。

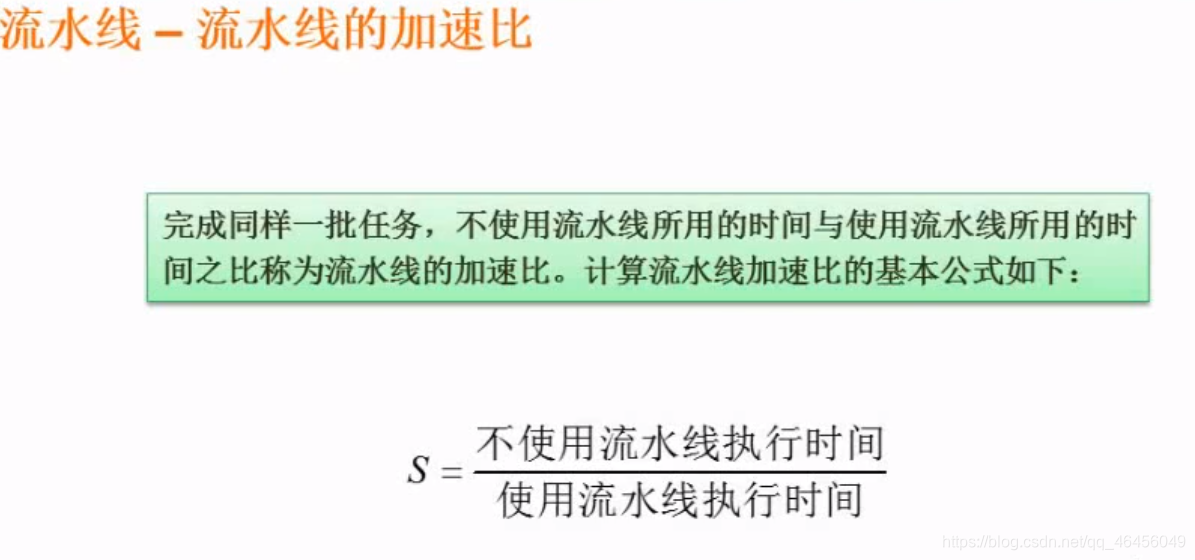

流水线的加速比计算

S = 不使用流水线执行时间 / 使用流水线执行时间,对应与上题就是 S = (2 + 2 + 1) * 100 / 203 = 500 / 203,可以看出S越大说明使用流水线提升的效率越高

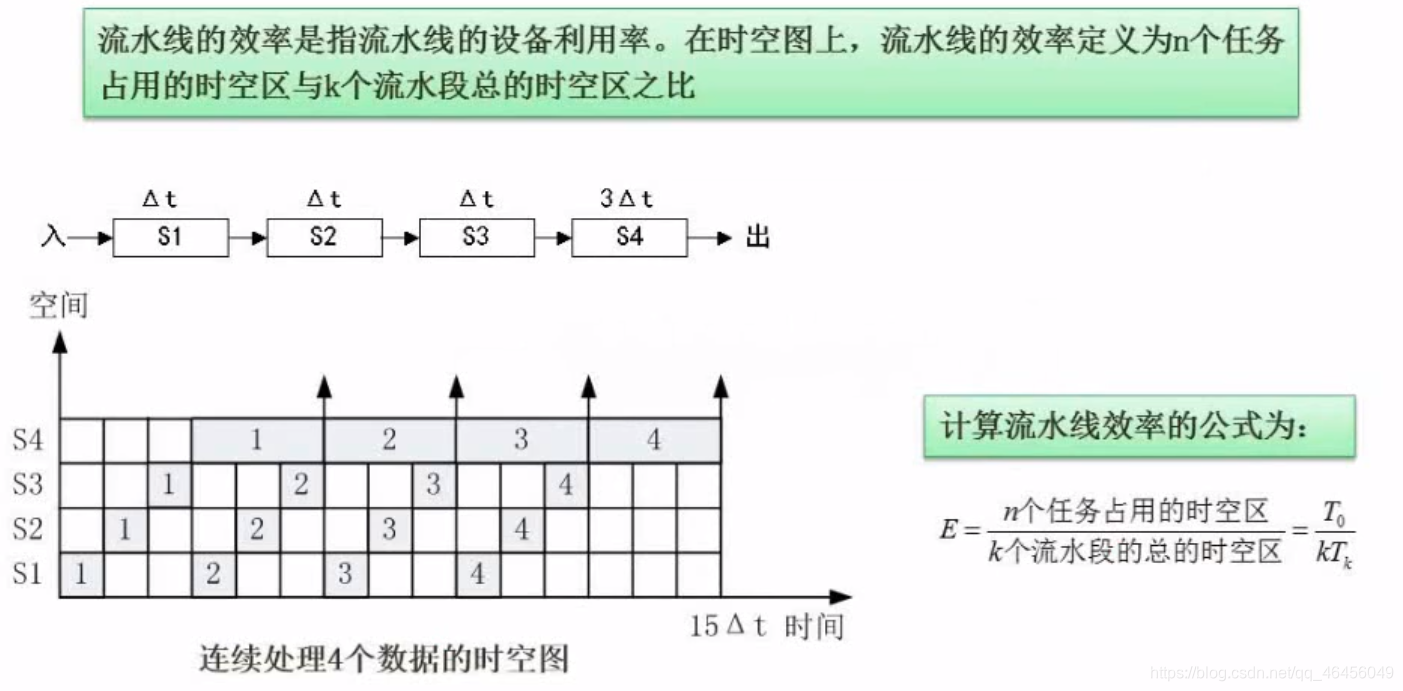

流水线的效率计算

可以理解为 图中的阴影面积 / 总面积 ⇒ 对应于上图就是 E = (t + t + t + 3t) * 4 / (15t * 4)

当流水线的每一个工作段的时长是相等的情况,往往效率最高

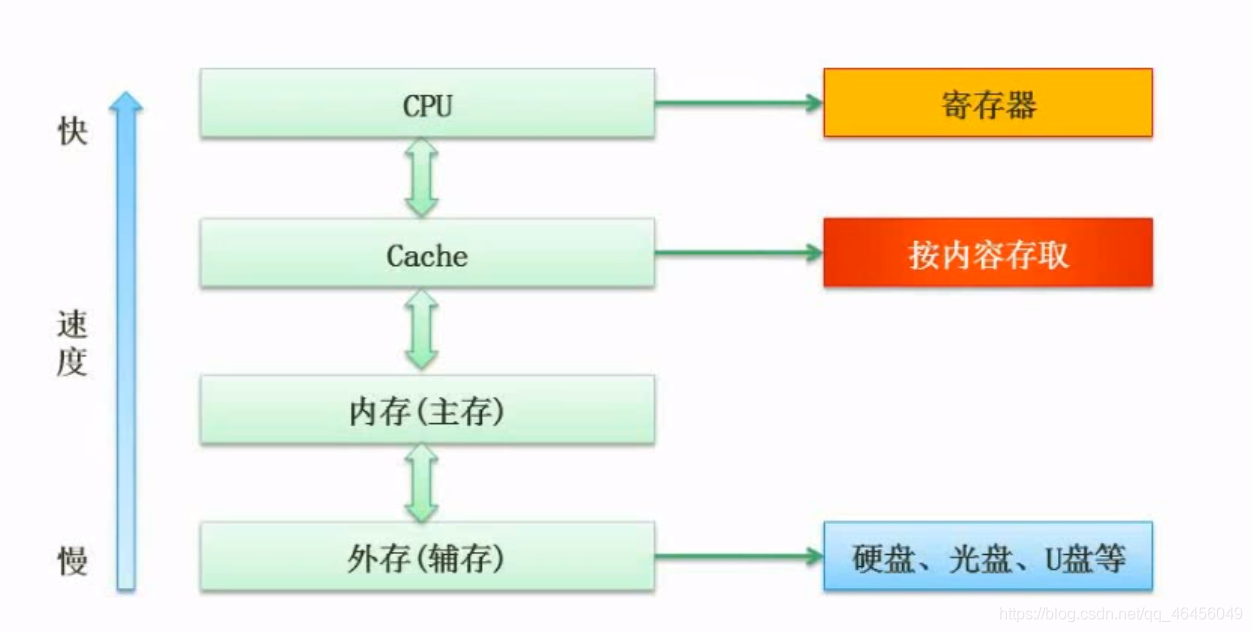

层次化存储结构

在整个层次化的结构中,速度最快、效率最高的是寄存器,寄存器存在于CPU当中,在CPU当中会有运算器、控制器,运算器和控制器里面有相应的寄存器。 寄存器的容量是极小的,但它的速度非常快,所以它是存储结构的最高层(顶层)。

Cache是高速缓存存储器

上图中结构从上往下容量越来越大,速度越来越小

CPU可以直接读取内存中的内容,不过读取速度会很慢,由于Cache缓存的读取速度高,所以用Cache存取内存中的一部分内容,让CPU直接操作缓存中的内容,这样效率会提高很多。(一般存取一些需要重复的操作/数据)

按内容存取: 存信息时,将信息中不同的内容存储到不同的区域,读取某个块的内容出来时,通过内容进行计算可得到该内容存储到哪个块当中。(相连存储器)它的速度、效率远高于按地址的存取方式。

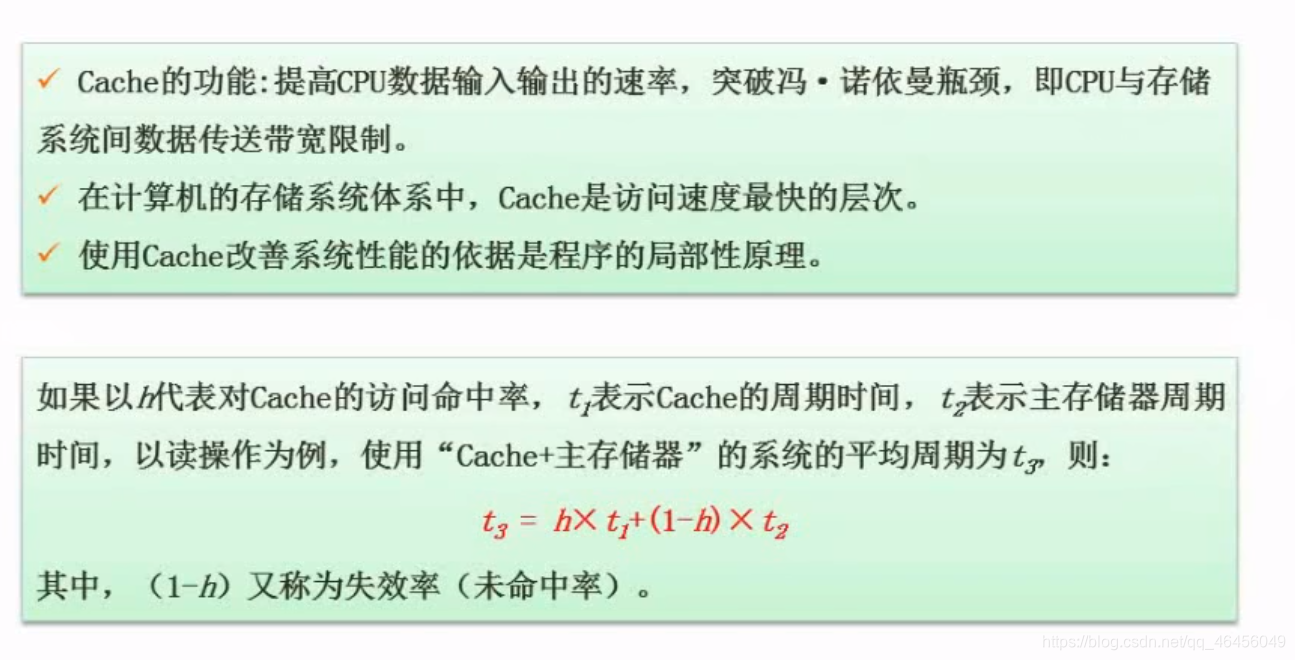

Cache

Cache工作于CPU和主存之间,他是为了提高访问的速度而提出来的一种方案,在整个的存储结构当中,除了寄存器,Cache是最快的。

Cache的访问命中率是CPU读取数据时,需要读取的数据在Cache中的概率。

假如Cache的存取的周期时间是1ns,主存存储周期为1μs,Cache的访问命中率是0.95

此时 t3 = 1 * 0.95 + 1000 * 0.05

所以不妨将上式看作加权和更助于理解

局部性原理

局部性原理主要是指计算机在处理相关的数据和程序的时候,一般都会有某一个时段集中的去访问某些指令或者读取某些空间的数据。

时间局部性: 刚刚访问完的指令再次访问

空间局部性: 当程序访问了一个空间,然后又访问这个空间临近的空间时候,将这种情况称为空间局部性。

工作集理论: 将频繁访问的页面的集合打包起来,使频繁访问的可以一起调入进来,短时间内不被替换出Cache,以提高效率。

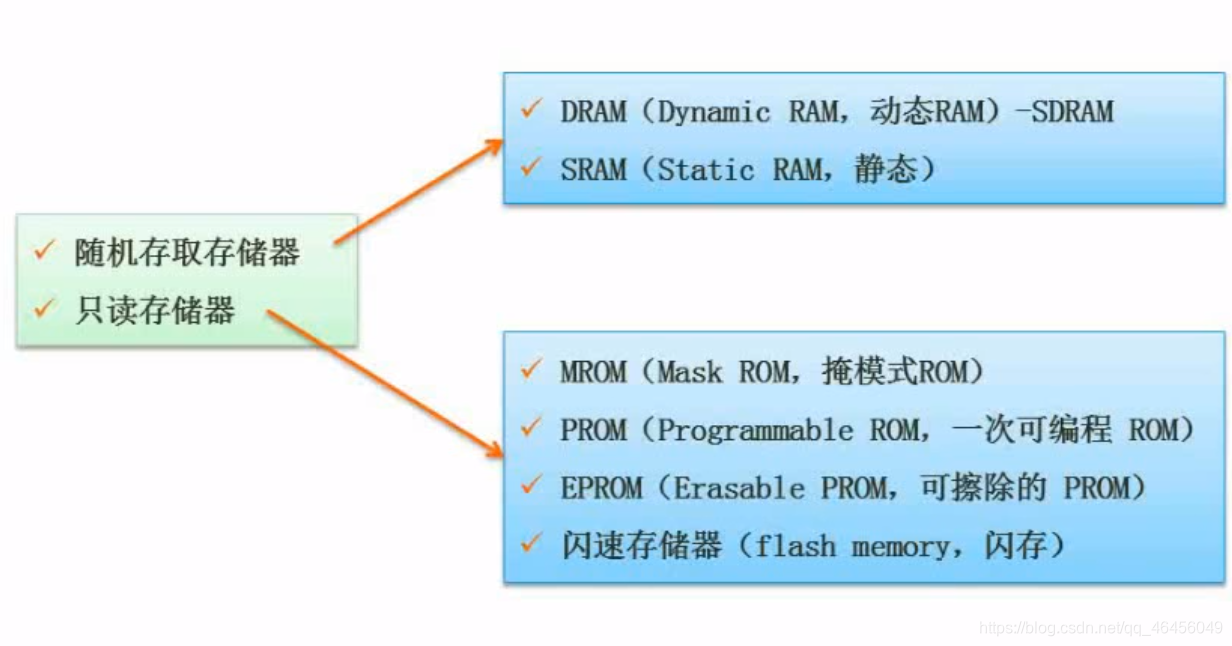

主存

随机存取存储器(RAM),只读存储器(ROM)

内存属于随机存取存储器,特点: 内存一旦断电,内存当中的数据都将被清除掉。

只读存储器(ROM): 断电之后依然能存储相应的信息。

主存的标志实际上就是将芯片组成相应的存储器。

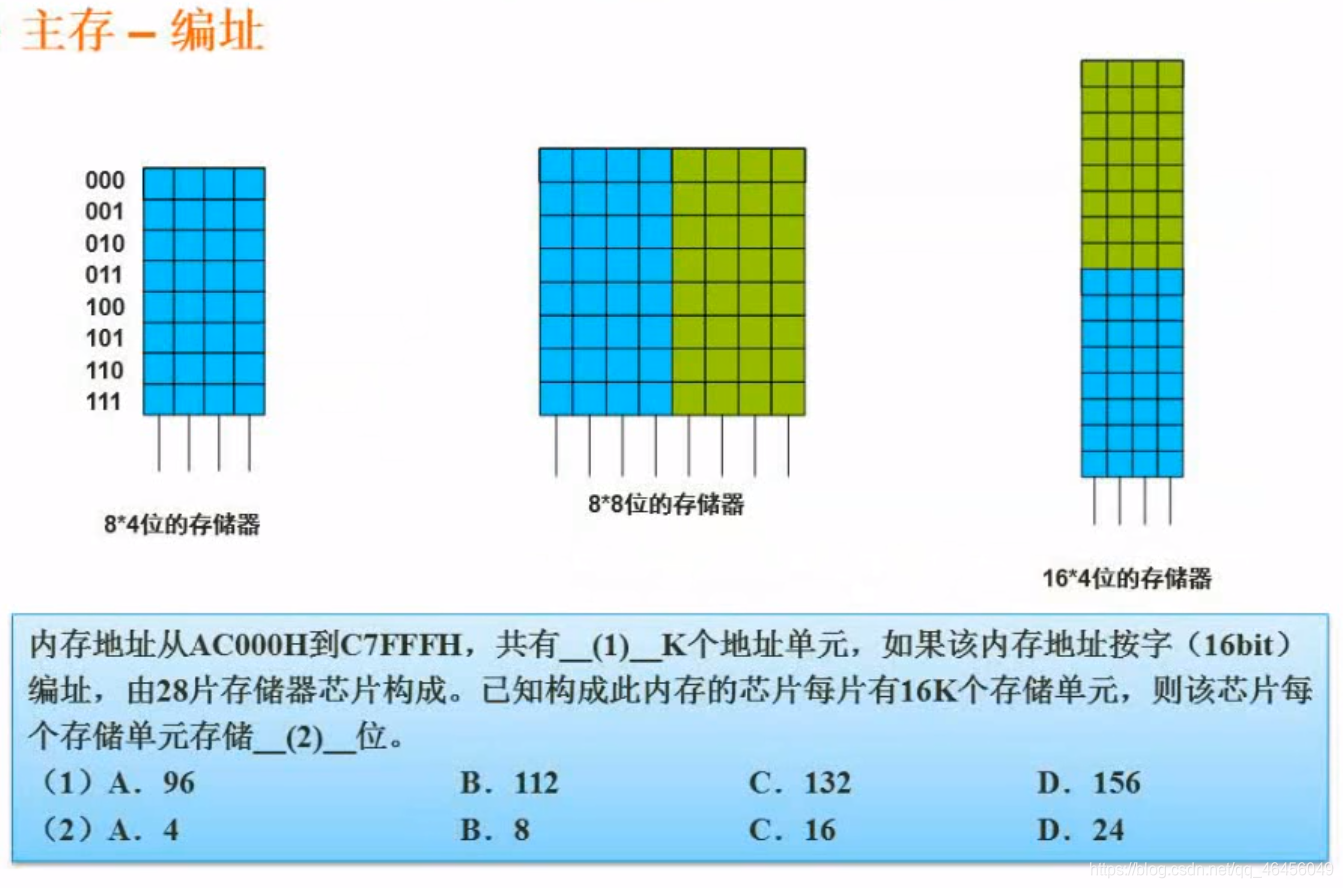

上图中 8 * 4位的存储器代表的是有8个地址空间(地址 / 存储单元),每一个地址空间存储了4个bit位的信息。

读取图中给出的题,地址单元的个数等于 C7FFF - AC000 + 1 = 1C000 换算为 K 则 1C000 / (2^10) = 112K

对于第二个空,设组成该芯片的每个存储单元存储x位,则有 112K * 16 = 16K * 28 * x ==》 解得 x = 4

对于这一问可以看作上式两边都是求面积。

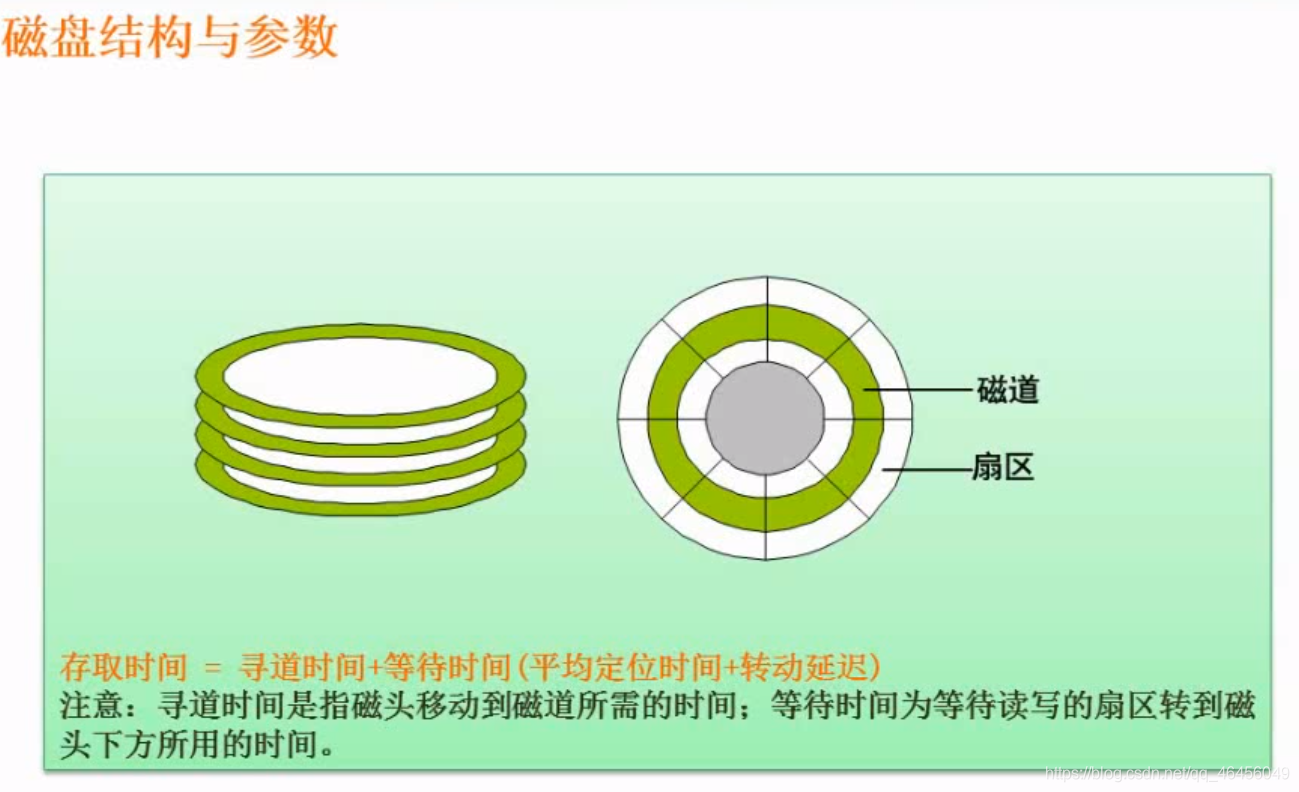

磁盘工作原理

磁盘是用一个环形的盘片,上面涂上特殊的材质来保存数据,在磁盘这种结构当中,盘面用来保存数据,磁头用来读取数据,磁头伸到盘面上,要读取信息的时候,磁头要挪到相应的磁道上面。(存信息存在磁道上面),寻找目标磁道的时候要消耗一定的时间,这个时间被称为寻道时间,等待时间(旋转延迟时间): 在一个磁道上面会分很多扇区(一个磁道上面的一小段),存储数据的时候就是存储在扇区上面,等待时间就是旋转磁盘到目标扇区所用的时间(取平均时间,转动一圈所用时间的一般)。

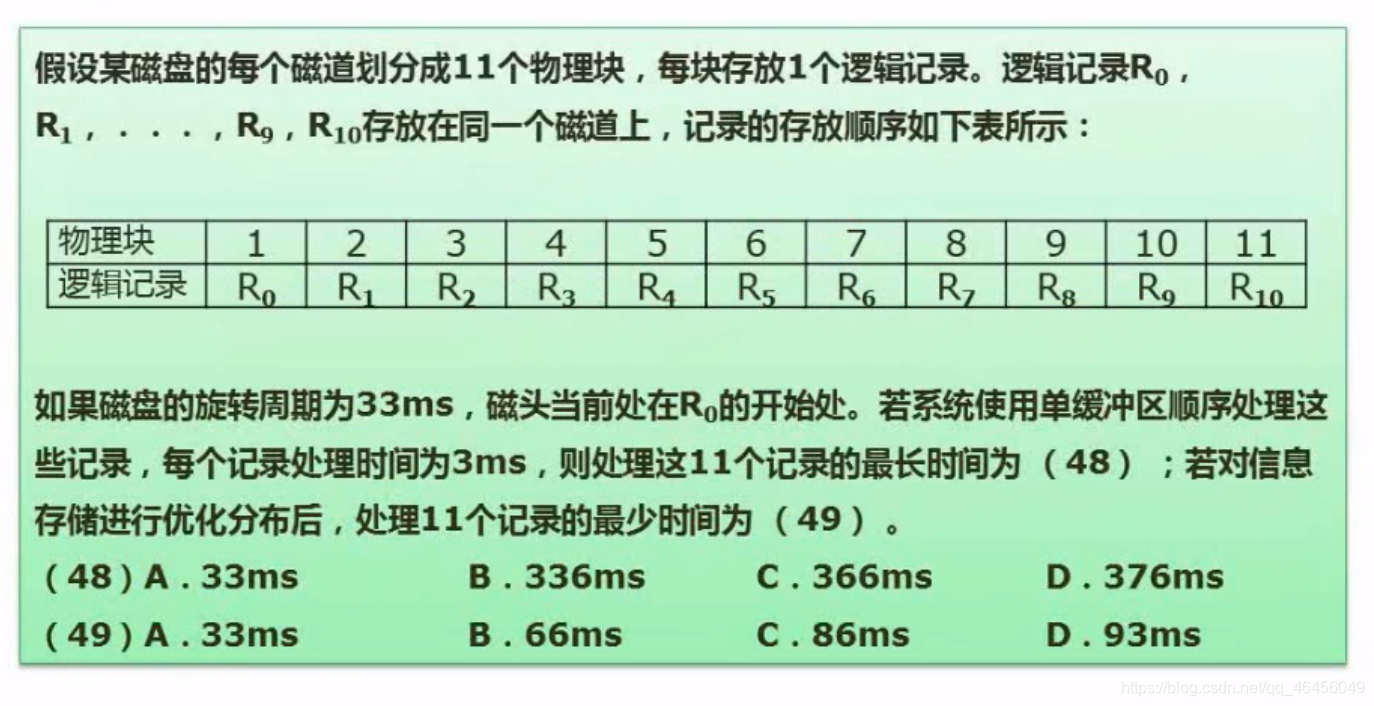

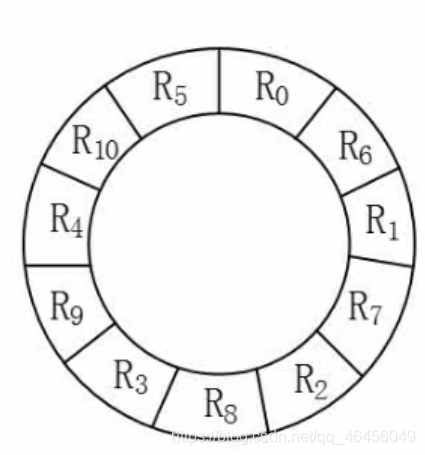

(单缓存区: 同一时间只能将读取到的一个数据放入缓存区处理,如果要处理下一条数据,只能等当前数据完成处理) ----- 旋转周期为33ms => 读取一个一个记录所消耗的时间为3ms, 当读取完R0后(3 ms ),将读取到的数据放入缓存区处理(3 ms),处理的同时磁盘也在转动,当处理完R0后,磁盘装动到R1的末尾,要读取出来R1的数据的话,需要转动一圈(33ms),从缓存区处理完成需要3ms,R1~R10都需要消耗 33 + 3 ms 才能完成读取+处理,R0则需要3+3 = 6ms,所以总的时间 t = (33 + 3) * 10 + 6 = 366ms

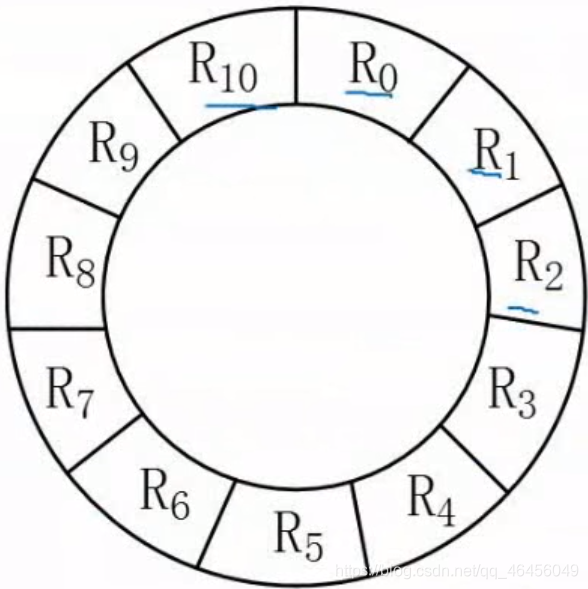

对存储进行优化分布后,只需要两个旋转周期就可以处理完(33*2 = 66 ms),(读取完R0后,对其进行处理(处理时,磁盘也在转动),处理完后,磁头恰好指到R1的开始…)

计算机总线

内部总线: 微机内部各个外围的芯片与处理器之间的总线。

系统总线: 微机中各个插件板和系统板之间的总线

外部总线: 微机和外部设备的总线。

数据总线是用来传输数据的,假如计算机是32位的,代表一个计算机的字(单位)就是32个bit位,这说明了总线的宽度就是32个bit位,那么我们一次/一个周期所能传输的数据量就是32个bit位

假设地址总线是32位,说明他代表的地址空间是232,也就是4G的宽度,所以我们发现如果我们用到的是32位的操作系统,它能够管理的内存就只有4G。

控制总线就是发送控制信号的总线。

系统可靠性分析与设计

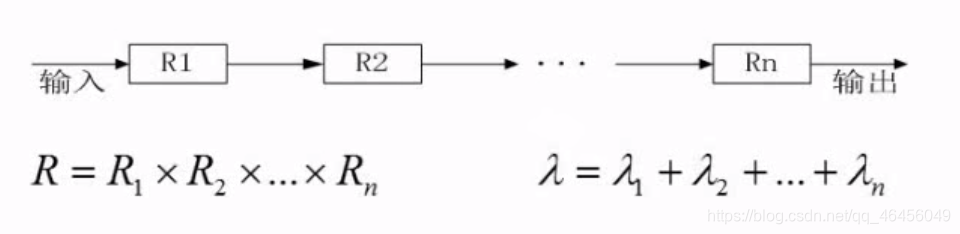

串联系统与并联系统

可以看到上面的串联系统,整个系统的子系统都必须正常运行,整个系统才正常。

所以整个系统的可靠度就是子系统的可靠度累乘(必须全部可靠)。相应的失效率的计算是累加(一个废全部废)。

注意: 对串联的失效率计算直接用加法这样计算的不准确,只有当R都很小的时候才能近似,否则偏差很大。

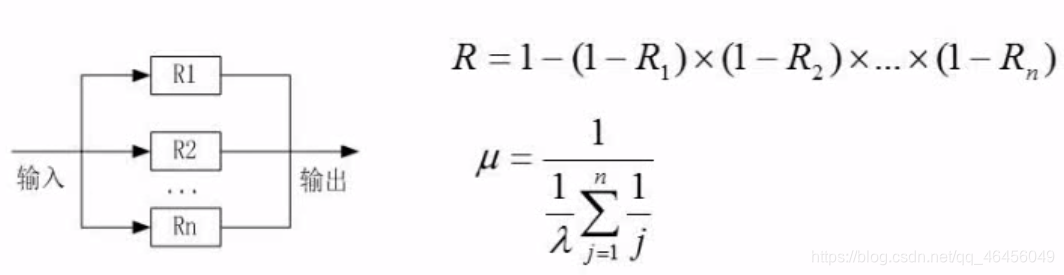

并联是多个子系统并在一起,并联的时候只要有一个子系统正常运行,则整个子系统就能正常运行。

(只有当所有子系统失效的时候,系统才失效)

所以可靠度为: 1 - 系统的失效率(子系统失效率累乘)。(不直接用加法原理是因为这样算的不准确,只有当R都很小的时候才能近似)

失效率就为1 - 可靠度

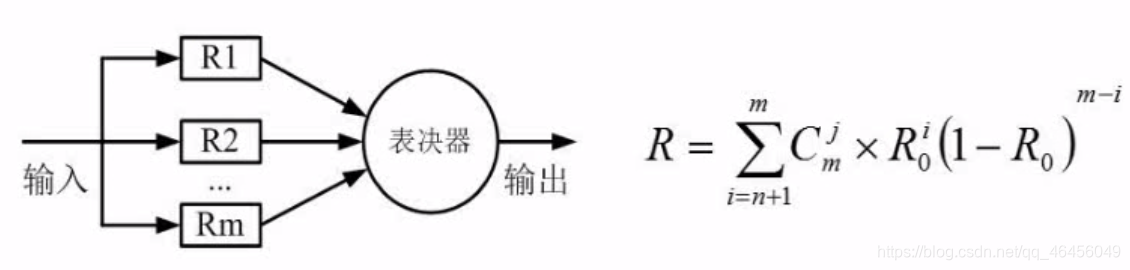

模冗余系统与混合系统

冗余模型: 在面向一些高可靠性的系统的要求的时候,提高系统可靠性可以通过冗余的方式来进行(R1,R2…Rm,多个模块是独立的,都做同样职能,都做同样的计算,它们分别计算出结果,系统到底采纳哪一个结果则通过表决来决定,所以R1~Rm的结果都会汇总到表决器)少数服从多数。

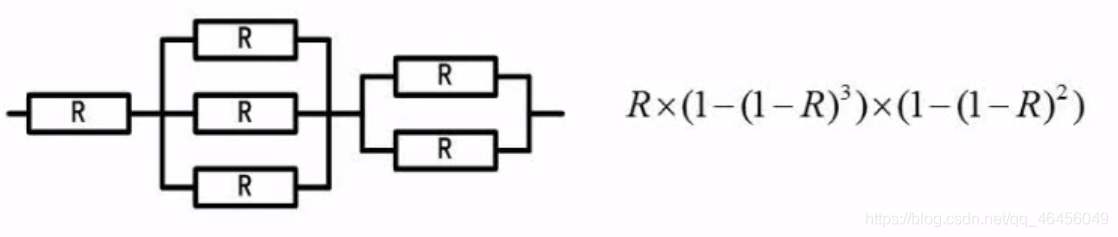

对于上述混合模型,从整体来讲,属于串行,可以先将中间并联和右边并列的分别求出可靠度,然后再看作一个串行,将可靠度累乘起来。

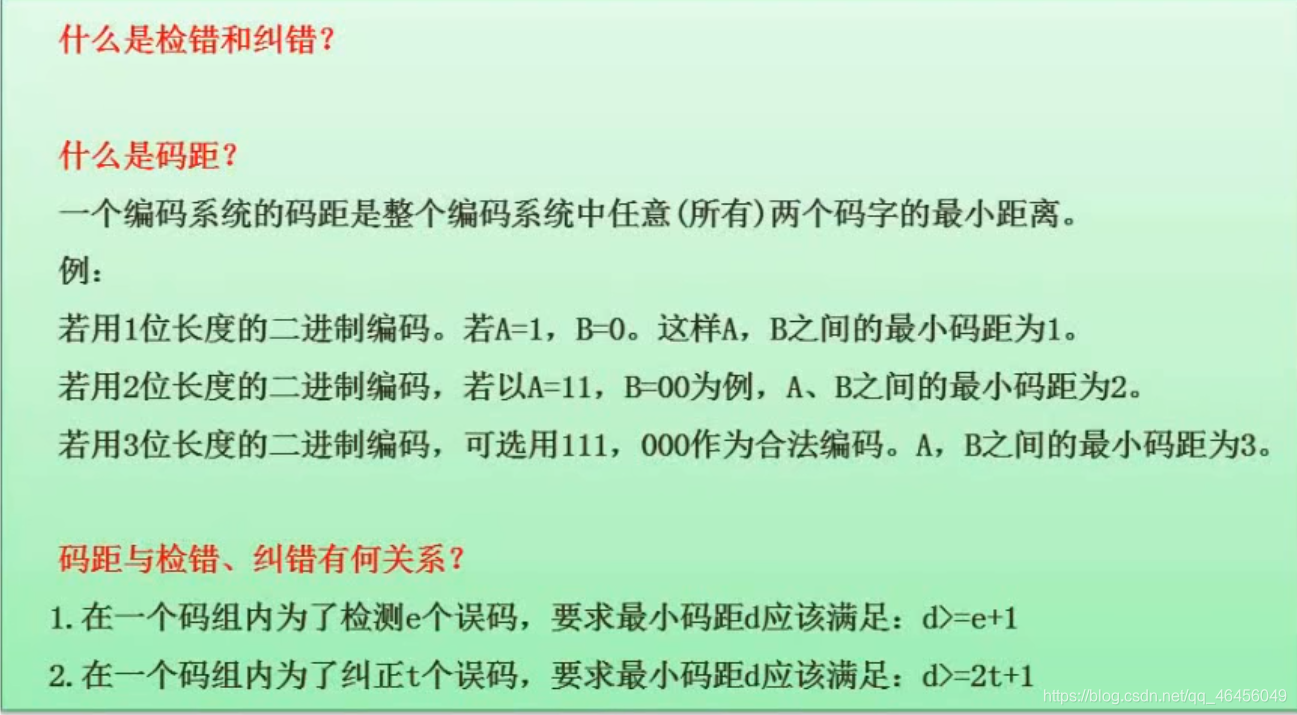

差错控制

A、B的码距: 将A的编码变为B的编码需要改的位数。

循环校验码CRC

可以检错,不可以纠错。

CRC基本原理和思路: 在进行信息的编码时,在它的尾部加入一些校验信息,加入这些校验信息之后,让编码后的数据能够与循环校验码的生成多项式相除,余数为零(不为零则说明传输过程中出现错误)。

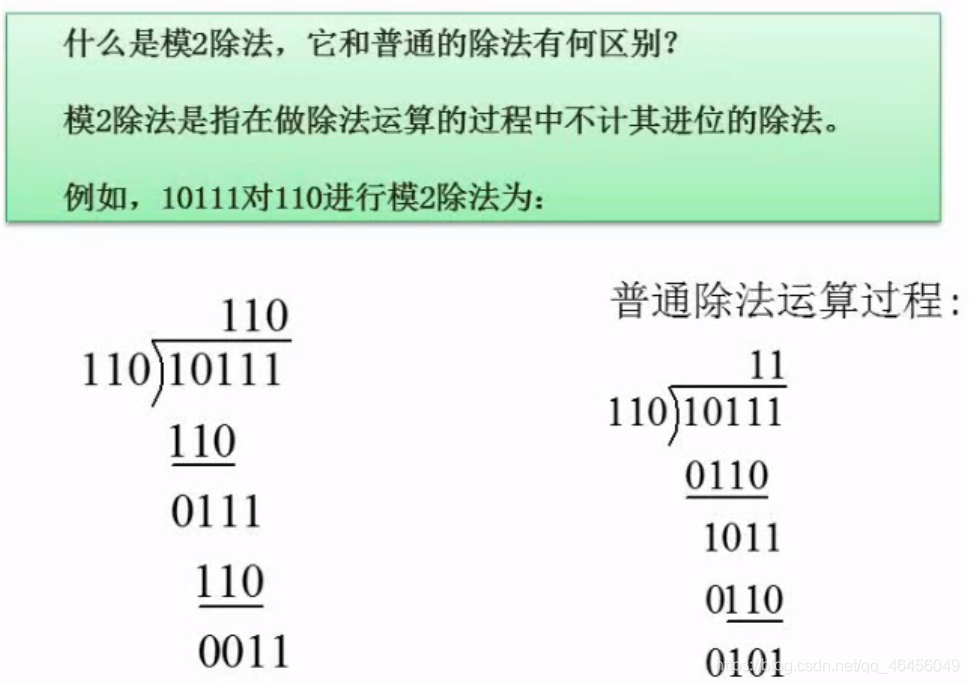

模2除法: 按位异或

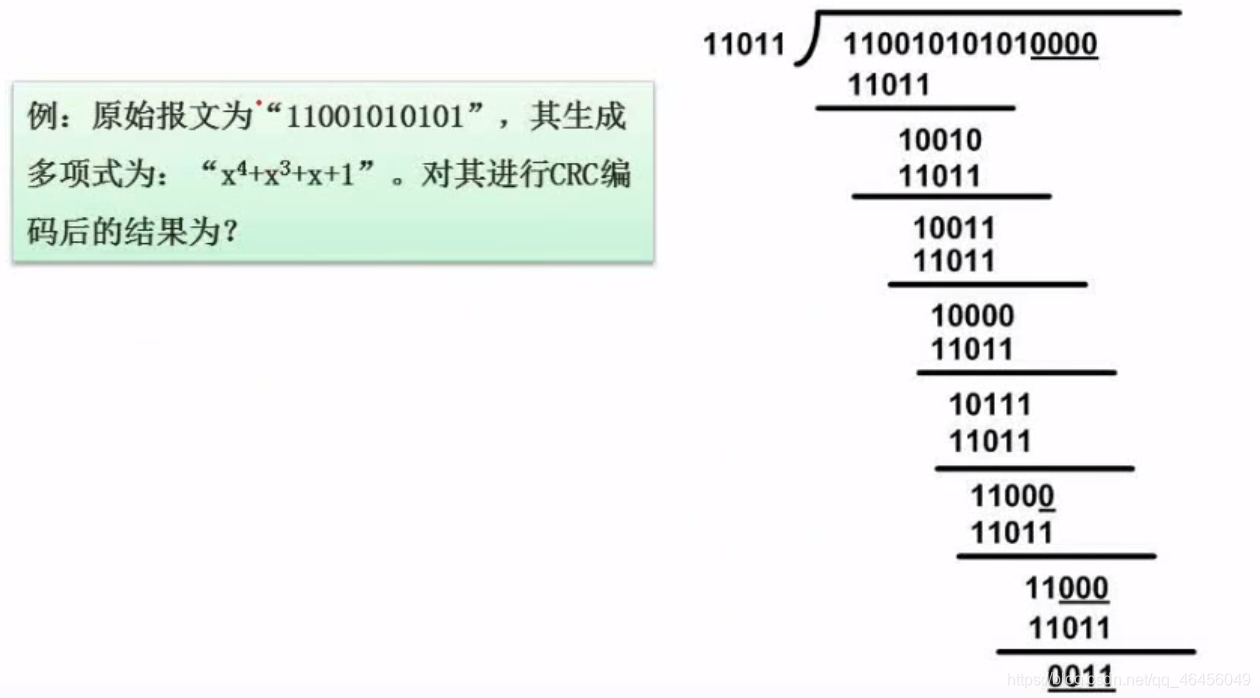

x的多少次方指示了对应的二进制位是1/0,对于x4 + x3 + x1 + 1 ⇒ 11011

在编码时要在原始报文后面 加 (生成多项式的二进编码的长度 - 1)个 0,

模2除法,除出来之后得到一个4位的余数,将其加到原始报文后面就得到了CRC编码。

收到这个上面通过CRC编码的信息后可以跟生成多项式(11011)进行模2的运算,余数为0则正确。

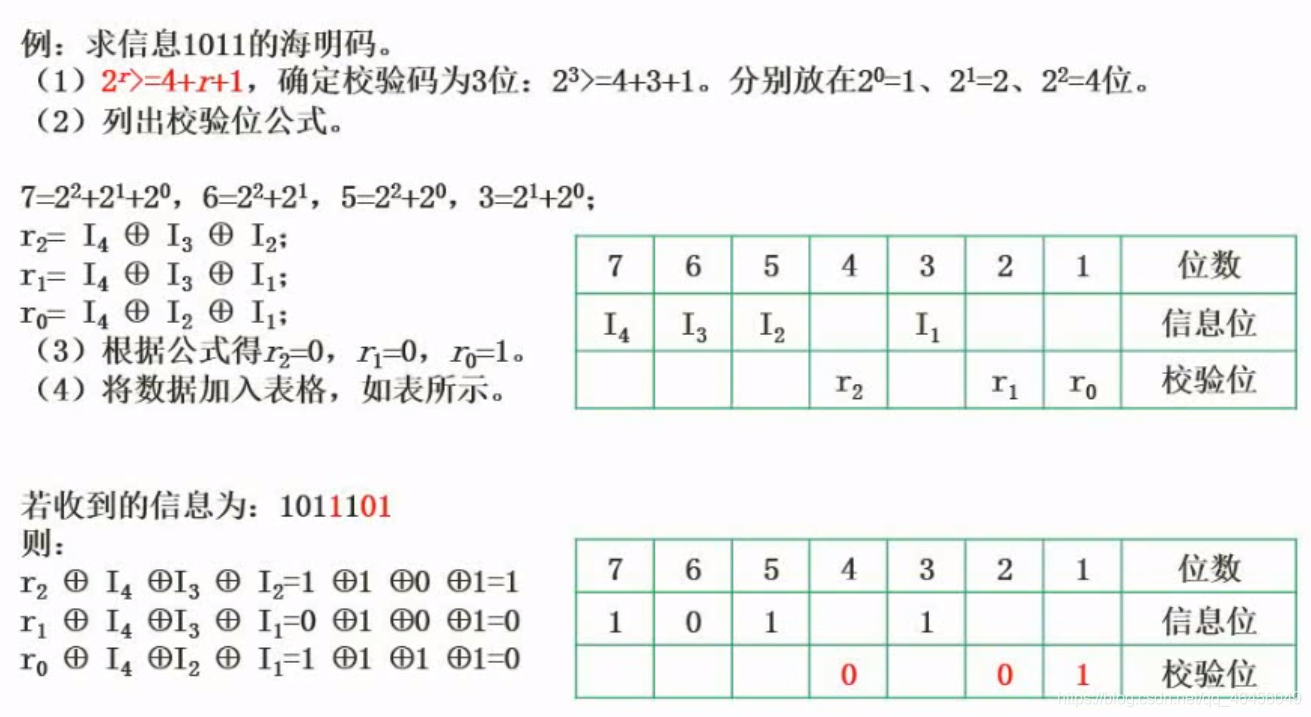

海明校验码

校验位的位置是位于整个信息编码的2n位置。

假如信息位有一个位的长度,则编码长度要有3个位的长度,因为20 = 1,21 = 2,存放的都是校验位。

确定校验位占的位数的公式: 2r >= x + r + 1,其中x是信息位的个数,r是校验位的个数。一般x是已知的,求校验位只需要从小(0)到大枚举,第一个满足上式子的r就是校验位的位数。

求出校验位位数后可得到总长度/位数为: 校验位长度 + 信息位长度

然后列一张表,将信息位和校验位填到相应位置即可。(校验位的计算: 将编码中每个信息位所在的位置用二进制加权求和表示,

如: 7 = 22 + 21 + 20,6 = 22 + 21 ,5 = 22 + 20,3 = 21 + 20)

将上面2次方出现过的次方用r次方的形式罗列出来

下标代表上式中的次方出现

r次方 = 这个下标在上式出现过的数对应信息位的信息进行异或操作的结果

如: r2 = 7位对应的是I4 ⊕ 6位对应的是I3 ⊕ 5位对应的是I2

即:

r2 = I4 ⊕ I3 ⊕ I2

r1 = I4 ⊕ I3 ⊕ I1

r0 = I4 ⊕ I2 ⊕ I1

然后将异或结果填入到对应校验位所在位置即可

.... 5 4 3 2 1 |位数 |

|信息位|

|校验位|

纠错: 假设有一位出错,接收到编码后,提取出信息位,按上面的方式求出校验位,然后再与提取出来的校验位按每一位进行异或操作,然后异或操作后的结果(换成10进制,100 ==> 6)对应位置即为出错位置。 然后对应位置取反即可。

本文为准备参加软考软件设计师考试的学习者提供了一份详细的知识点梳理,涵盖计算机组成、操作系统、数据库、计算机网络、系统安全等多个方面,并强调了刷题在备考过程中的重要性。建议考生在大二下或大三上备考,通过观看在线课程并配合刷题应用进行学习,以提高通过率。

本文为准备参加软考软件设计师考试的学习者提供了一份详细的知识点梳理,涵盖计算机组成、操作系统、数据库、计算机网络、系统安全等多个方面,并强调了刷题在备考过程中的重要性。建议考生在大二下或大三上备考,通过观看在线课程并配合刷题应用进行学习,以提高通过率。

1572

1572

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?