在使用STM32的时候,首先需要对时钟进行相应的配置,下面对时钟进行简要的分析说明。

(本文主要参考来源于ST官方手册以及野火的资料)

RCC (Reset Clock Control)– 复位和时钟控制器

时钟的几个重要的配置分别为:

(1) 系统时钟SYSCLK

(2) 设置AHB分频因子(决定HCLK等于多少)

(3) 设置APB2分频因子(决定PCLK2等于多少)

(4) 设置APB1分频因子(决定PCLK1等于多少)

(5) 设置各个外设的分频因子;

上述的几个分频系数的配置主要对应于AHB、APB2和APB1这三条总线时钟的开启

对于SYSCLK、HCLK、PCLK2、PCLK1这四个时钟的配置一般是: PCLK2 = HCLK = SYSCLK=PLLCLK = 72M

PCLK1=HCLK/2 = 36M

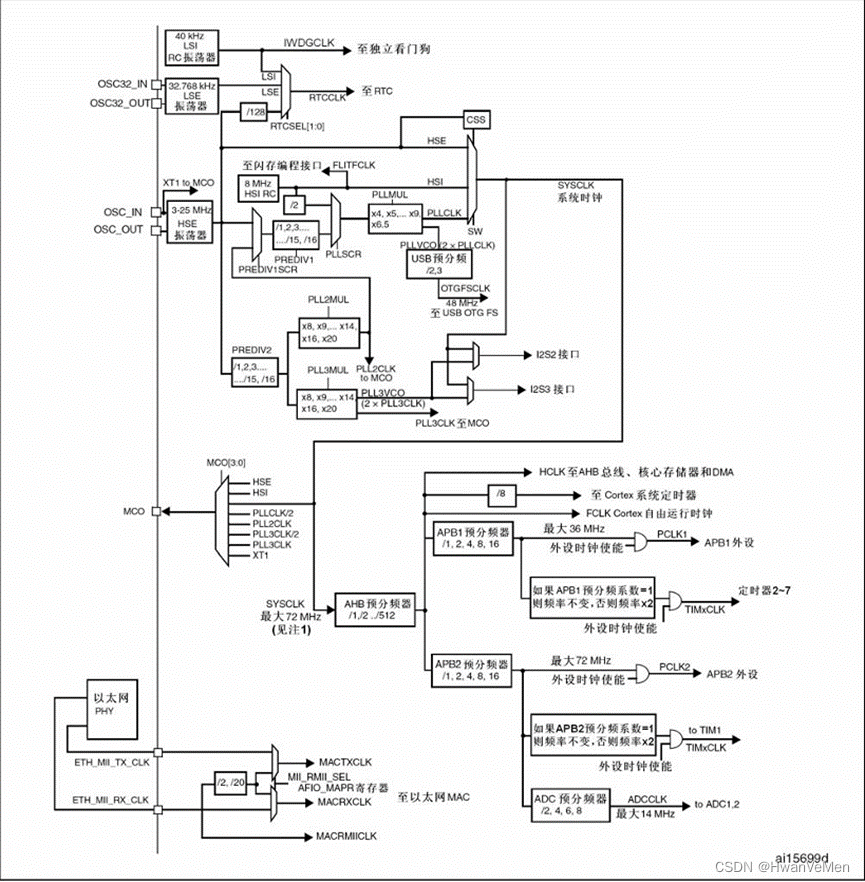

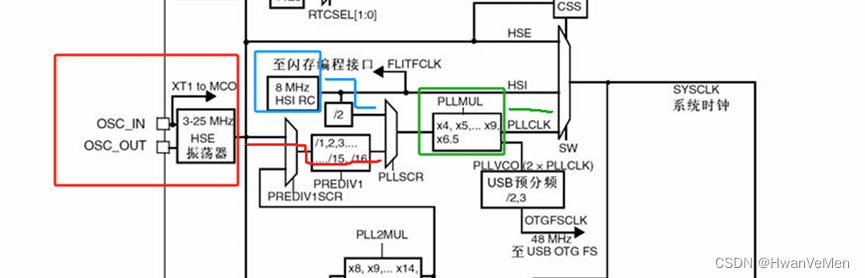

下面放一张STM32手册中的时钟树:

系统时钟SYSCLK

系统时钟来源可以是:HSI、PLLCLK、HSE

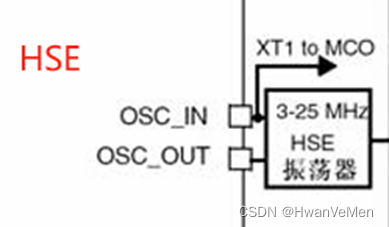

HSE是高速的外部时钟信号,可以由有源晶振或者无源晶振提供,频率从4-16MHZ不等。

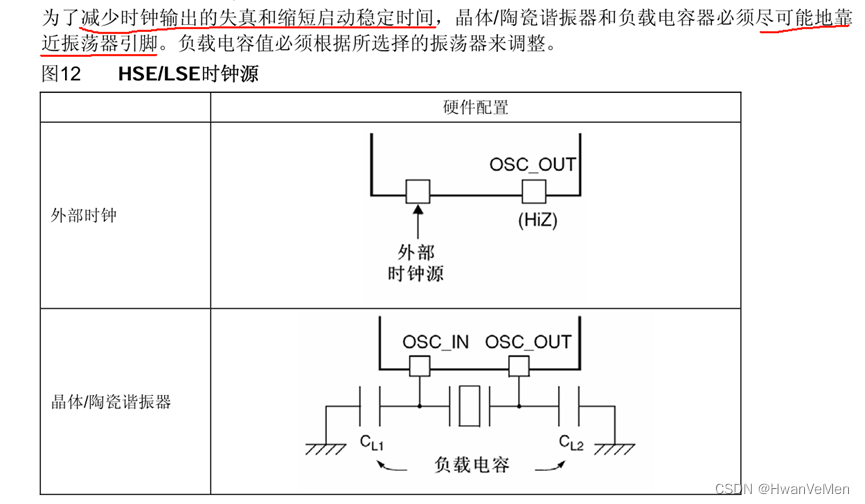

(1)当使用有源晶振时, 时钟从OSC_IN引脚进入,OSC_OUT引脚悬空,

(2)当选用无源晶振时,时钟从OSC_IN和OSC_OUT进入,并且要配谐振电容。

HSE最常使用的就是8M的无源晶振。当确定PLL时钟来源的时候,HSE可以不分频或者2分频, 这个由时钟配置寄存器CFGR的位17:PLLXTPRE设置,我们设置为HSE不分频。

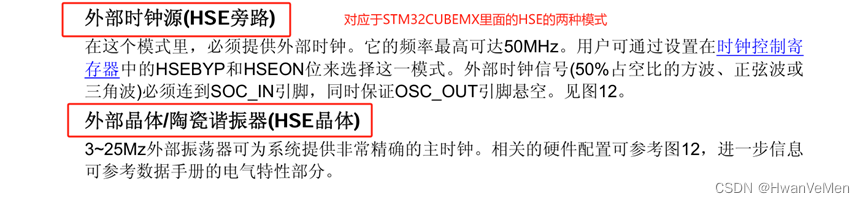

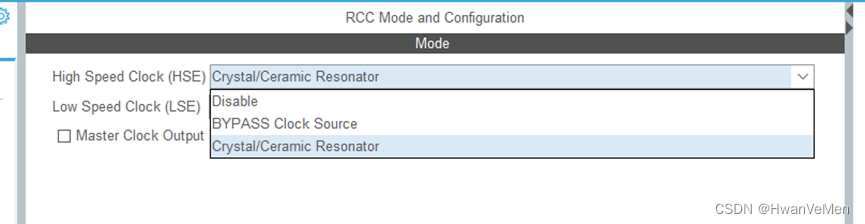

HSE时钟

高速外部时钟信号(HSE)来源可以有两个,一个来自HSE外部晶体/陶瓷谐振器,另外一个是HSE用户外部时钟:

HSI时钟

HSI时钟信号由内部8MHz的RC振荡器产生,可直接作为系统时钟或在2分频后作为PLL输入。 HSI RC振荡器能够在不需要任何外部器件的条件下提供系统时钟。它的启动时间比HSE晶体振荡器短。然而,即使在校准之后它的时钟频率精度仍较差。

校准:

制造工艺决定了不同芯片的RC振荡器频率会不同,这就是为什么每个芯片的HSI时钟频率在出厂前已经被ST校准到1%(25°C)的原因。系统复位时,工厂校准值被装载到时钟控制寄存器的 HSICAL[7:0]位。

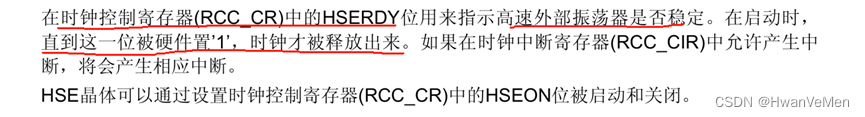

如果用户的应用基于不同的电压或环境温度,这将会影响RC振荡器的精度。可以通过时钟控制 寄存器里的HSITRIM[4:0]位来调整HSI频率。 时钟控制寄存器中的HSIRDY位用来指示HSI RC振荡器是否稳定。在时钟启动过程中,直到这 一位被硬件置’1’,HSI RC输出时钟才被释放。HSI RC可由时钟控制寄存器中的HSION位来启 动和关闭。

如果HSE晶体振荡器失效,HSI时钟会被作为备用时钟源

因为HSI时钟来源是由内部的RC振荡器产生的,并且RC振荡器会受到温度以及电压的影响,导致时钟精度较差,所以一般不使用HSI作为PLL时钟的来源

HSI是内部高速的时钟信号,频率为8M,根据温度和环境的情况频率会有漂移,一般不作为PLL的时钟来源。这里我们选HSE作为PLL的时钟来源。

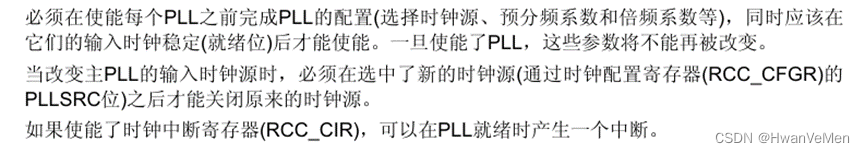

PLL时钟源

PLL时钟来源可以有两个:一个来自HSE,另外一个是HSI/2,具体用哪个由时钟配置寄存器CFGR的位16:PLLSRC设置。

PLL时钟来源选择如下图:红色是HSE,蓝色是HSI,绿色是PLL倍频因数

PLL时钟PLLCLK

通过设置PLL的倍频因子,可以对PLL的时钟来源进行倍频,倍频因子可以是:[2,3,4,5,6,7,8,9,10,11,12,13,14,15,16], 具体设置成多少,由时钟配置寄存器CFGR的位21-18:PLLMUL[3:0]设置。我们这里设置为9倍频, 因为上一步我们设置PLL的时钟来源为HSE=8M,所以经过PLL倍频之后的PLL时钟:PLLCLK = 8M *9 = 72M。 72M是ST官方推荐的稳定运行时钟,如果你想超频的话,增大倍频因子即可,最高为128M。 我们这里设置PLL时钟:PLLCLK = 8M *9 = 72M。

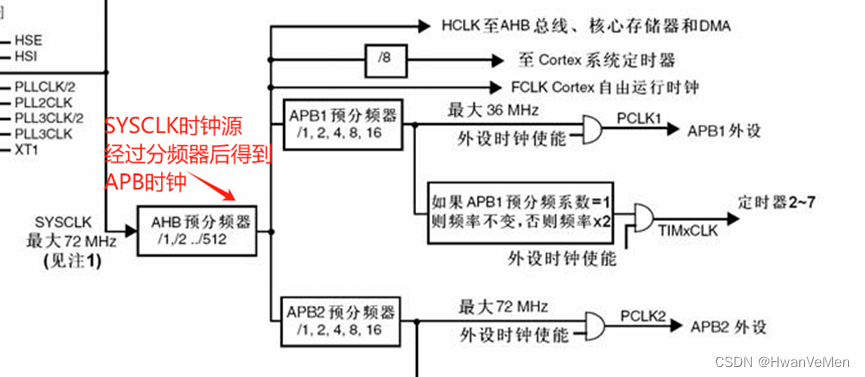

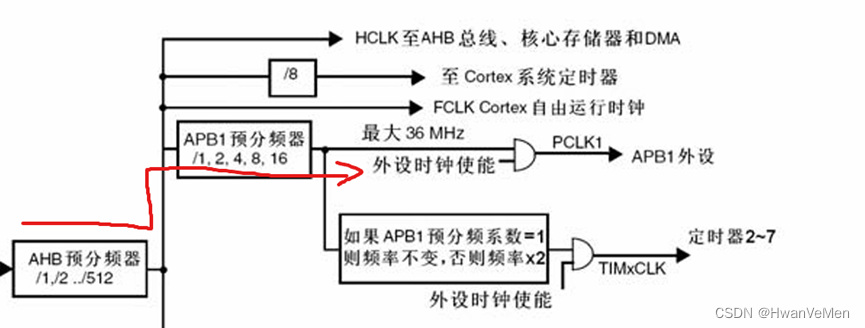

AHB总线时钟HCLK

系统时钟SYSCLK经过AHB预分频器分频之后得到时钟叫APB总线时钟,即HCLK,分频因子可以是:[1,2,4,8,16,64,128,256,512], 具体的由时钟配置寄存器CFGR的位7-4 :HPRE[3:0]设置。

片上大部分外设的时钟都是经过HCLK分频得到, 至于AHB总线上的外设的时钟设置为多少,得等到我们使用该外设的时候才设置, 我们这里只需粗线条的设置好APB的时钟即可。我们这里设置为1分频,即HCLK=SYSCLK=72M。

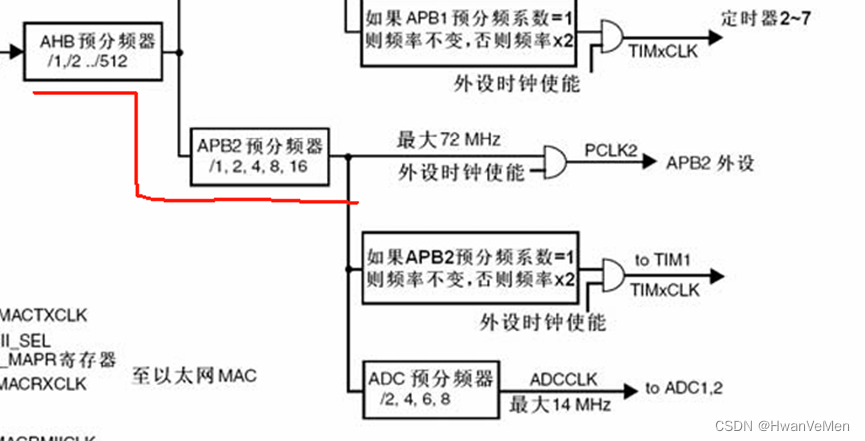

APB2总线时钟PCLK2

APB2总线时钟PCLK2由HCLK经过高速APB2预分频器得到,分频因子可以是:[1,2,4,8,16],具体由时钟配置寄存器CFGR的位13-11:PPRE2[2:0]决定。 PCLK2属于高速的总线时钟,片上高速的外设就挂载到这条总线上,比如全部的GPIO、USART1、SPI1等。至于APB2总线上的外设的时钟设置为多少, 得等到我们使用该外设的时候才设置,我们这里只需粗线条的设置好APB2的时钟即可。我们这里设置为1分频,即PCLK2 = HCLK = 72M。

APB1总线时钟PCLK1

APB1总线时钟PCLK1由HCLK经过低速APB预分频器得到,分频因子可以是:[1,2,4,8,16],具体的由时钟配置寄存器CFGR的位10-8:PRRE1[2:0]决定。 PCLK1属于低速的总线时钟,最高为36M,片上低速的外设就挂载到这条总线上,比如USART2/3/4/5、SPI2/3,I2C1/2等。 至于APB1总线上的外设的时钟设置为多少,得等到我们使用该外设的时候才设置,我们这里只需粗线条的设置好APB1的时钟即可。 我们这里设置为2分频,即PCLK1 = HCLK/2 = 36M。

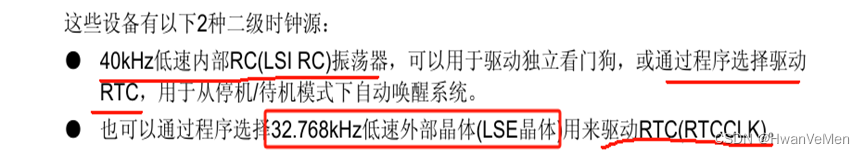

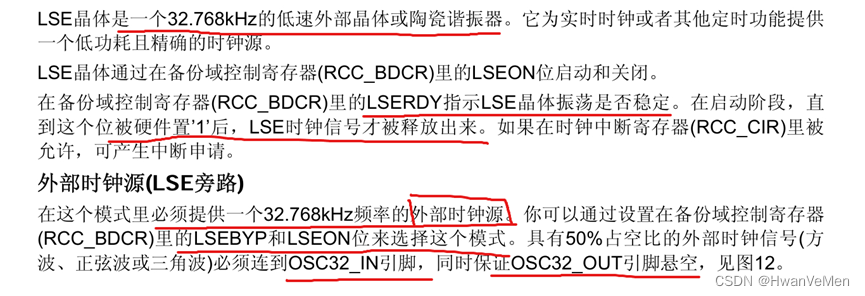

LSE时钟

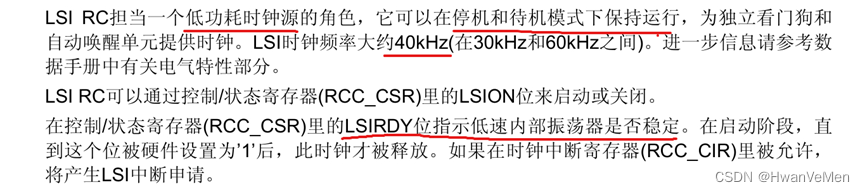

LSI时钟

4423

4423

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?