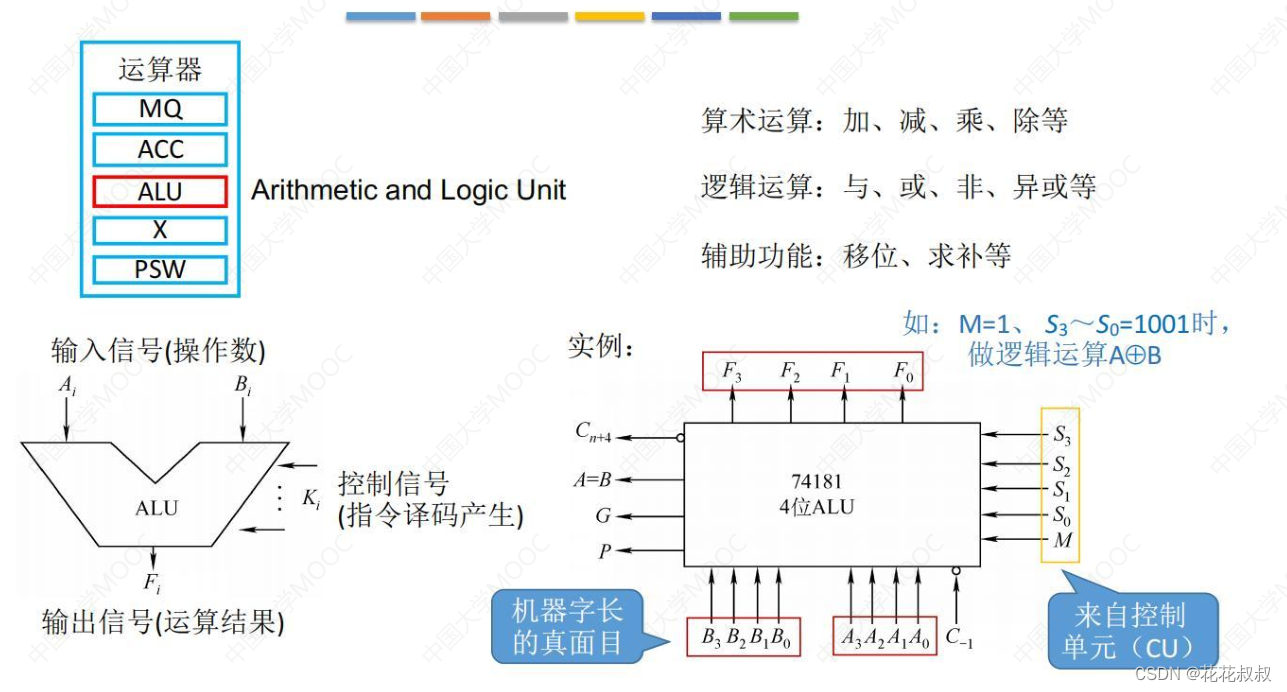

算术逻辑单元

算术逻辑单元就是运算器里面的ALU,这个东西的作用就是对数字进行算术运算或者是逻辑运算。

下面的A B 指的就是参与运算的两个数字,右边指的就是对数字进行什么操作,下面的M就是传递这次操作时算术运算还是逻辑运算。F就是运算结果,左边的那些是串联或者并联的接口。

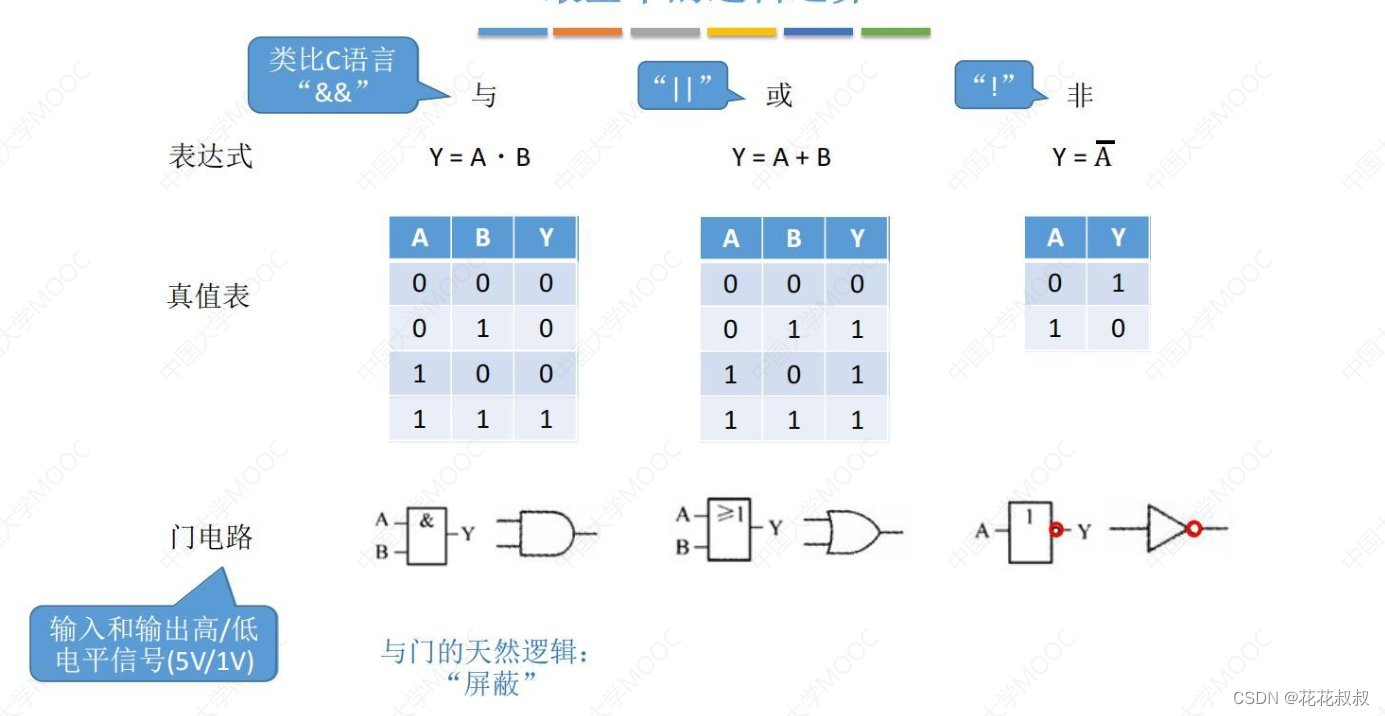

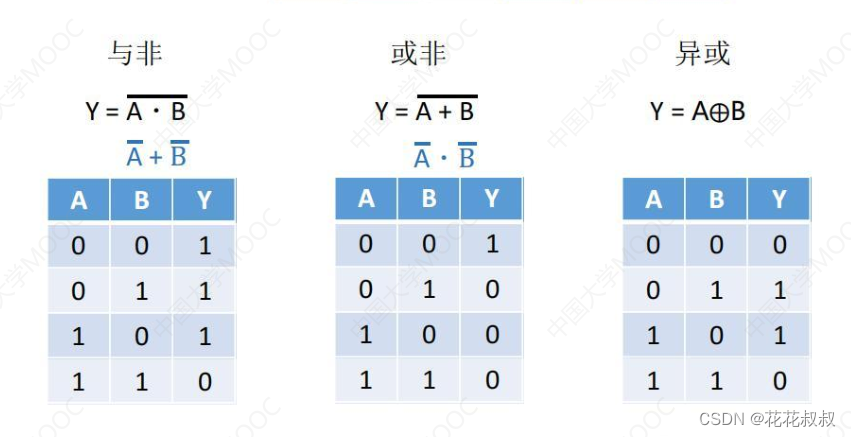

逻辑运算

异或:两个数字不一样的话,结果就是1,否则是0。

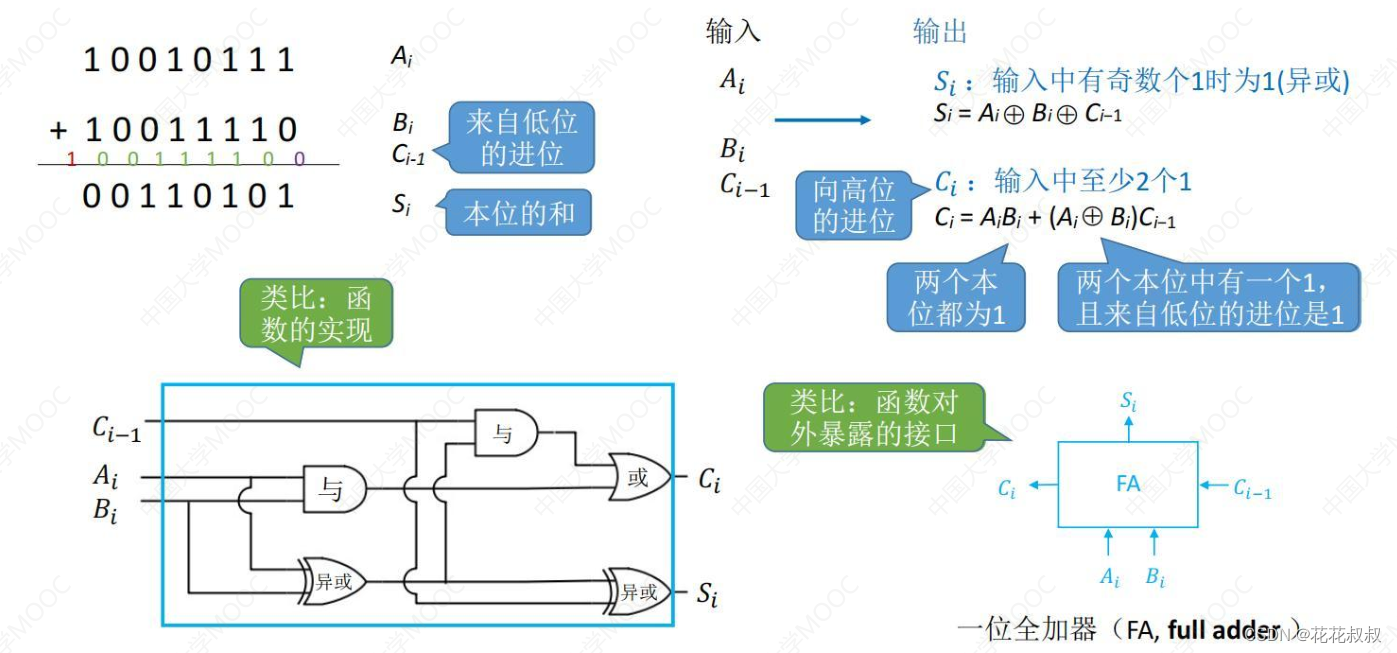

一位全加器

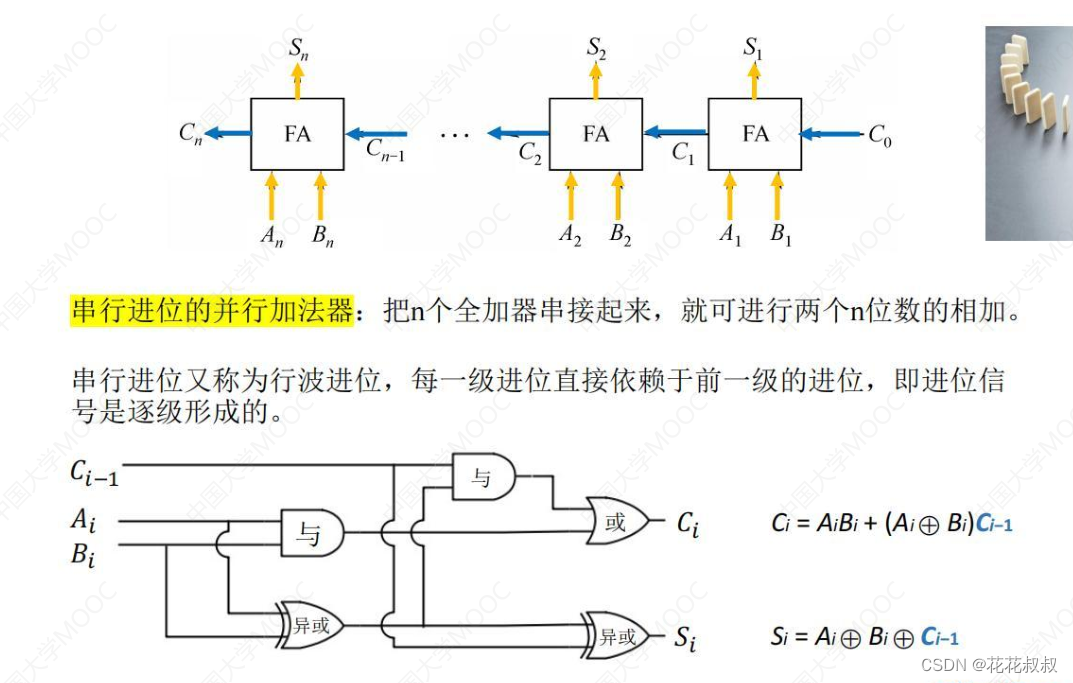

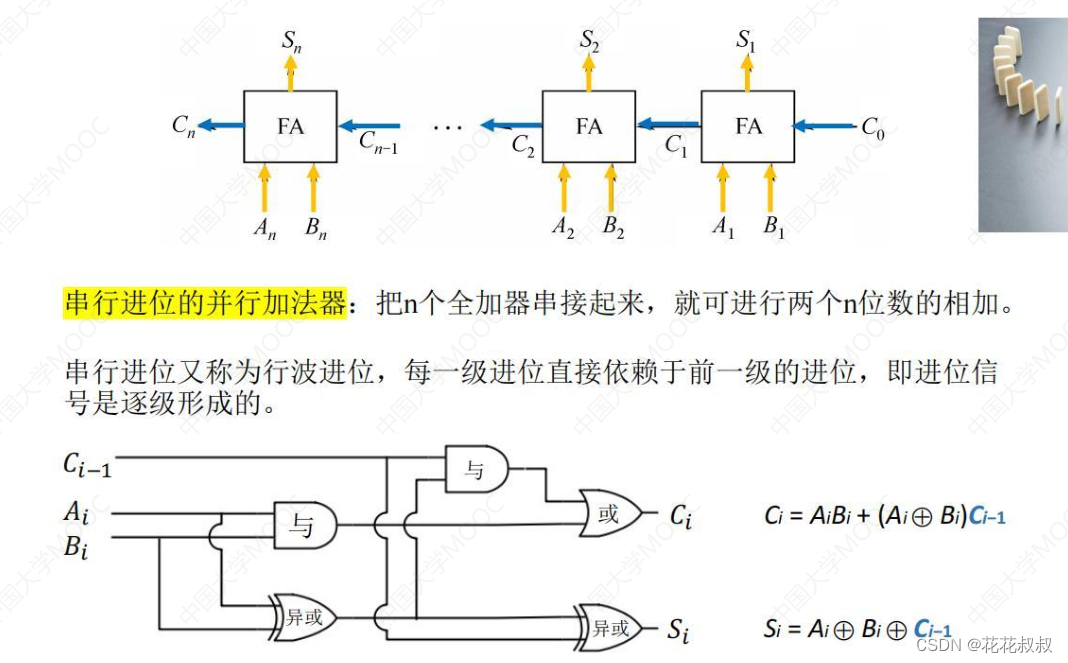

串行进位加法器

缺点就是有前后关联关系,必须有顺序。

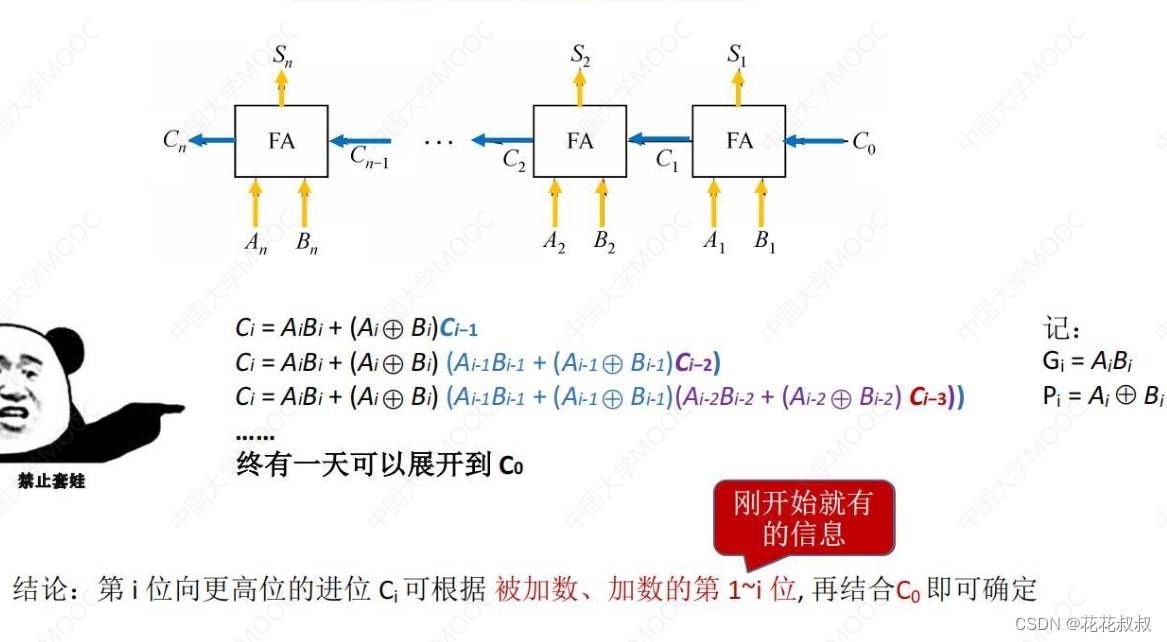

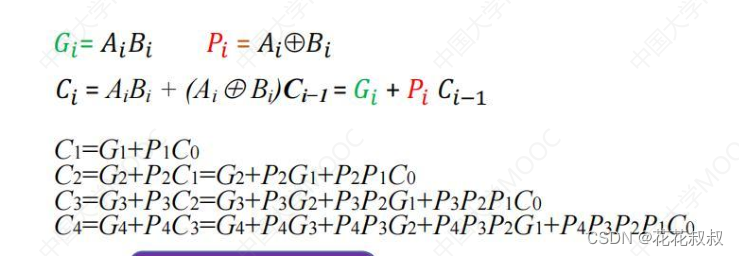

并行进位加法器

优点:Ci仅仅和Ai,Bi以及最低进位C0有关,相互之间的进位没有依赖关系。

补码加减运算器

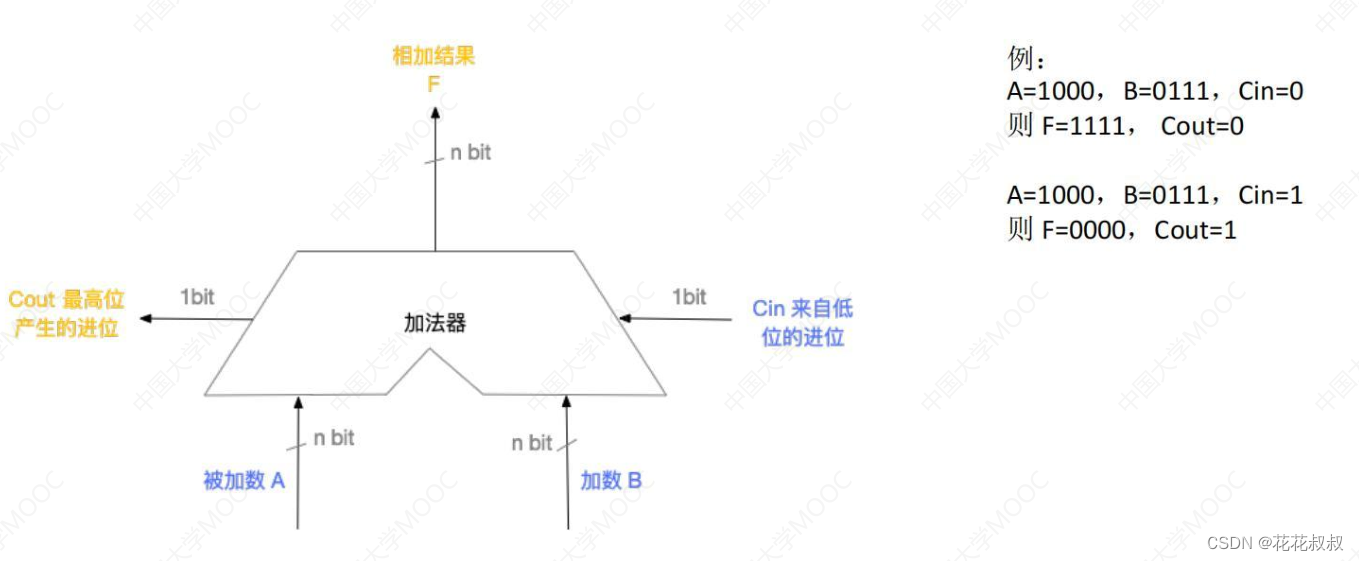

加法器原理

Cin和Count的作用就是可以对数据进行位拓展操作。

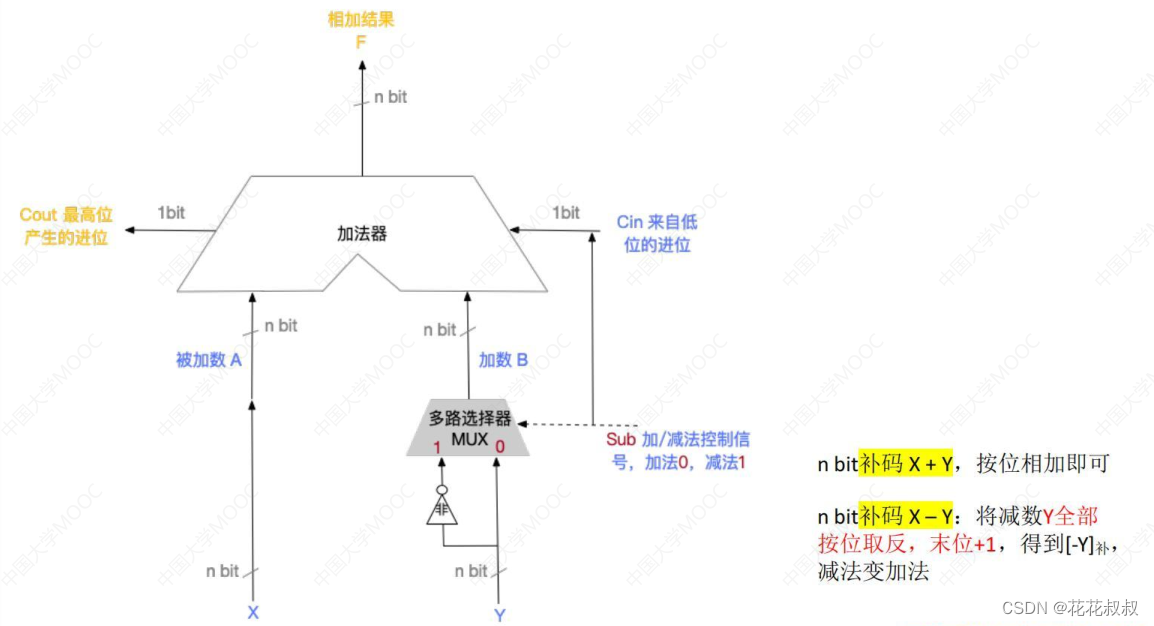

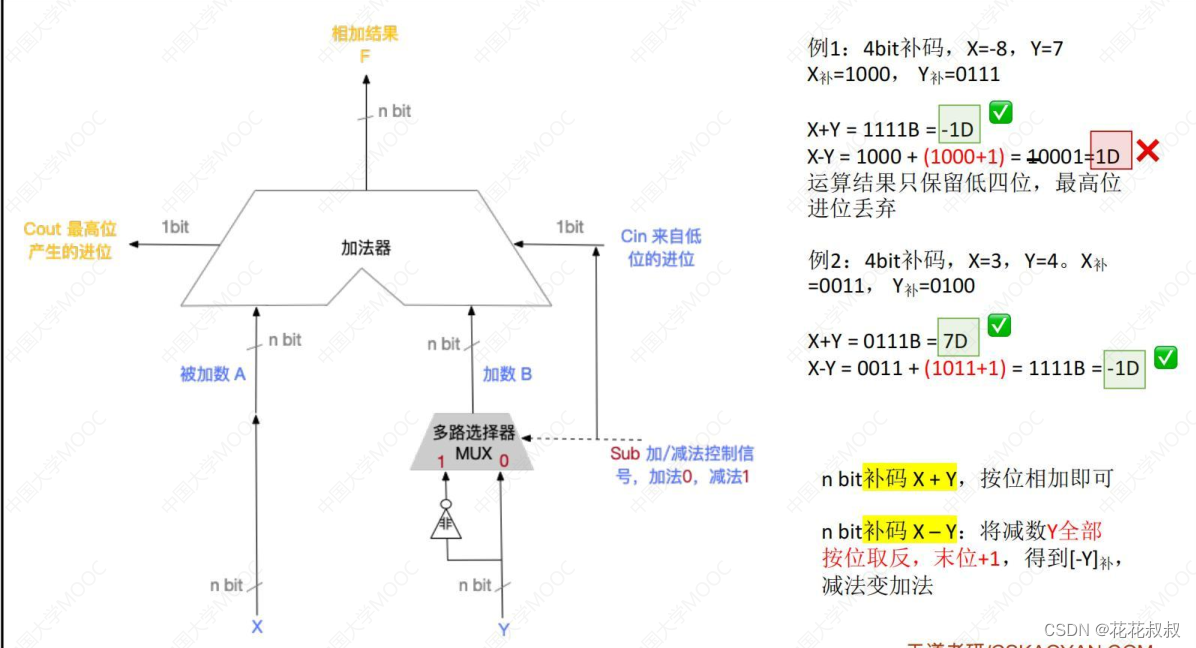

补码加法器原理

在加法器的基础上对数据进行预处理

如果补码之间是进行加法操作:X直接作为被加数,Sub的值为0,Cin值为0,之后X和Y进行加法操作。

如果补码之间是进行减法操作:X直接作为被加数,Sub的值为1,所以对Y进行取反操作,Cin的值为1,最后就是X + Y + Cin(1)的结果。

在补码加法的操作过程中会出现溢出现象,导致结果错误。

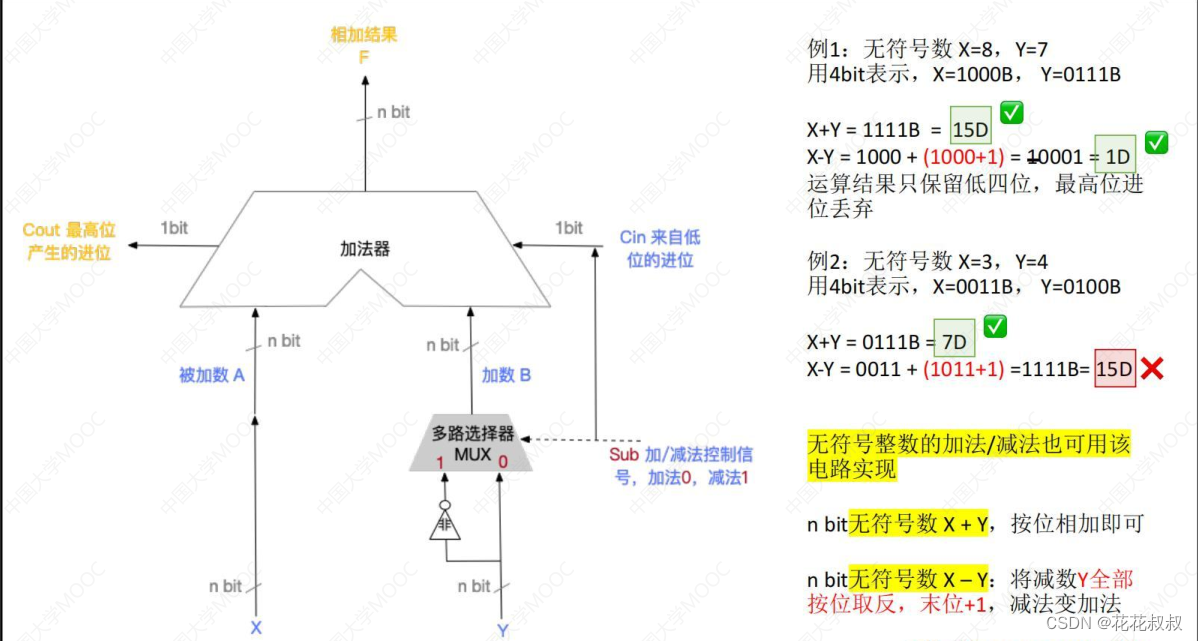

无符号整数加减法

无符号整数加减法和有符号整数的加减法用的是相同的硬件逻辑

再进行加减法的时候,也会产生溢出现象,导致结果不准确。

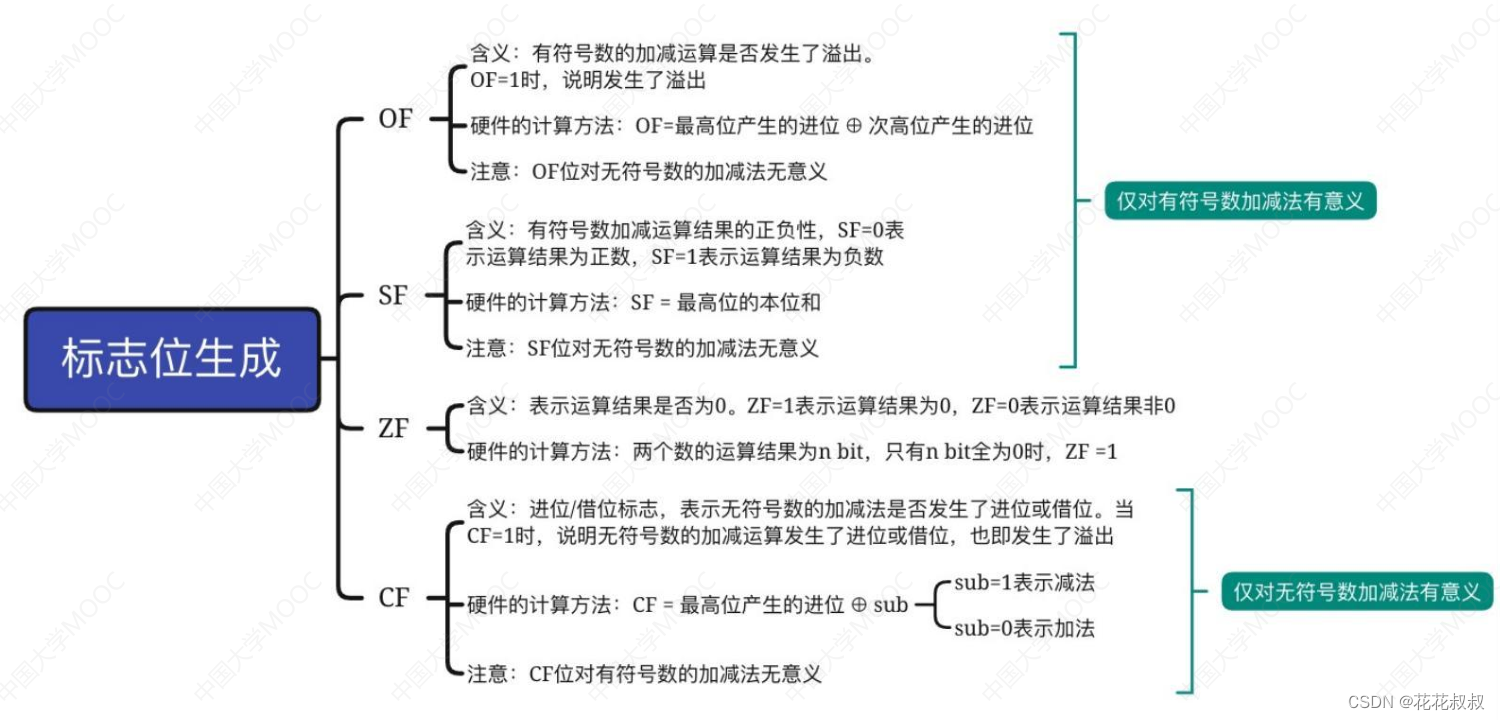

标志位的生成

判断是否有溢出现象,检查运算结果的正确性。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?