(1)cache(介于CPU和DDR)

解决CPU速度和内存速度的速度差异问题(CPU存取数据的速度非常快,而内存比较慢),内存中被CPU访问最频繁的数据和指令被复制到CPU中的缓存,CPU访问数据直接去缓存中访问就行了。

(2)cache一致性

CPU的访问数据与DDR的数据没有同步。

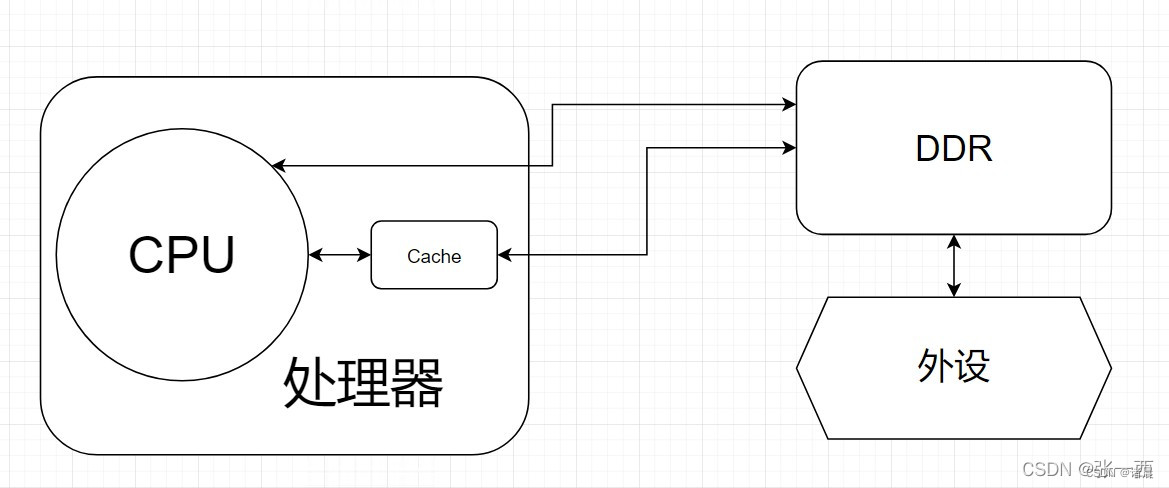

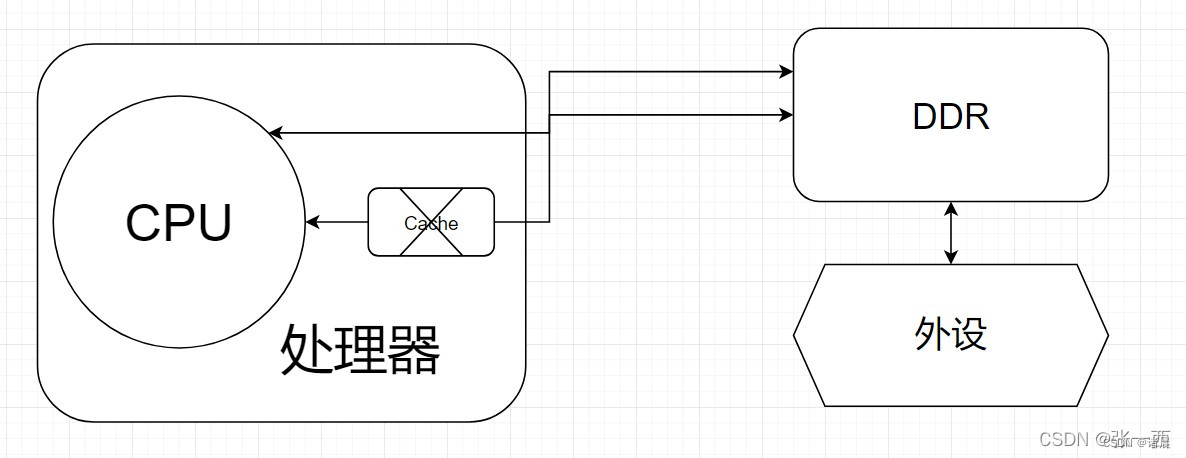

(3)CPU、Cache以及DDR之间访问关系

Cache是一个介于CPU以及DDR(DRAM)之间的一个高速缓存(一般好像是SRAM),在处理器内部,读写速度较DDR高,但是低于CPU的速度。假如没有Cache,直接访问DDR,CPU的速度远远高于DDR,那么CPU就需要等待DDR的数据到来,才能做其他事情,就会造成CPU使用效率较低。

使用Cache之后,提前将DDR的数据缓存到Cache中,如果恰好CPU访问DDR的数据在Cache中有,那么CPU拿到数据的时间将更短,处理效率将大大增加。但是同时也会造成一致性问题,即CPU的访问的数据(Cache)与DDR的数据没有同步,造成执行错误。

假设一种真实情况,CPU要访问DDR中的一块数据,那么这块数据会放在Cache中,之后DMA控制器直接将外设的数据放在DDR中,更新了刚刚的那一块CPU要访问的数据,此时CPU要获取数据进行处理,还是拿着Cache中未更新的数据(没有立马反映到DDR中),就会造成一致性问题。

(4)解决Cache一致性问题

将Cache中的数据清空,或者将DDR与Cache的数据同步。(使用CacheFlush和Cache Invalidate操作,CacheFlush把Cache里的数据清空,将Cache内容推到DDR中;而Cache Invalidate表示当场宣布Cache内容无效,需要从DDR中重新加载数据,即把数据从DDR中拉到Cache中。)

1694

1694

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?