原理

加法

101101

+ 1

1011100

减法

101100

- 1

101011

加法:计数每+1

最低位:必须翻转1次

第i位:只有当低于i的位全为1时翻转

同理减法:计数每-1

最低位:必须翻转1次

第i位:只有当低于i的位全为0时翻转

翻转实现方式:T触发器

控制方式:

1)控制input:恒有clk,T=0保持,T=1翻转;(同步counter)

2)控制clk:T==1,无clk保持,有clk翻转,(异步counter)

一、同步计数器

1.四位二进制

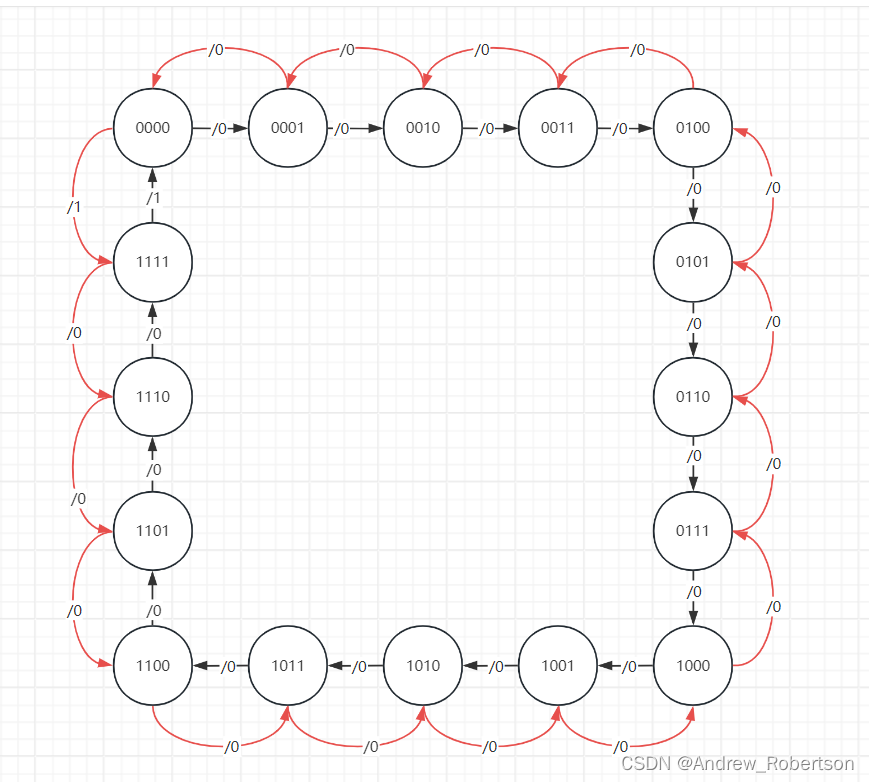

状态转换图:

加法计数器(黑色);减法计数器(红色);可逆计数器(黑+红)。

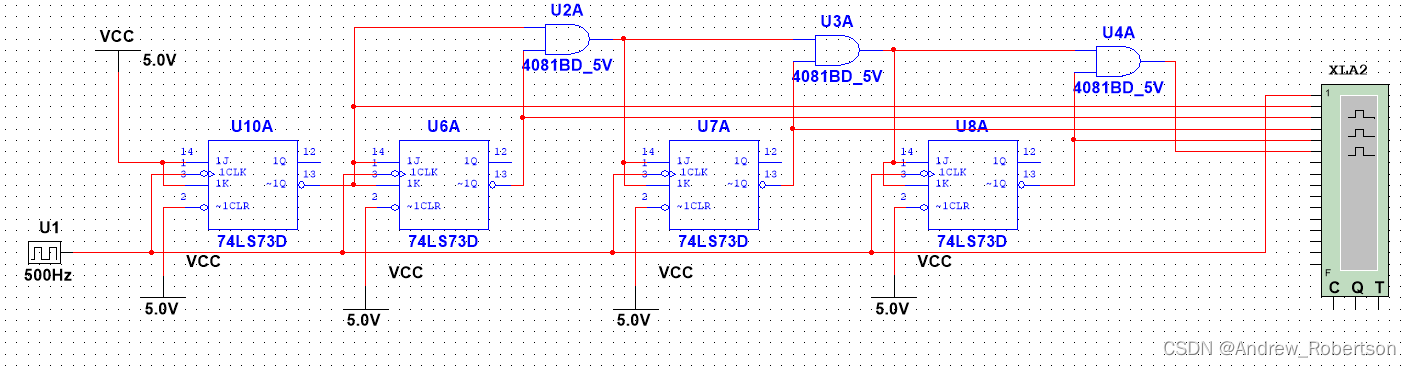

加法计数器

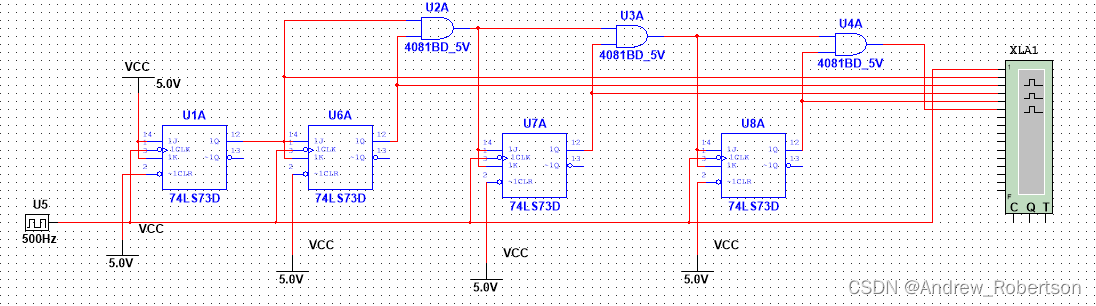

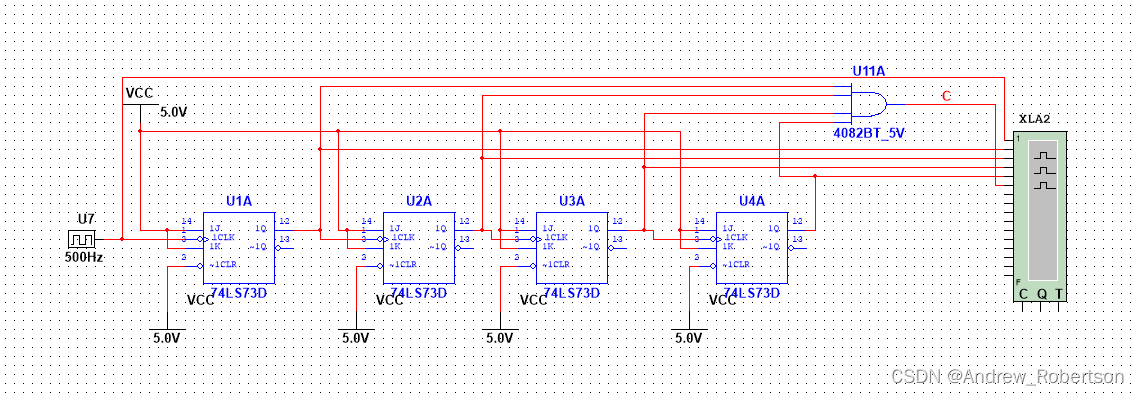

电路图

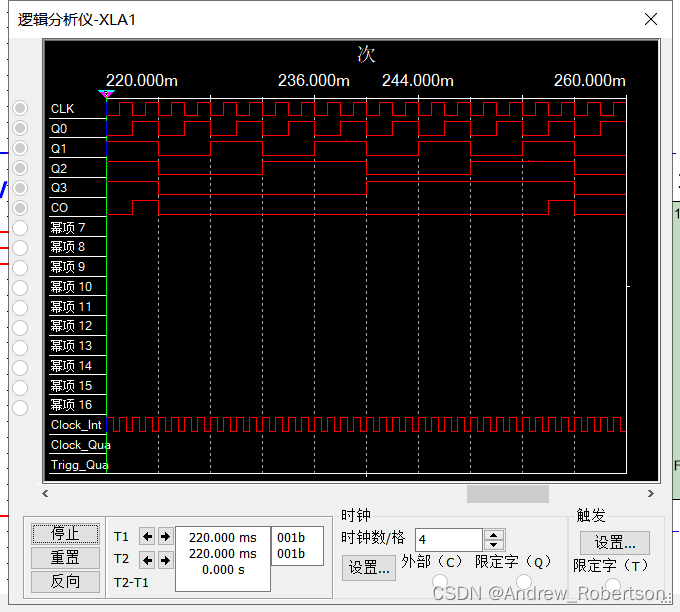

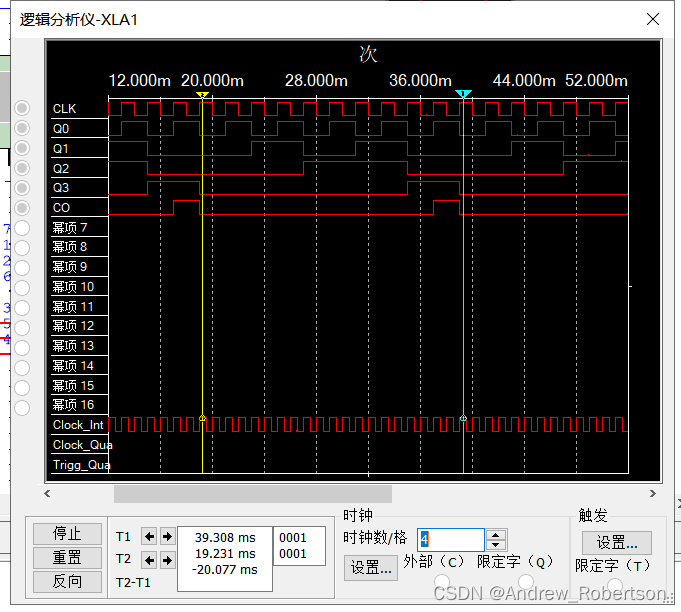

clk=500Hz,逻辑分析仪 采样频率1kHz(下同)

驱动/激励方程:

T0=1;

T1=Q0;

T2=Q1Q0;

T3=Q2Q1Q0;

代入T触发器特性方程:Q*=T⊕Q

状态方程:

Q0*=Q';

Q1*=Q0⊕Q1;

Q2*=(Q1Q0)⊕Q2;

Q3*=(Q2Q1Q0)⊕Q3;

输出方程:CO=Q3Q2Q1Q0

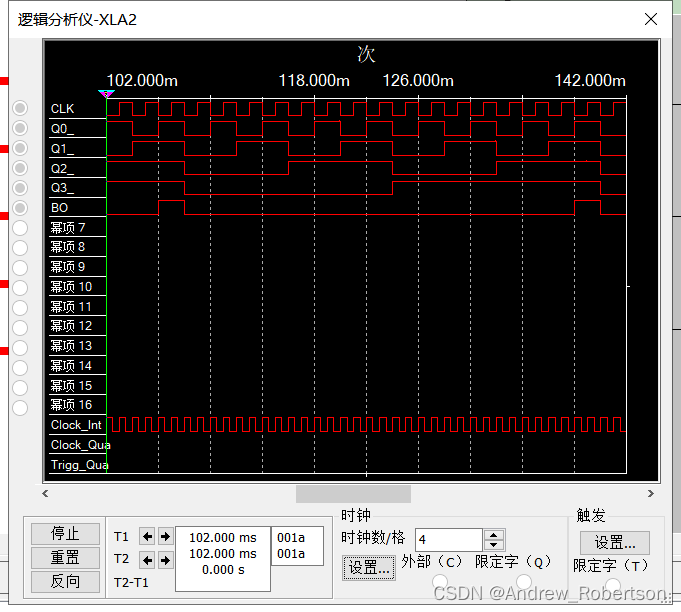

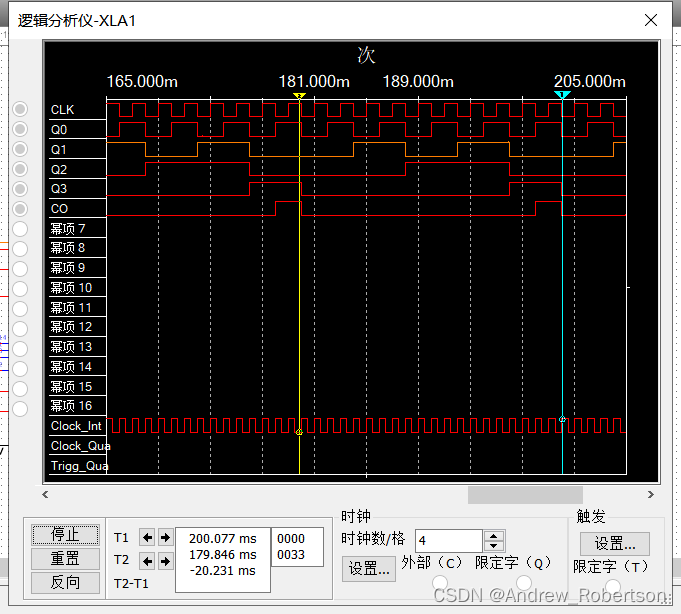

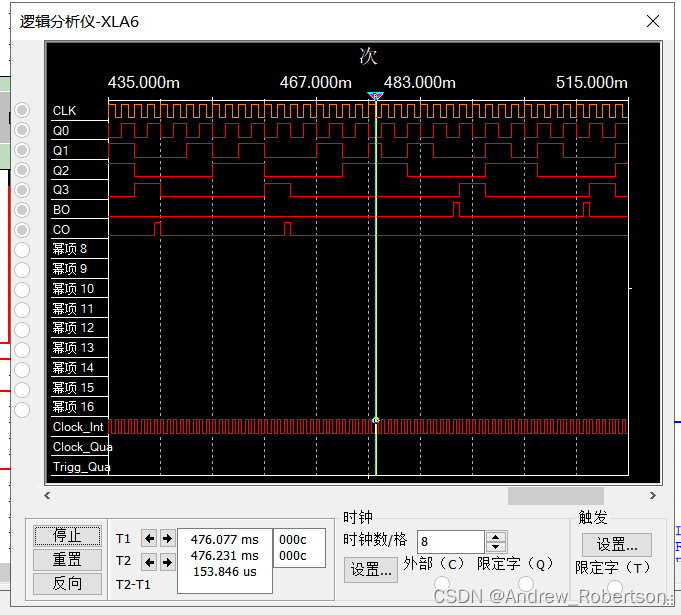

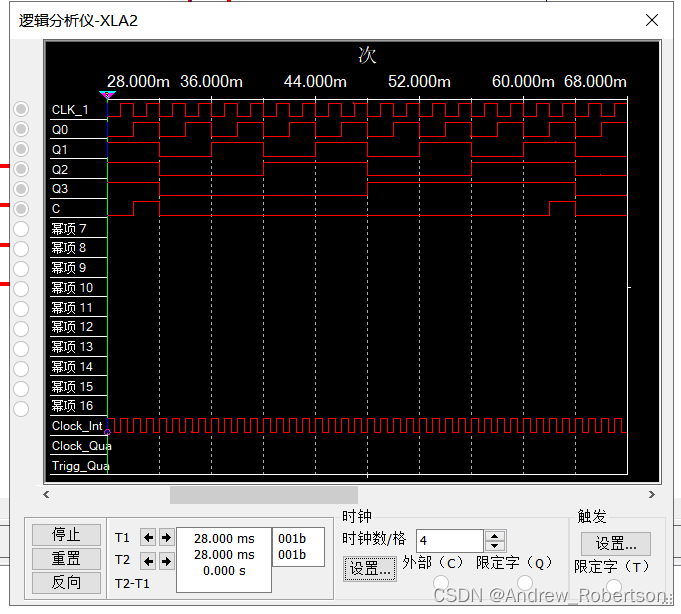

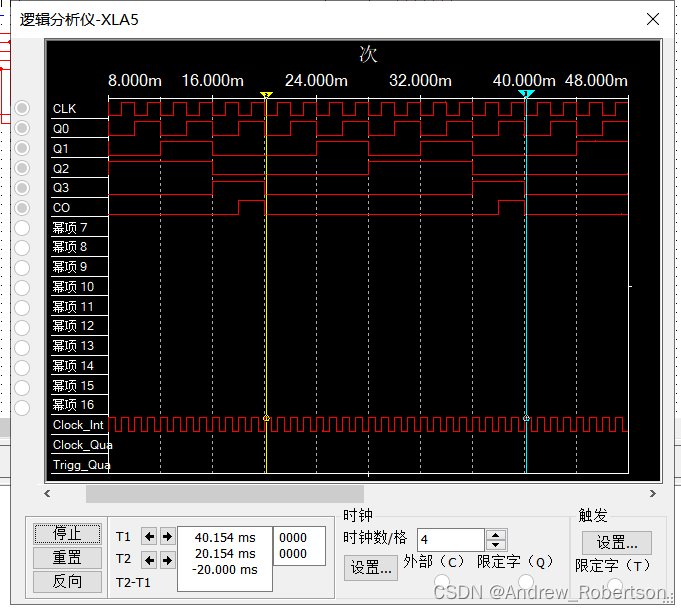

仿真波形

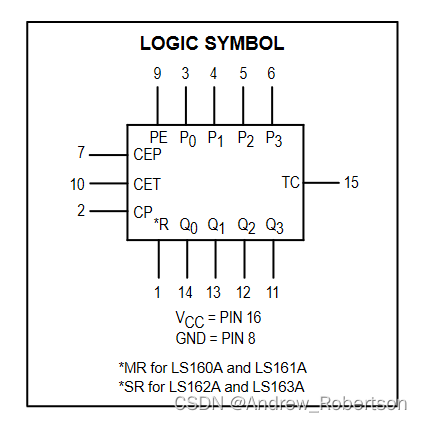

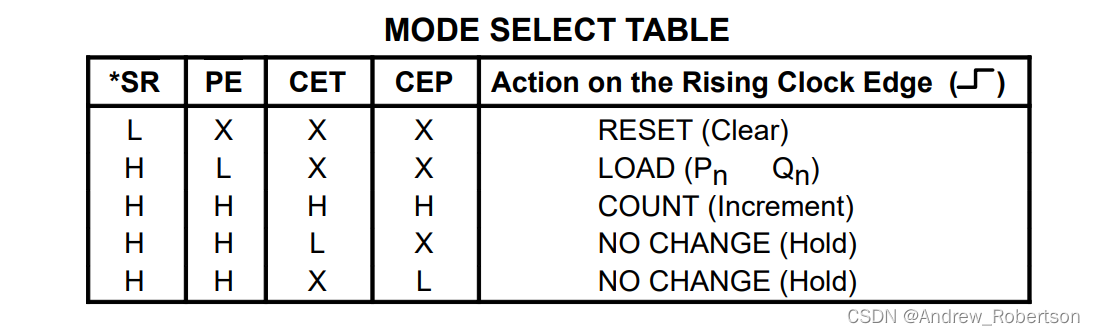

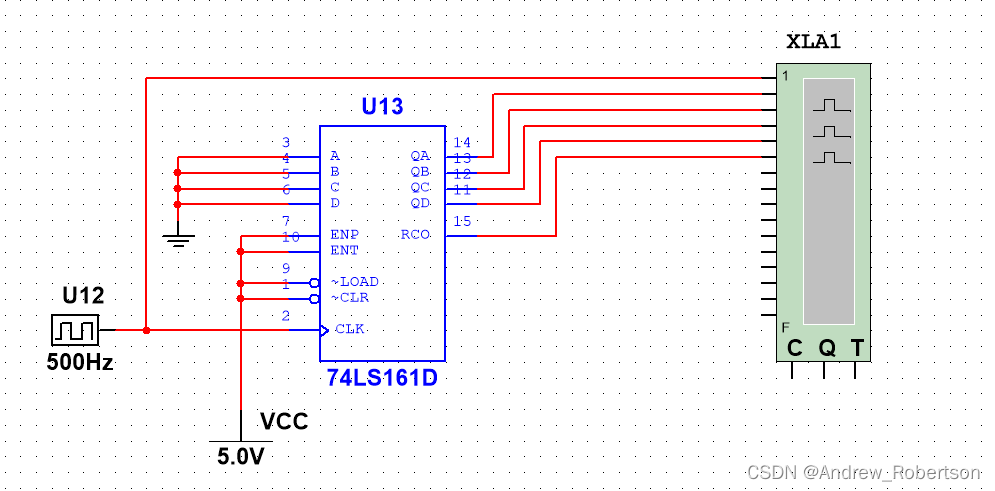

相关芯片 74LS161

上升沿触发,

使能端:PE

清零:*SR=~CLR;

控制端:CEP=ENP,CET=ENT;

进位输出:TC

同步置数:~LOAD(仿真芯片上)

真值表

电路图

仿真波形同上。

减法计数器

同理,驱动/激励方程:

T0=1;

T1=Q0';

T2=Q1'Q0';

T3=Q2'Q1'Q0';

代入T触发器特性方程:Q*=T⊕Q

状态方程:

Q0*=Q';

Q1*=Q0'⊕Q1;

Q2*=(Q1'Q0')⊕Q2;

Q3*=(Q2'Q1'Q0')⊕Q3;

输出方程:CO=Q3'Q2'Q1'Q0'

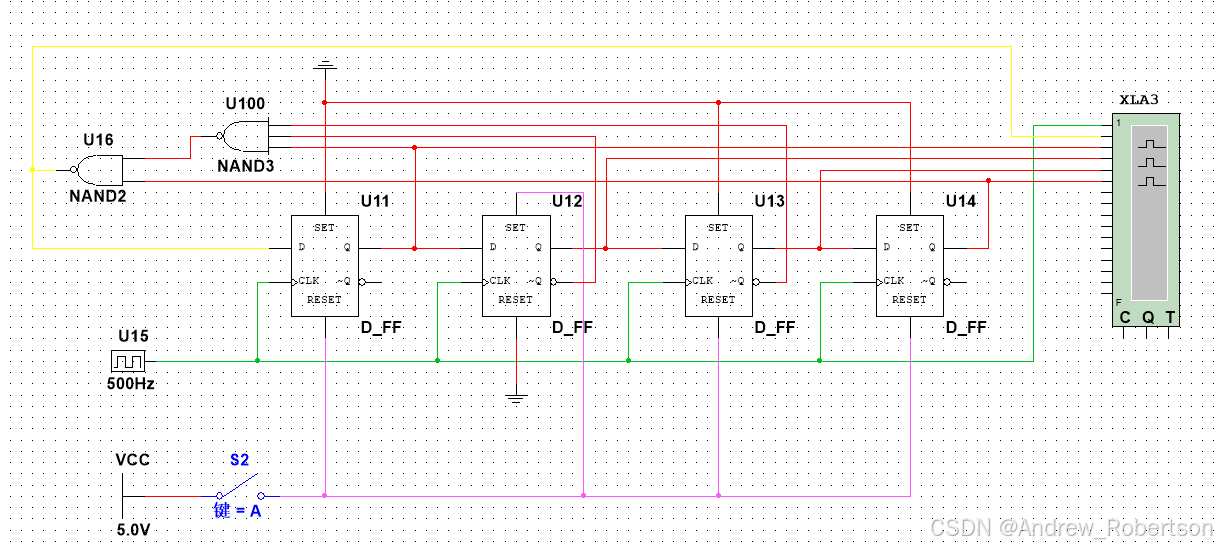

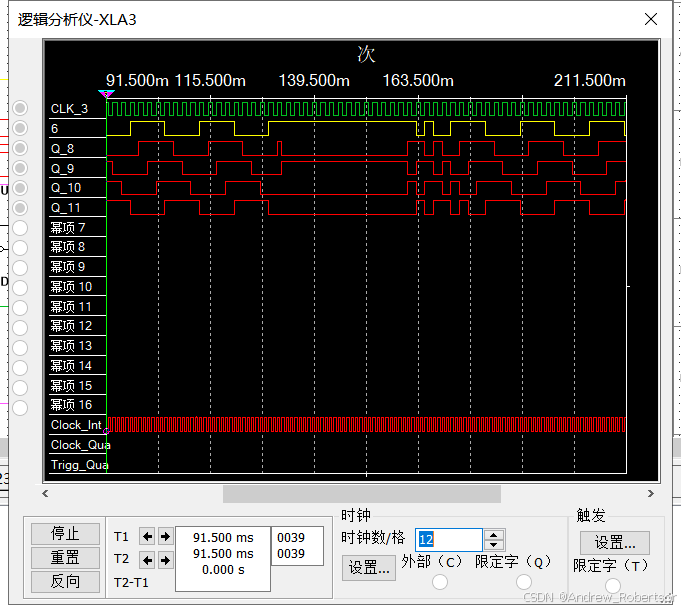

电路图

仿真波形

可逆计数器

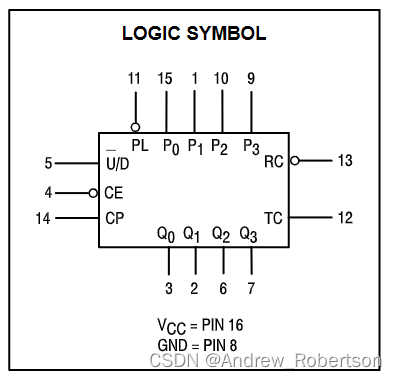

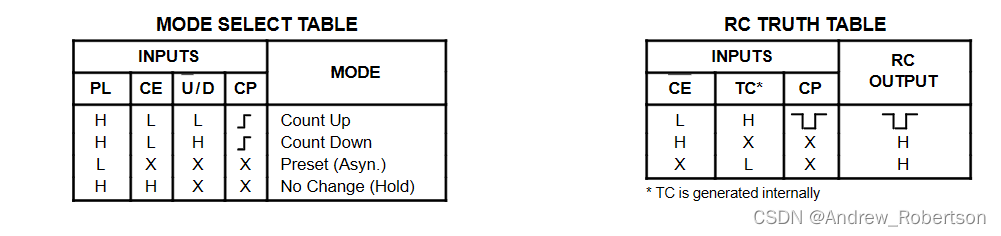

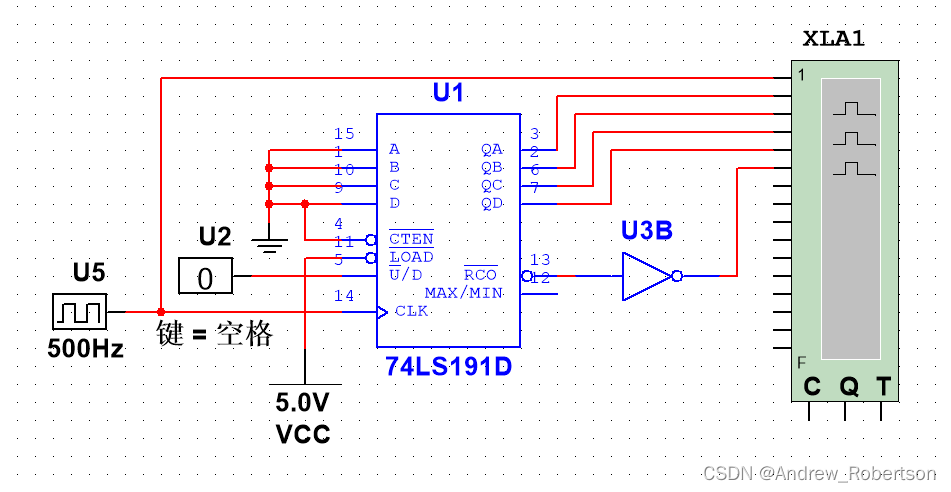

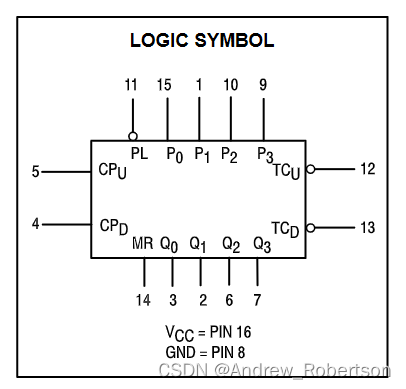

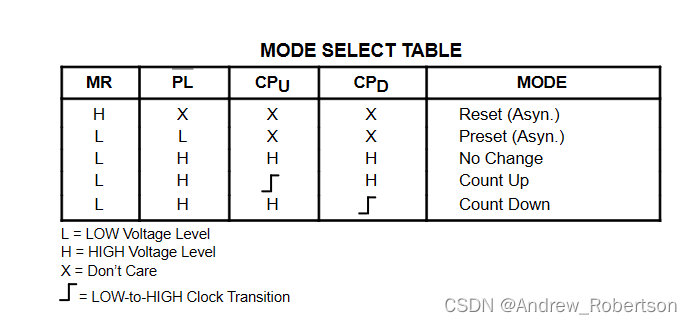

(1)74LS191(单CLK,UP-DOWN COUNTER)

电路图

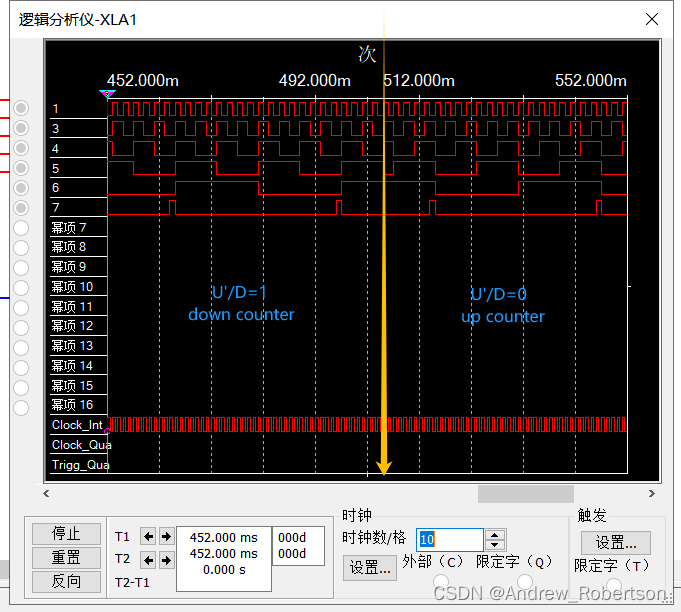

波形图

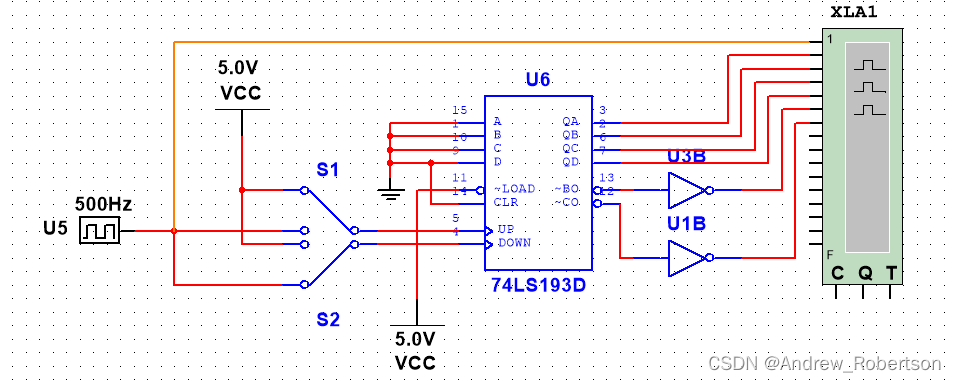

(2)74LS193(双CLK,UP-DOWN COUNTER)

电路图

波形

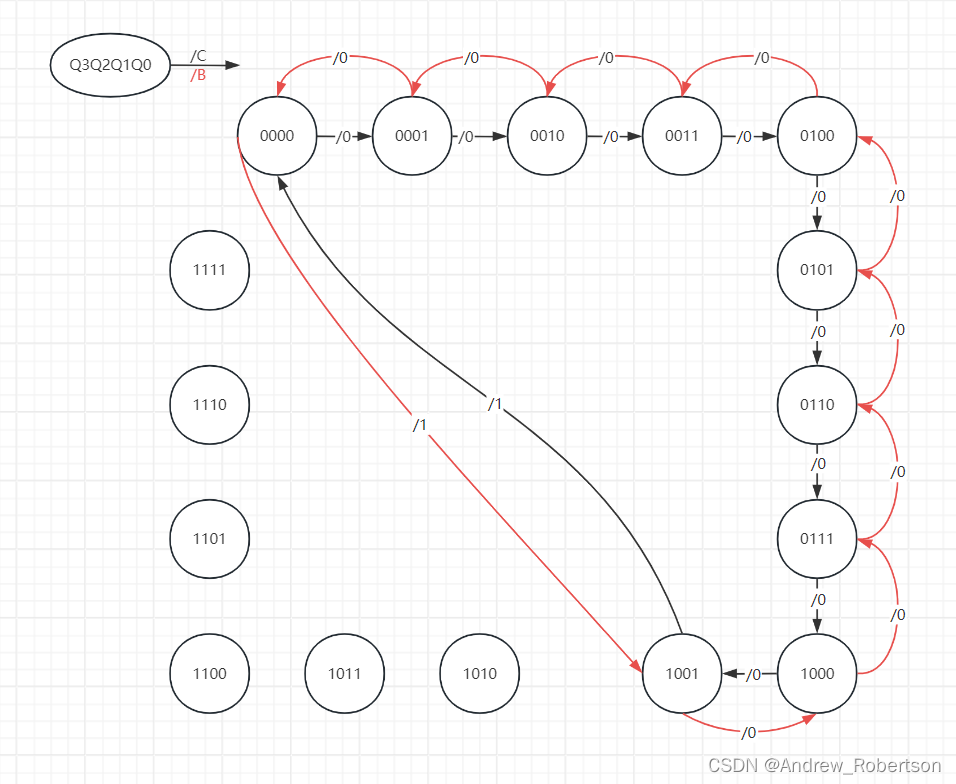

2.十进制counter

状态转换图

加法计数时,1001次态为0000,并输出CO=1;减法同理。

1010-1111为无效状态。

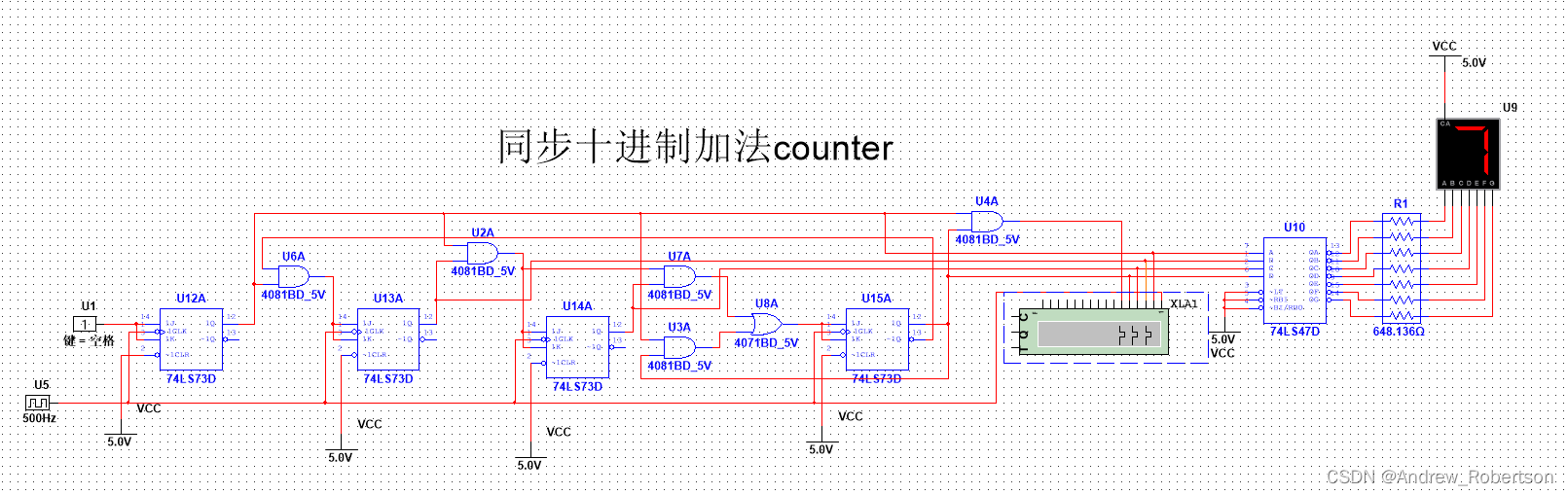

(1)T触发器电路

a.加法

驱动/激励方程:

T0=1;

T1=Q3'Q0;

T2=Q1Q0;

T3=Q2Q1Q0+Q3Q0;

代入T触发器特性方程:Q*=T⊕Q

状态方程:

Q0*=Q';

Q1*=(Q3'Q0)⊕Q1;

Q2*=(Q1Q0)⊕Q2;

Q3*=(Q2Q1Q0+Q3Q0)⊕Q3;

输出方程:CO=Q3Q0

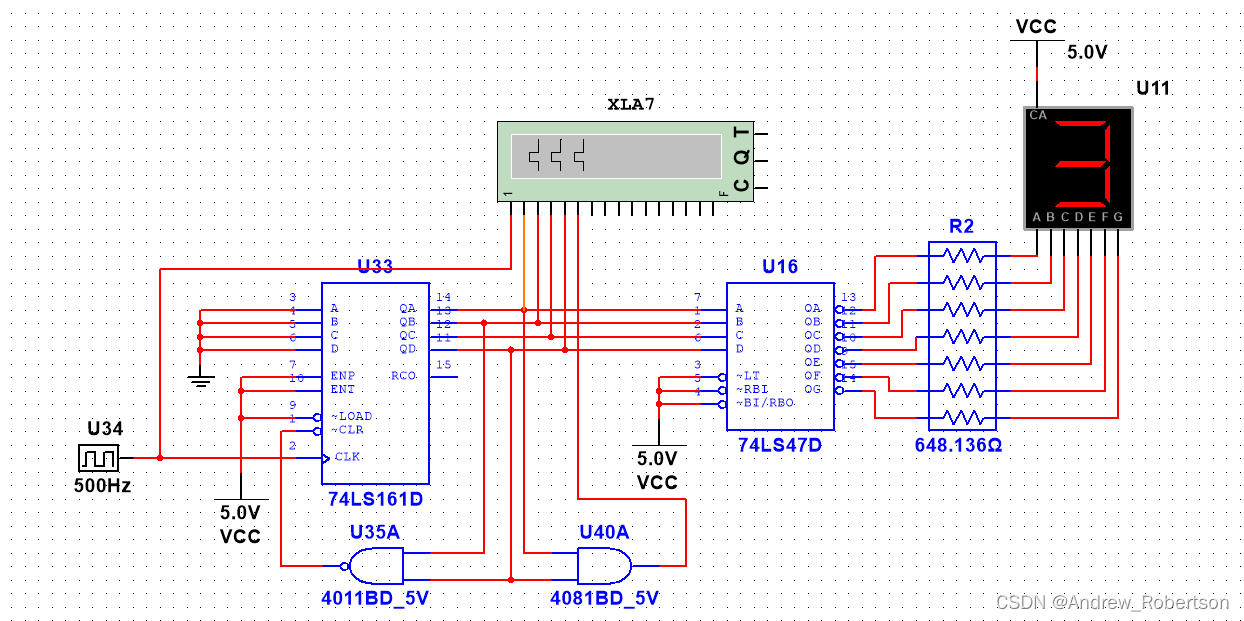

电路

波形

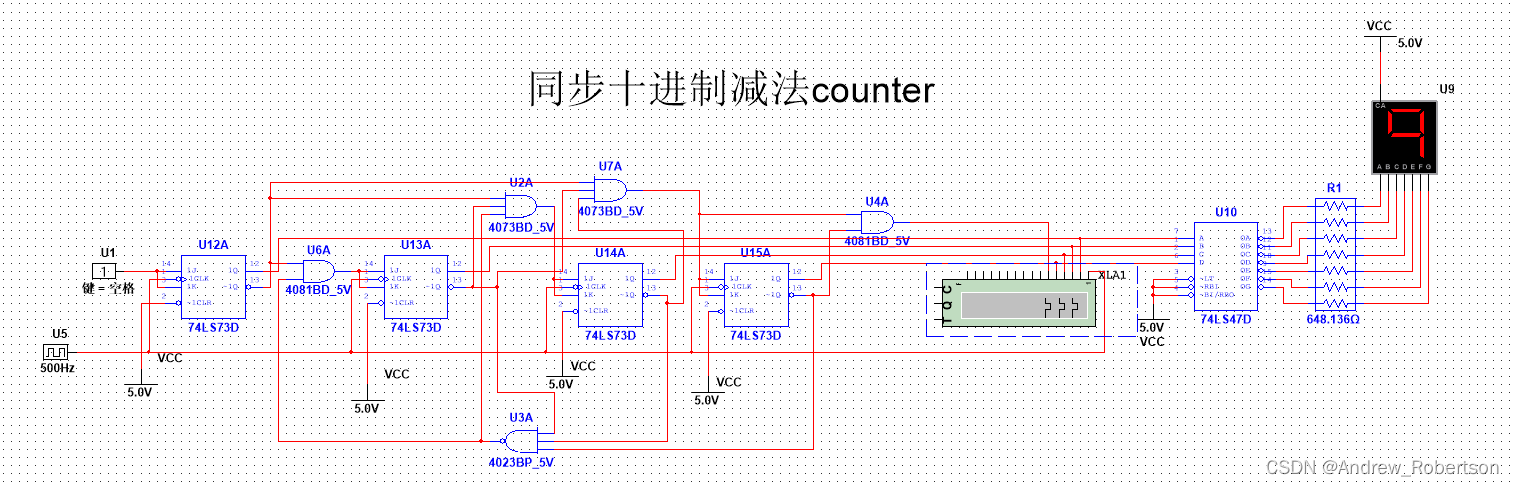

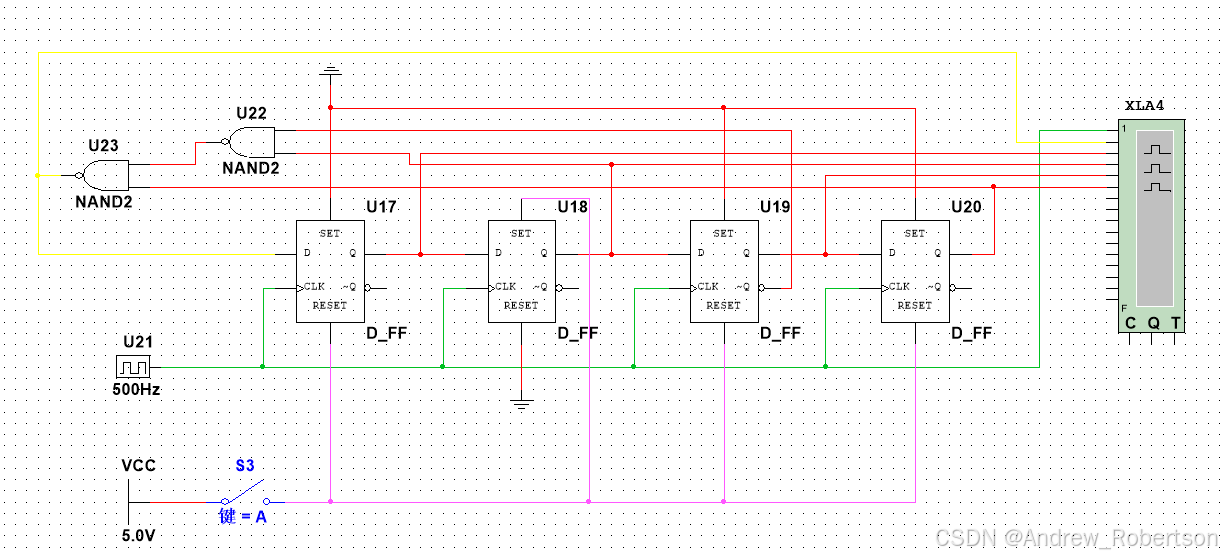

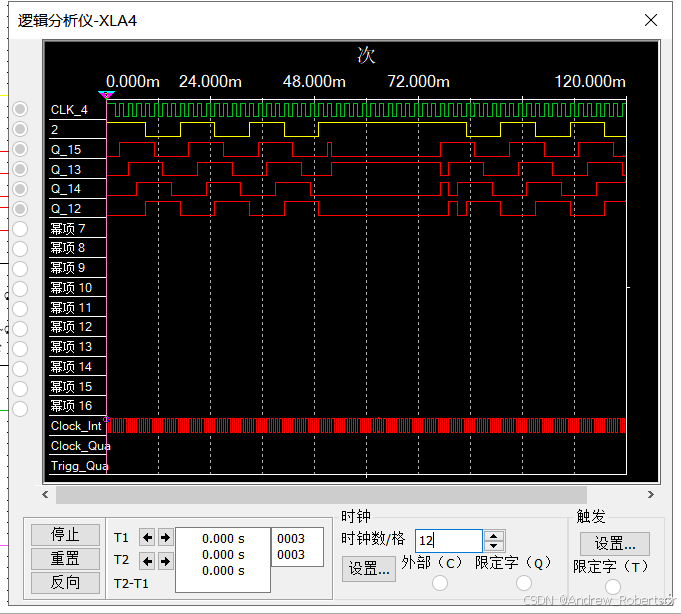

b.减法

驱动/激励方程:

T0=1;

T1=Q0'(Q3'Q2'Q1')';

T2=Q1'Q0'(Q3'Q2'Q1')';

T3=Q2'Q1'Q0'

同理状态方程代入即可,

输出方程BO=Q3'Q2'Q1'Q0'

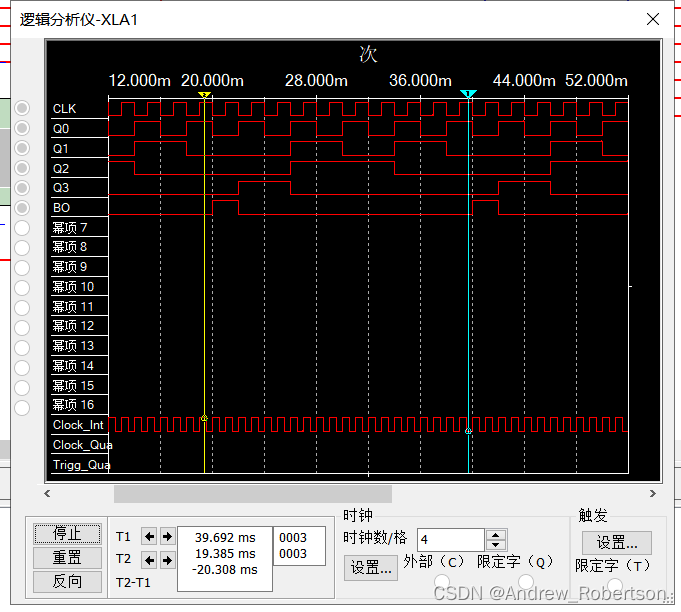

波形

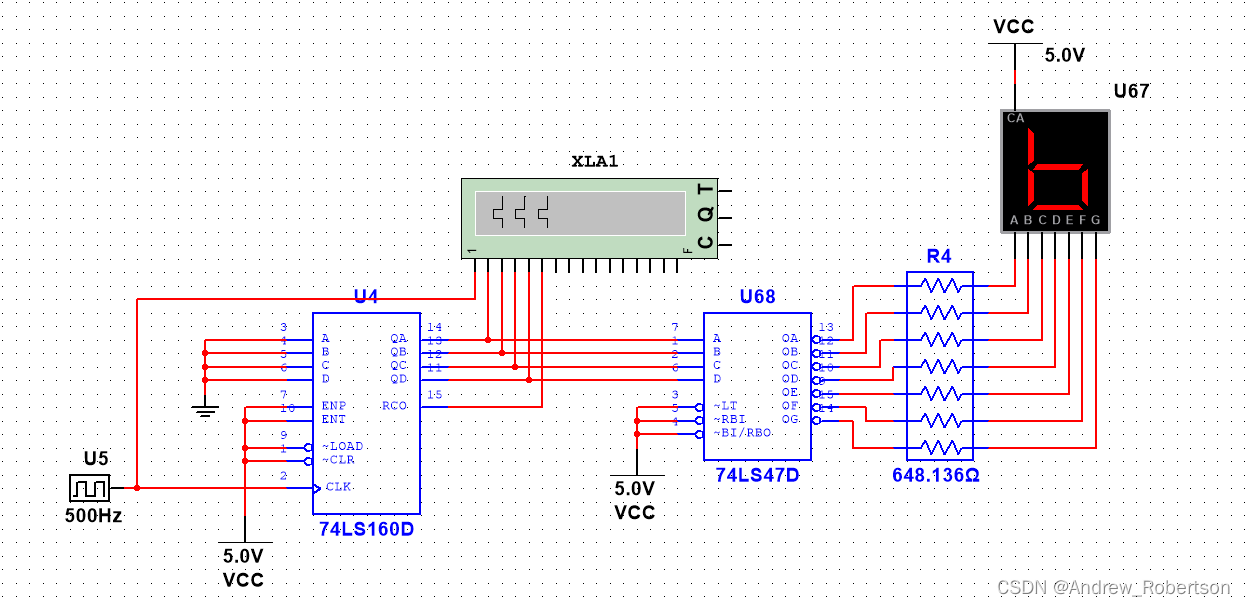

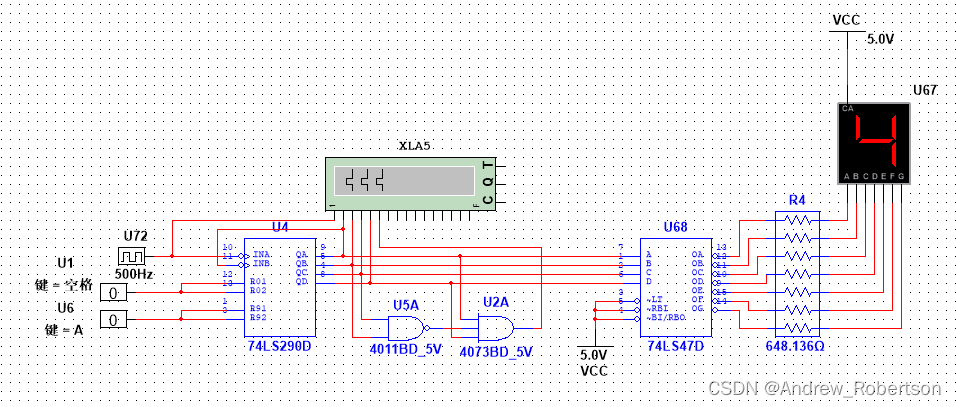

(2)同步十进制芯片

- 74LS160 同步十进制加法计数器

- 74LS190 单时钟可逆十进制计数器

- 74LS192 双时钟可逆十进制计数器

功能分别于74LS161、74LS191、74LS193相同,进制不同

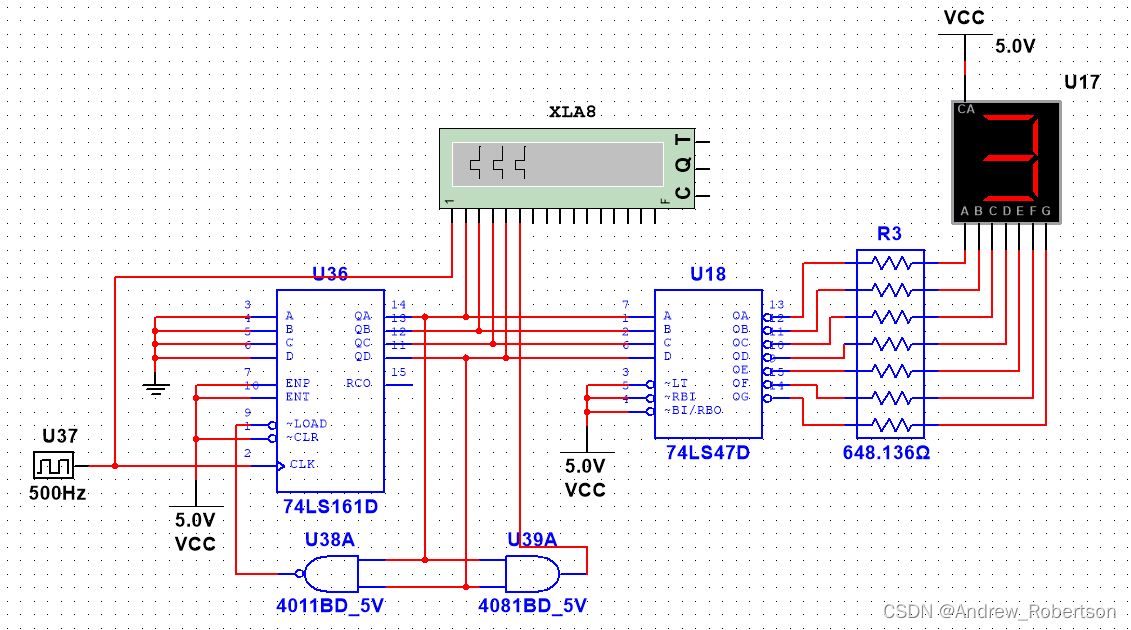

1.74LS160

电路

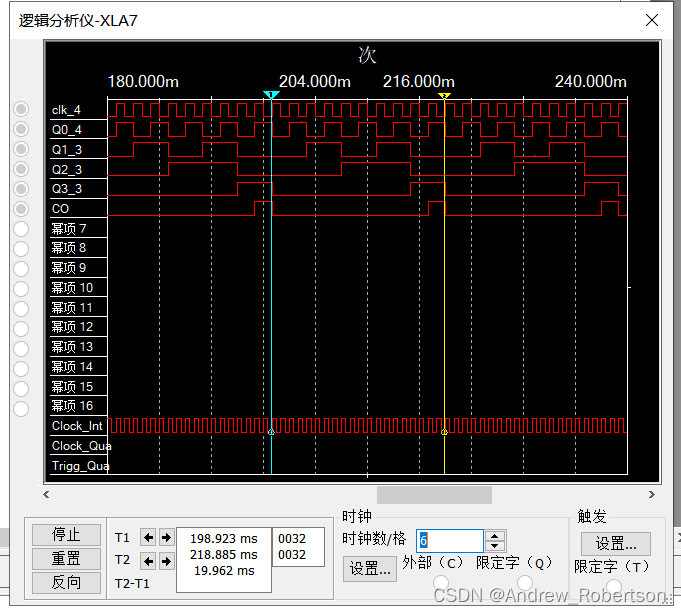

波形

2.74LS190

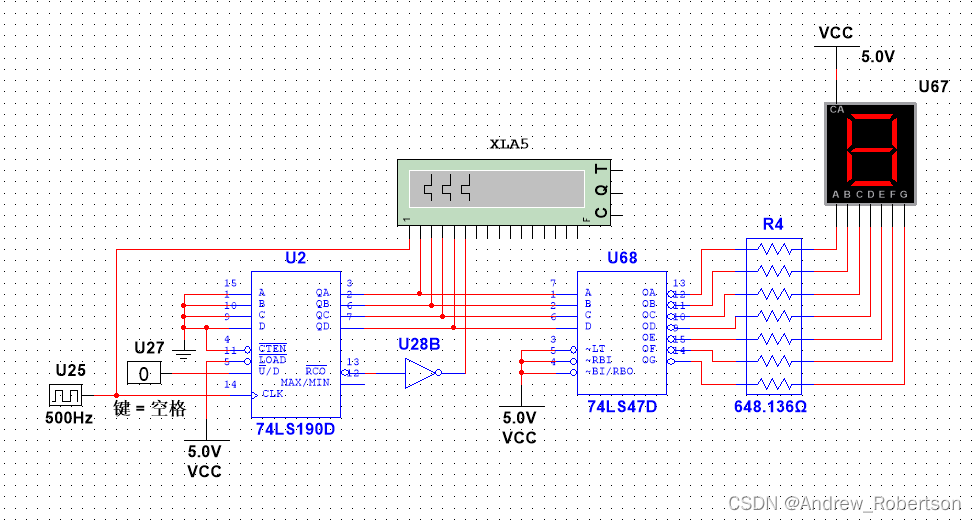

电路

波形图,测量线左侧u’/d=0加法计数,右侧u’/d=0减法计数

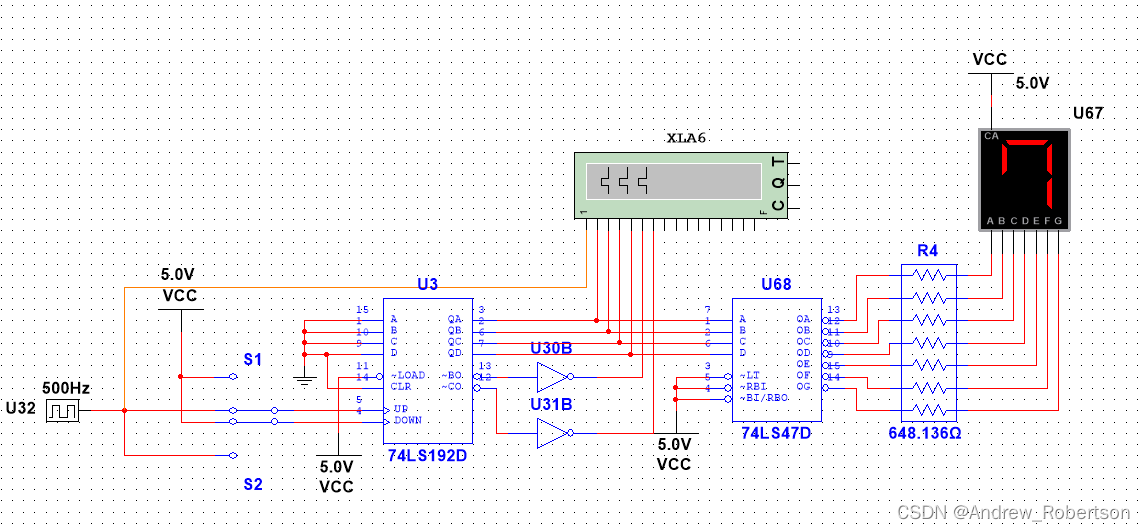

3.74LS192

电路

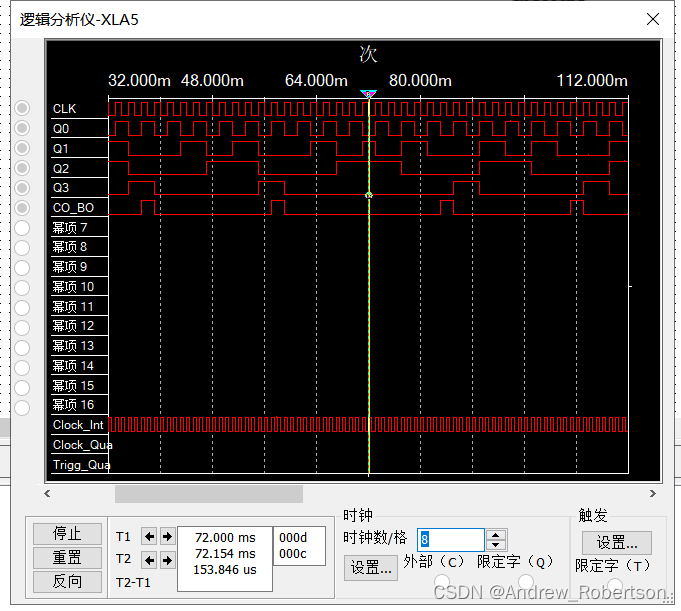

波形图,测量线左侧加法计数,右侧减法计数

(3)反馈清零法

用于有清零端(CR/~CLR)的计数器,在Q=1010时清零,但是存在时间极短,忽略1010,

即Q=1001+1=1010接到清零端,

实际上产生的进位信号CO=1001

电路图

仿真

(4)反馈置数法

用于有置数端(PE/LD)的计数器,

在Q=1001时置为ABCD,即Q=1001接到置数端,

CO=1001

电路图

仿真

二、异步计数器

1.异步四位二进制计数器

缺点:到Q3会有4tpd的延时,工作速度:同步>异步

波形

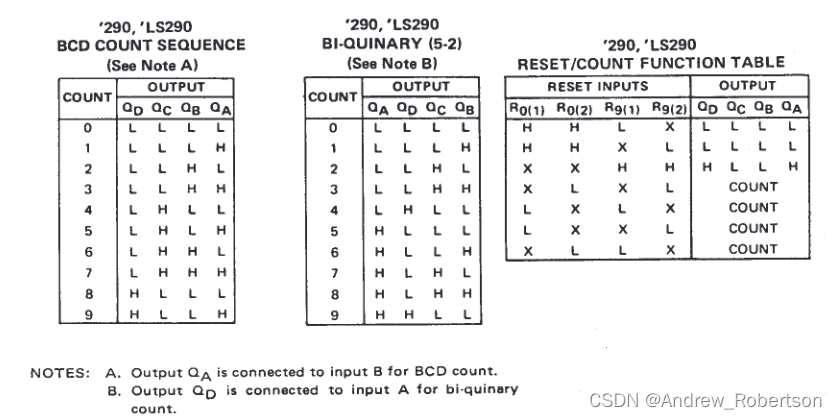

2.二-五-十进制异步计数器 74LS290

真值表

电路

波形

三、移位寄存器型计数器

(移位寄存器 + 反馈电路) --> 计数器

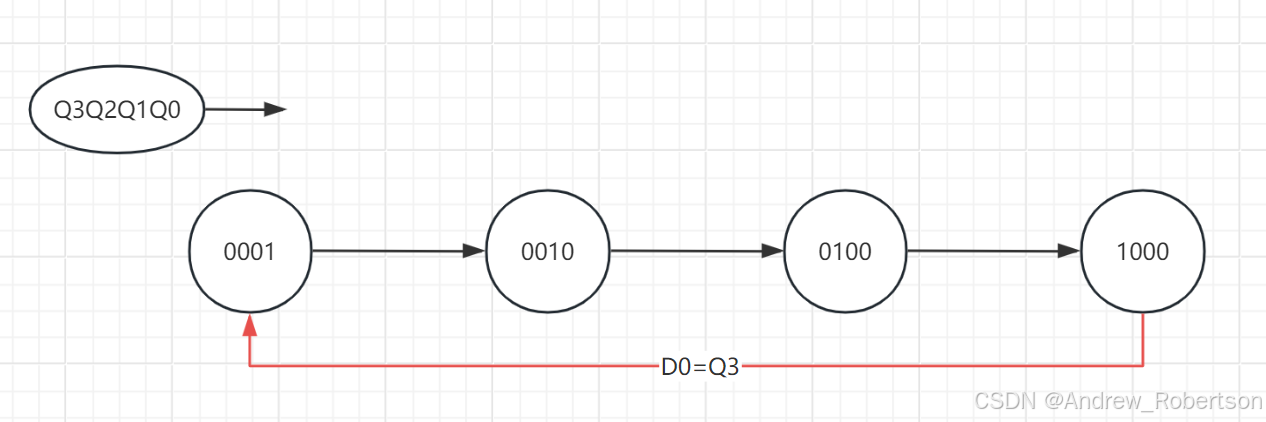

1.环形计数器

结构:移位寄存器 + 反馈电路 D0=Q3

data : LSB --> MSB --(feedback)--> LSB --> MSB ..... 形成循环,成为模4计数器

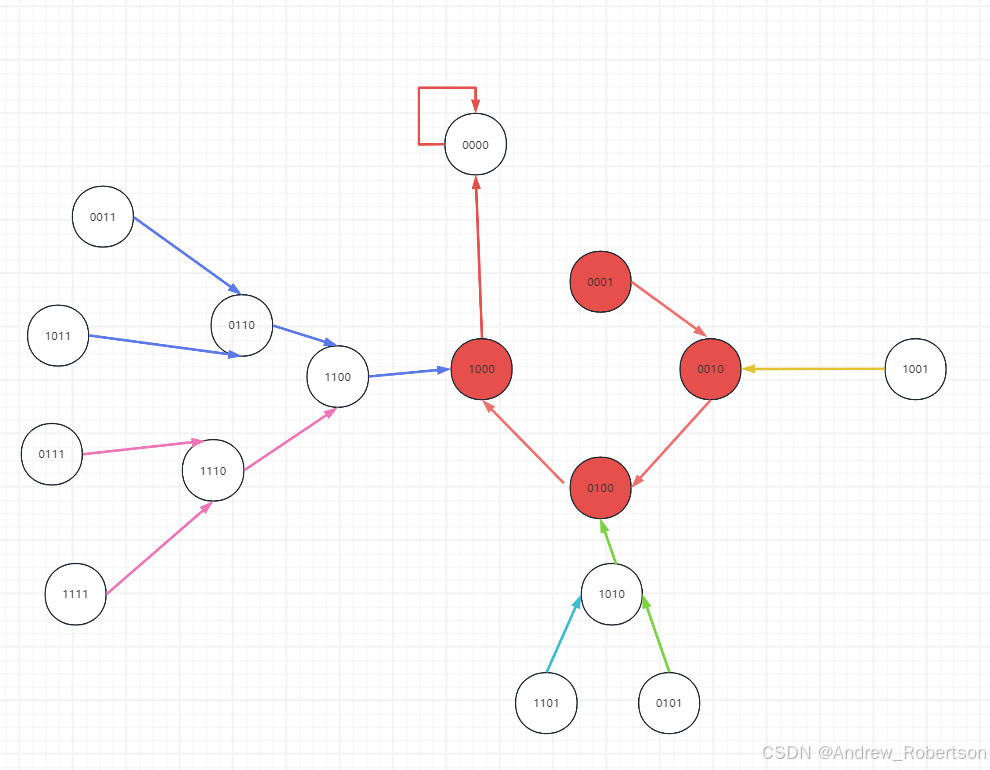

状态转换图:

需要提前给Q3Q2Q1[复位端RESET] & Q0[置数端SET] 施加高电平脉冲(器件端口为高电平触发),

模拟出初态 Q3Q2Q1Q0 = 0001 ,周期结束后可重复能形成循环,

缺点:a.需提前配置置数端和复位端,该电路无法自启动

b.抗干扰能力差,若Q3Q2Q1Q0跳出循环,该电路无法回到循环,

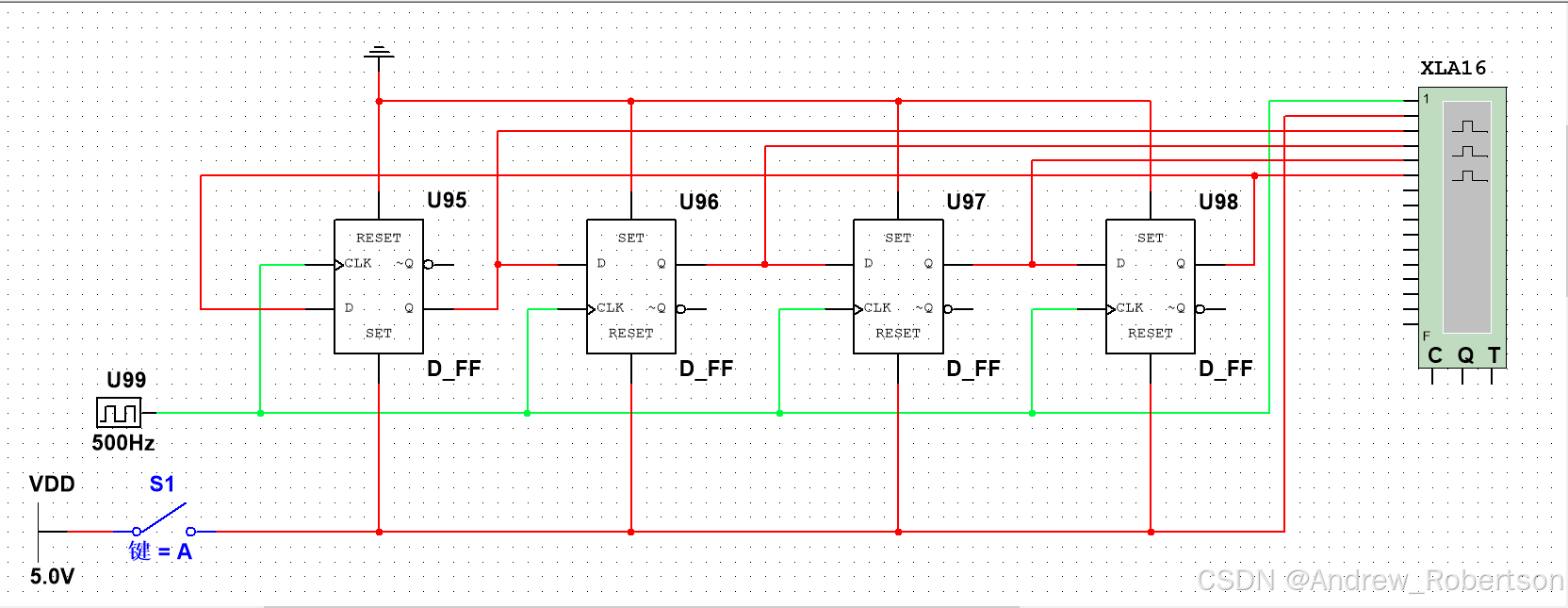

电路图如下:

状态方程:Q3*=D3=Q2, Q2*=D2=Q1, Q1*=D1=Q0, Q0*=D0=Q3,

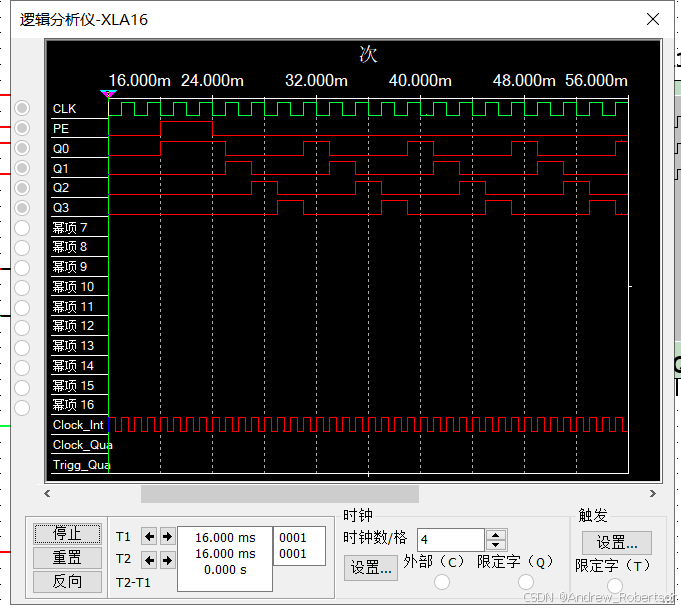

逻辑分析仪仿真图如下:(PE端施加高电平脉冲)

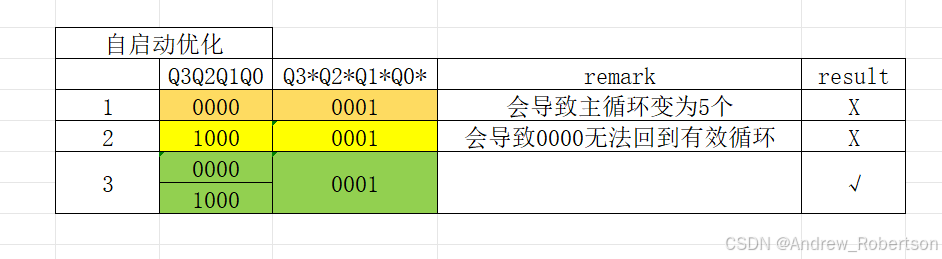

自启动优化:

将Q3Q2Q1Q0所有状态加入状态转换, 将无效循环转换为有效循环。

初始移位寄存器全部状态转换如下:

此时有3个优化选择:

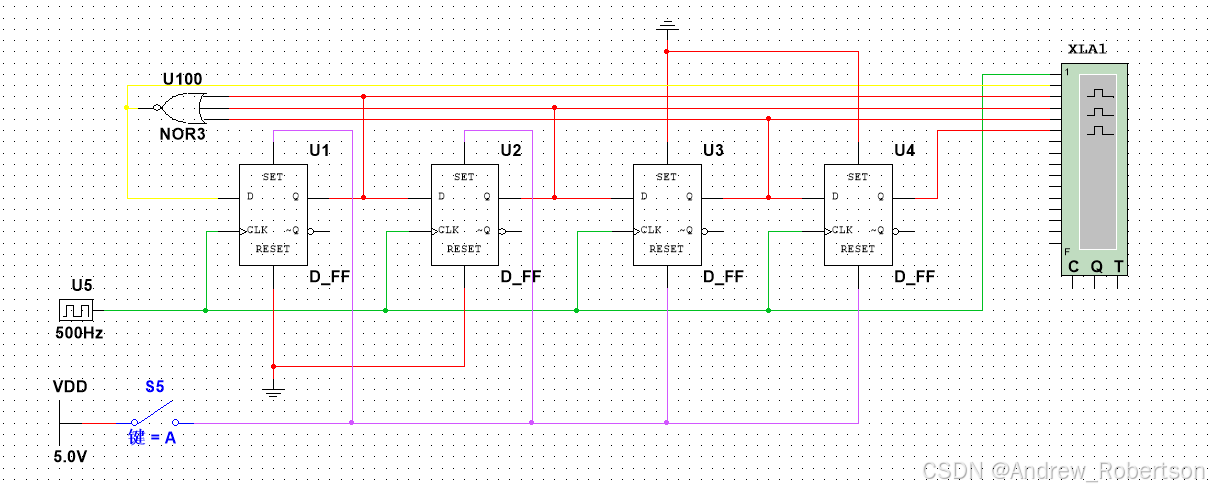

所以D0 = Q3*Q2*Q1*Q0*= Q3'Q2'Q1'Q0'+Q3Q2'Q1'Q0' = Q2'Q1'Q0' = (Q2+Q1+Q0)' (或非式)

自启动优化:移位寄存器 + 反馈电路 D0=(Q0+Q1+Q2)'

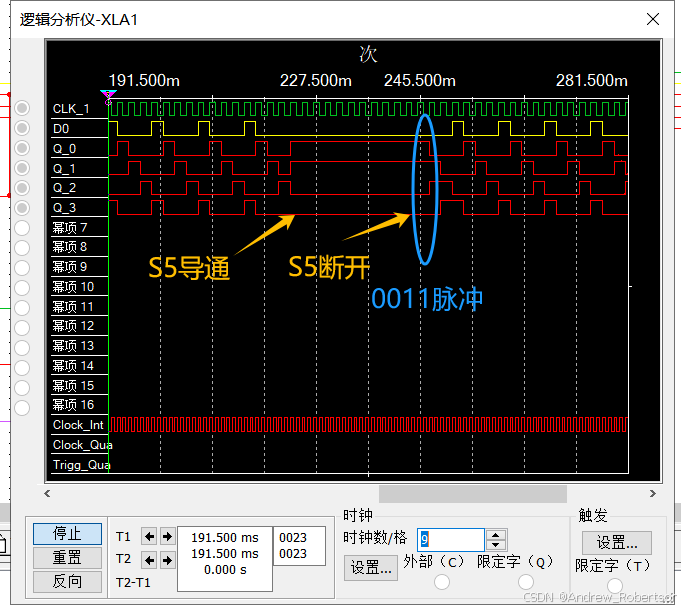

电路图:VDD部分用来模拟干扰脉冲0011

波形:由波形图可见,受到0011干扰脉冲,经过3个周期后可自恢复

2.扭环形计数器(Johnson Counter)

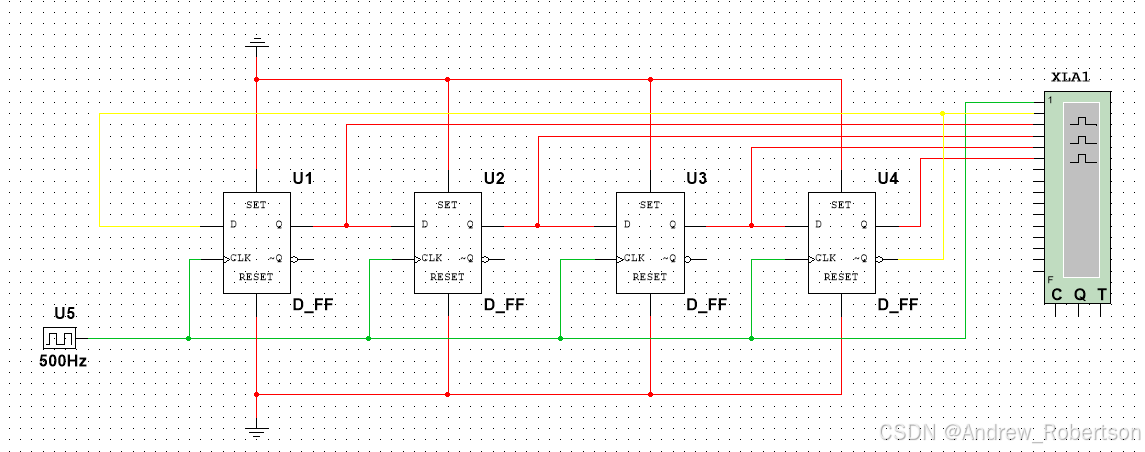

结构:移位寄存器 + 反馈电路 D0=Q3'

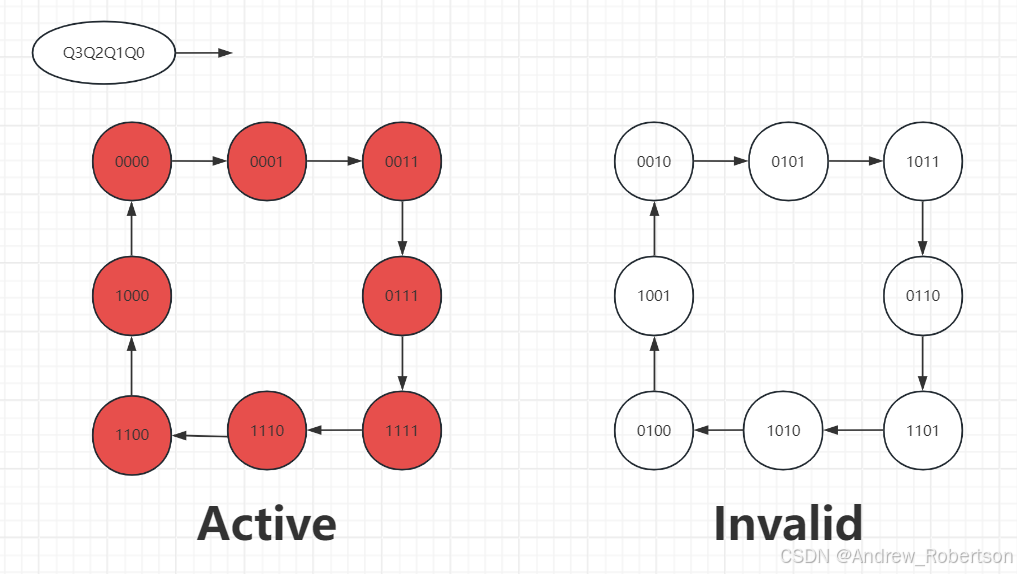

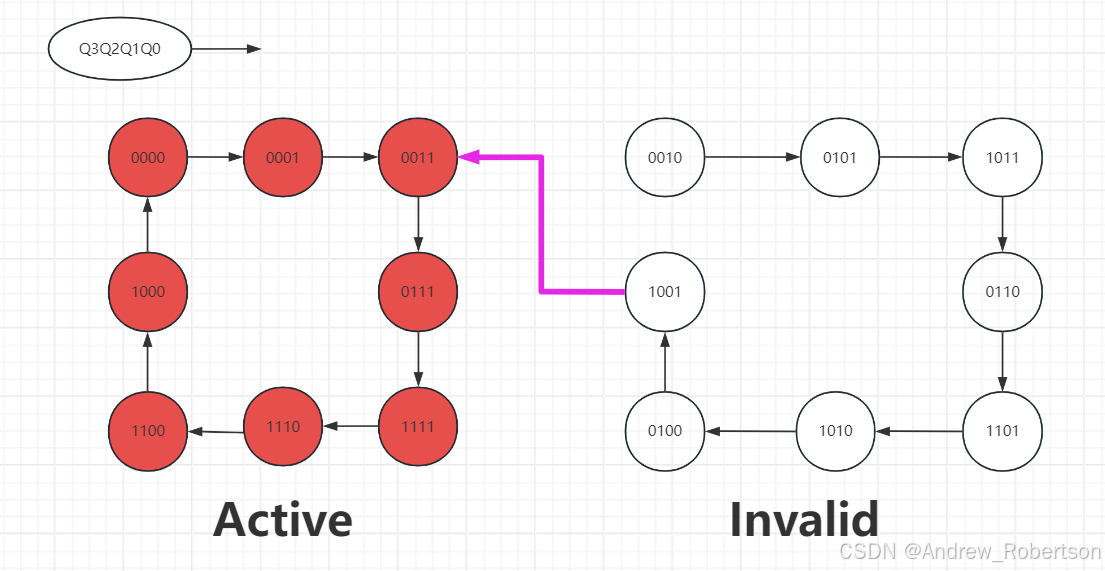

原理与环形计数器类似,状态利用率更高,模8计数器,状态转换图/电路图/波形图如下:

优化

∩和∪

无效循环转换为有效循环

将1001次态转换为0011,即D0=Q3Q2'Q1'Q0

反馈电路: D0 = Q3Q2'Q1'Q0 + Q3' = Q2'Q1'Q0 + Q3' = [Q3(Q2'Q1'Q0)']' (与非式)

自启动优化:移位寄存器 + 反馈电路 D0=[Q3(Q2Q1Q0')']'

状态转换图

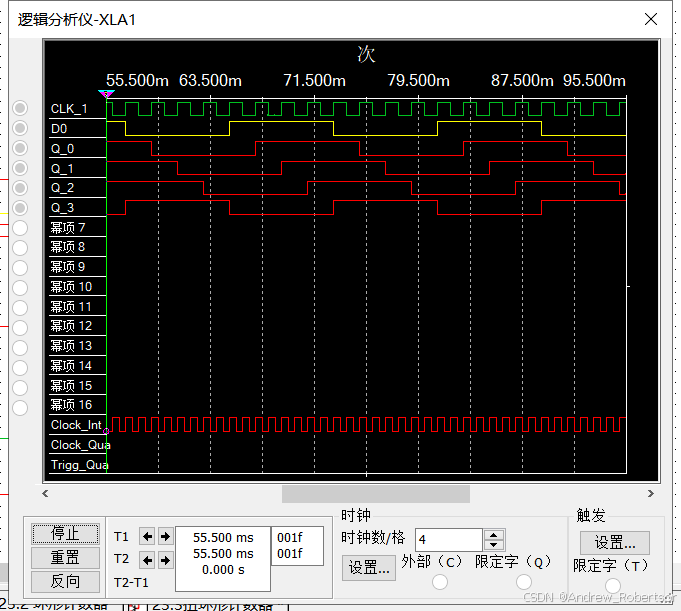

电路图:VCC模拟干扰脉冲0010

波形:经过8个脉冲后回到有效循环

也可以参考书上更简单高效的结构:移位寄存器 + 反馈电路 D0=(Q1Q2'+Q3')

电路图:

波形图:5个脉冲回到有效循环

以上です。

601

601

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?