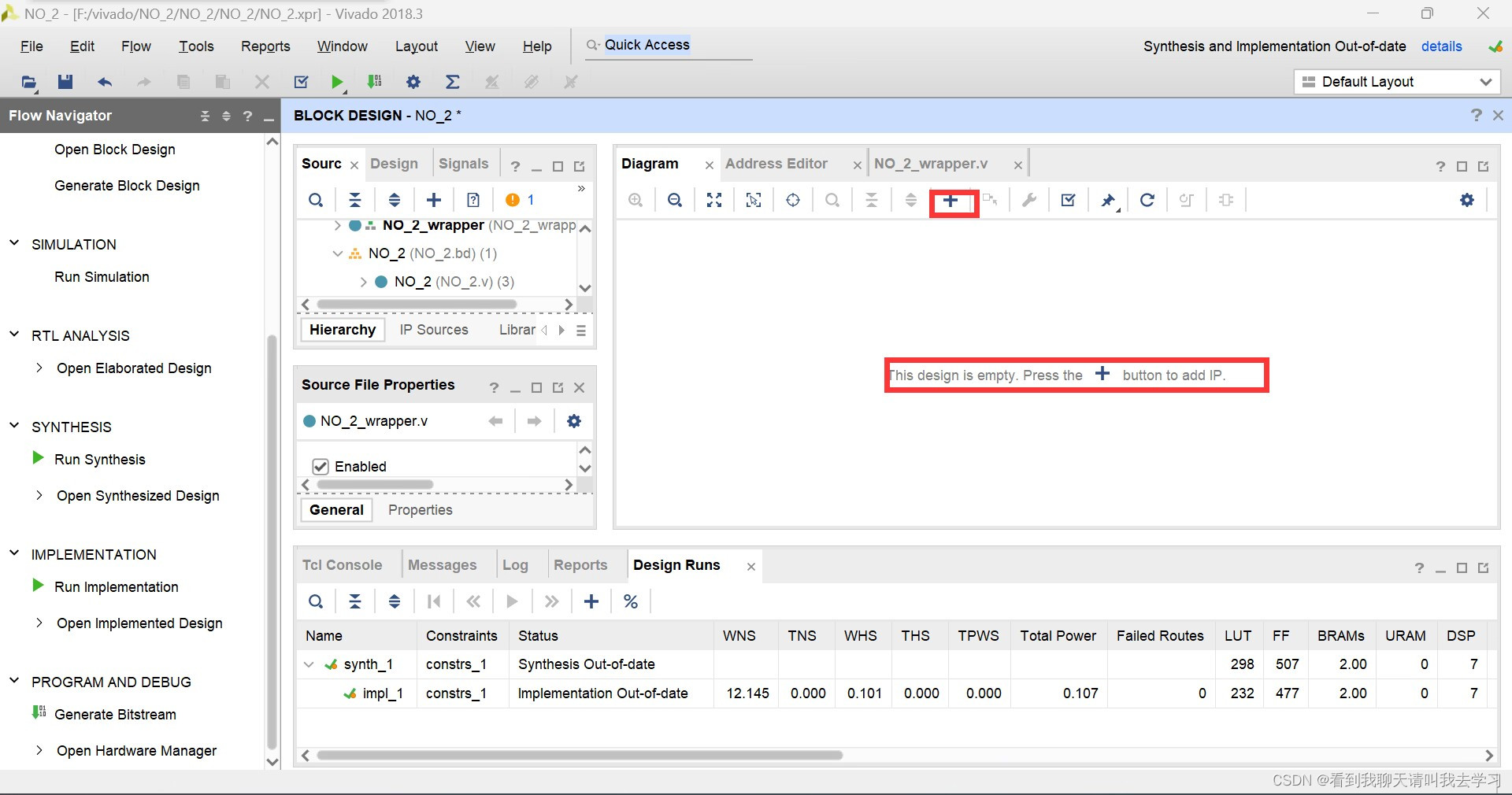

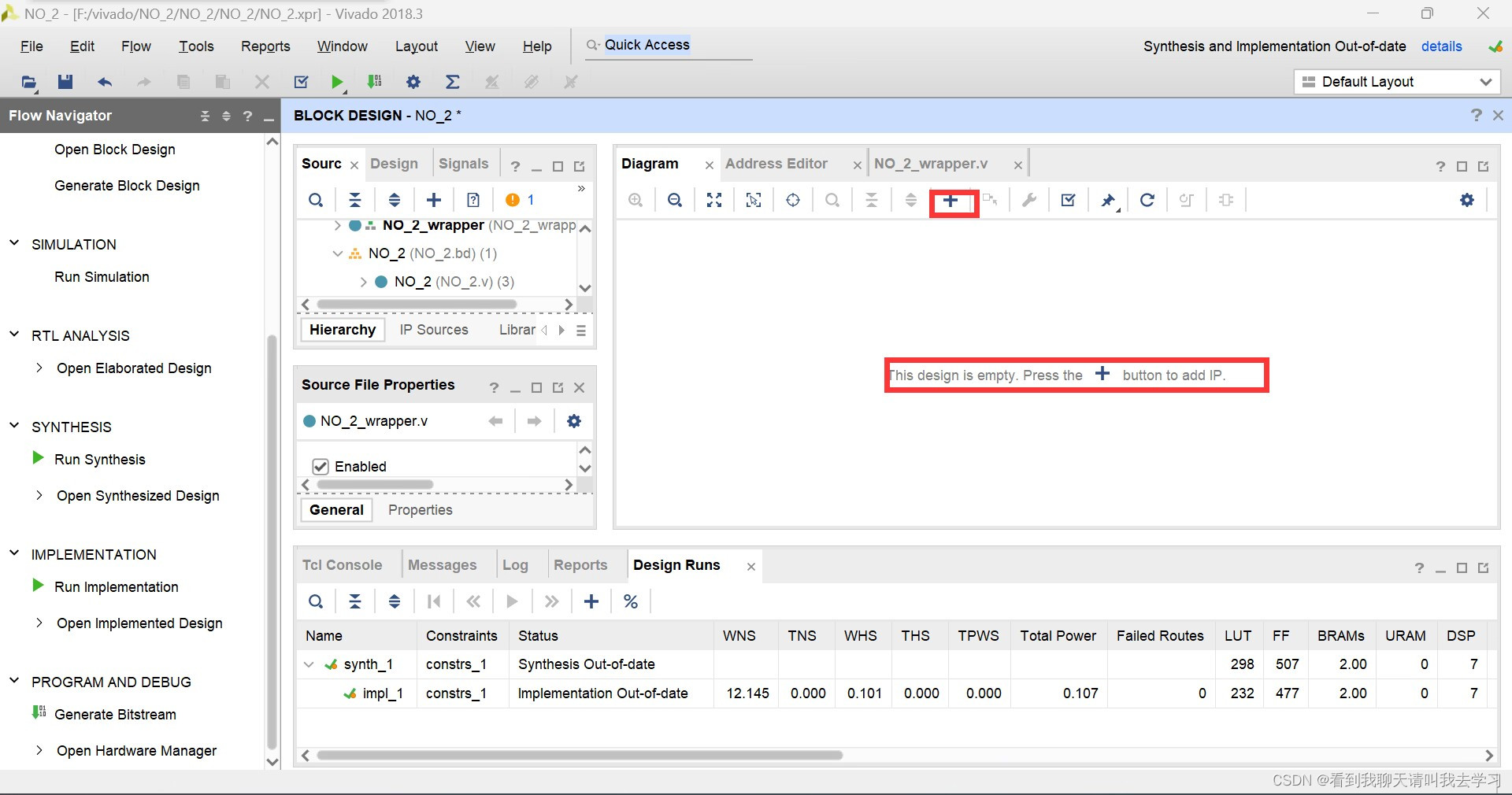

打开vivado工程文件(我这边打开的是之前已经烧录的),打开后:点击Create block design,设置一个名字,然后ok,会弹出一个diagram的图窗,点击➕(图示两种方法都可以)

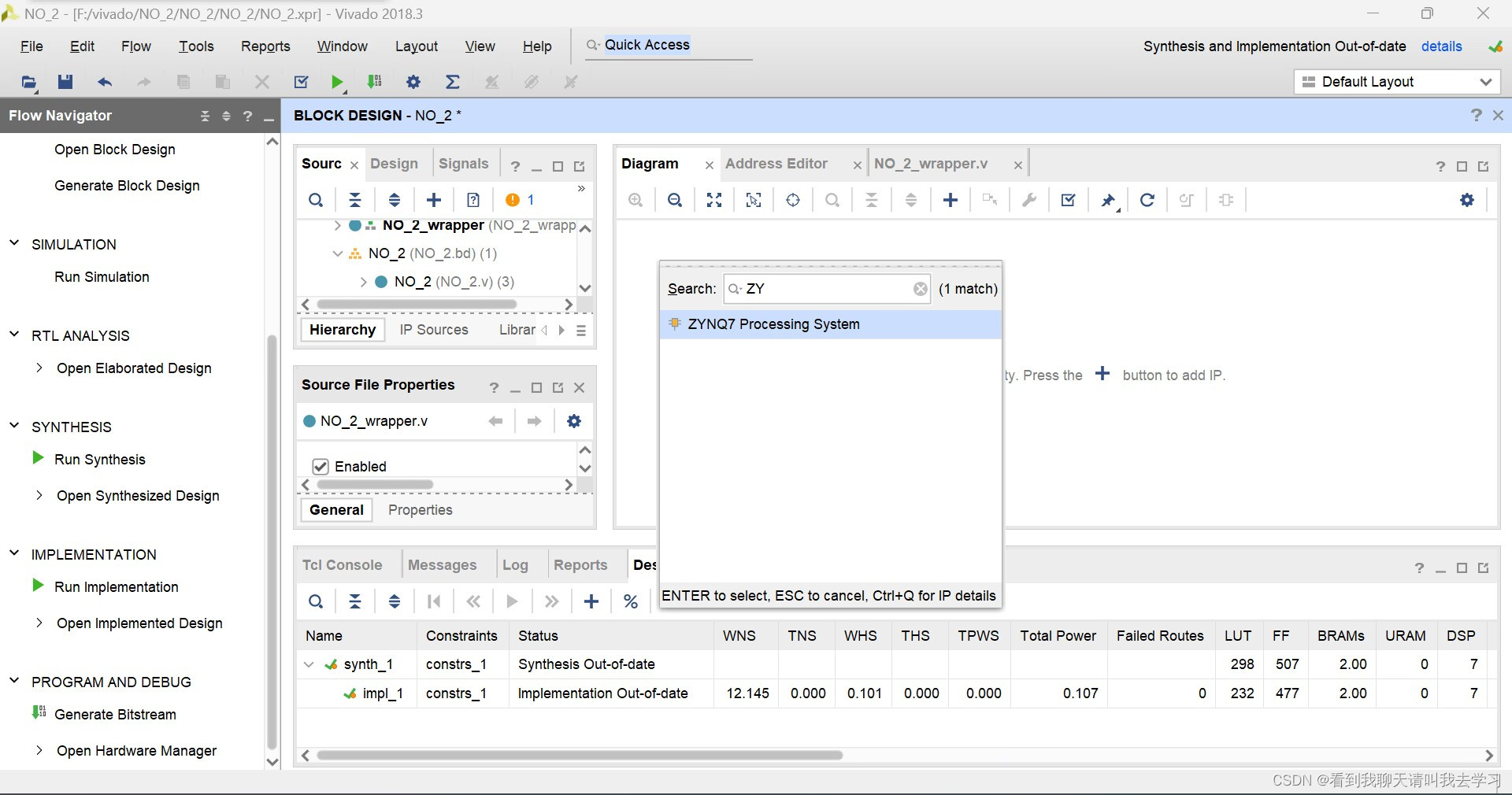

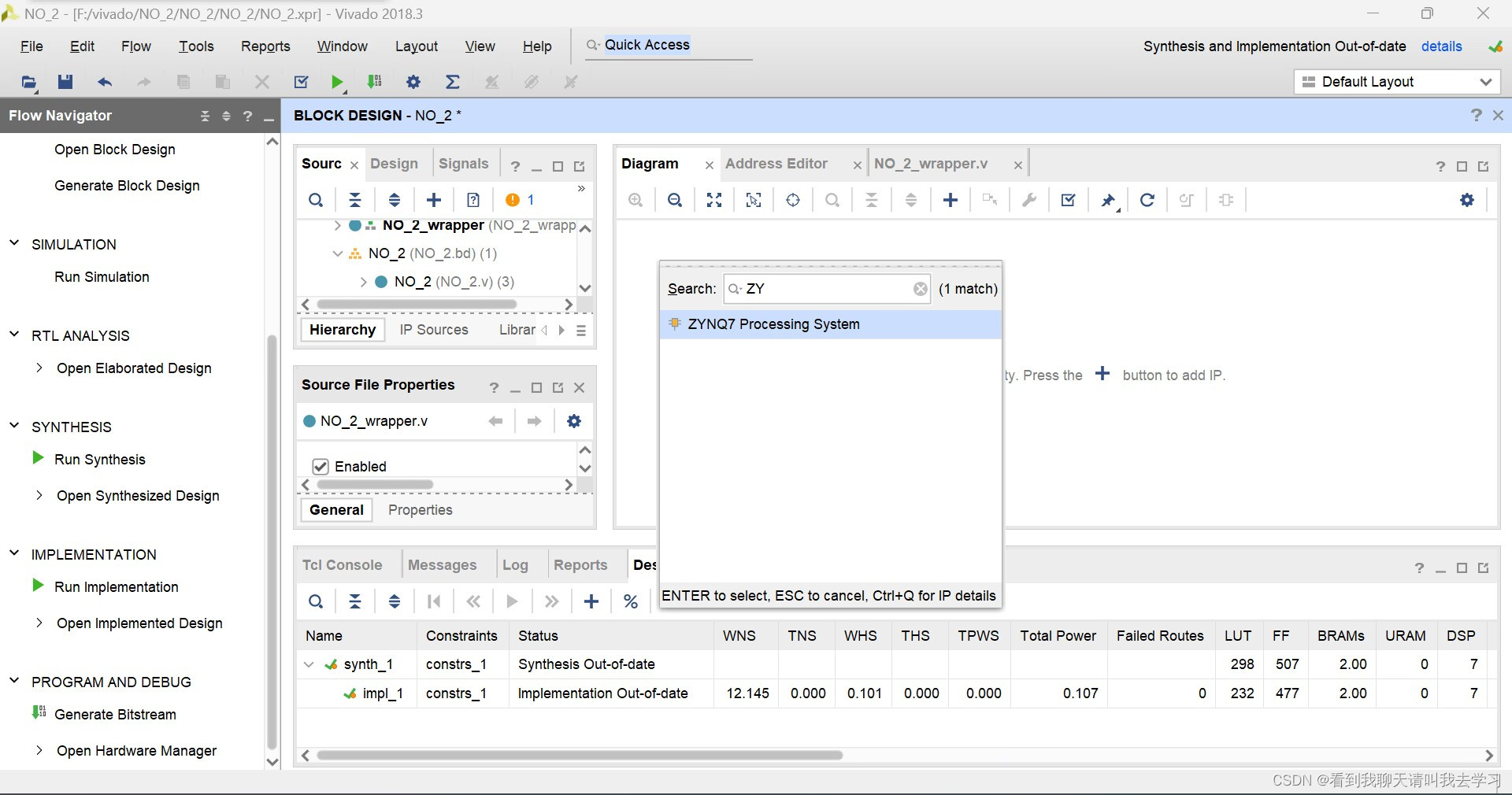

添加Zynq

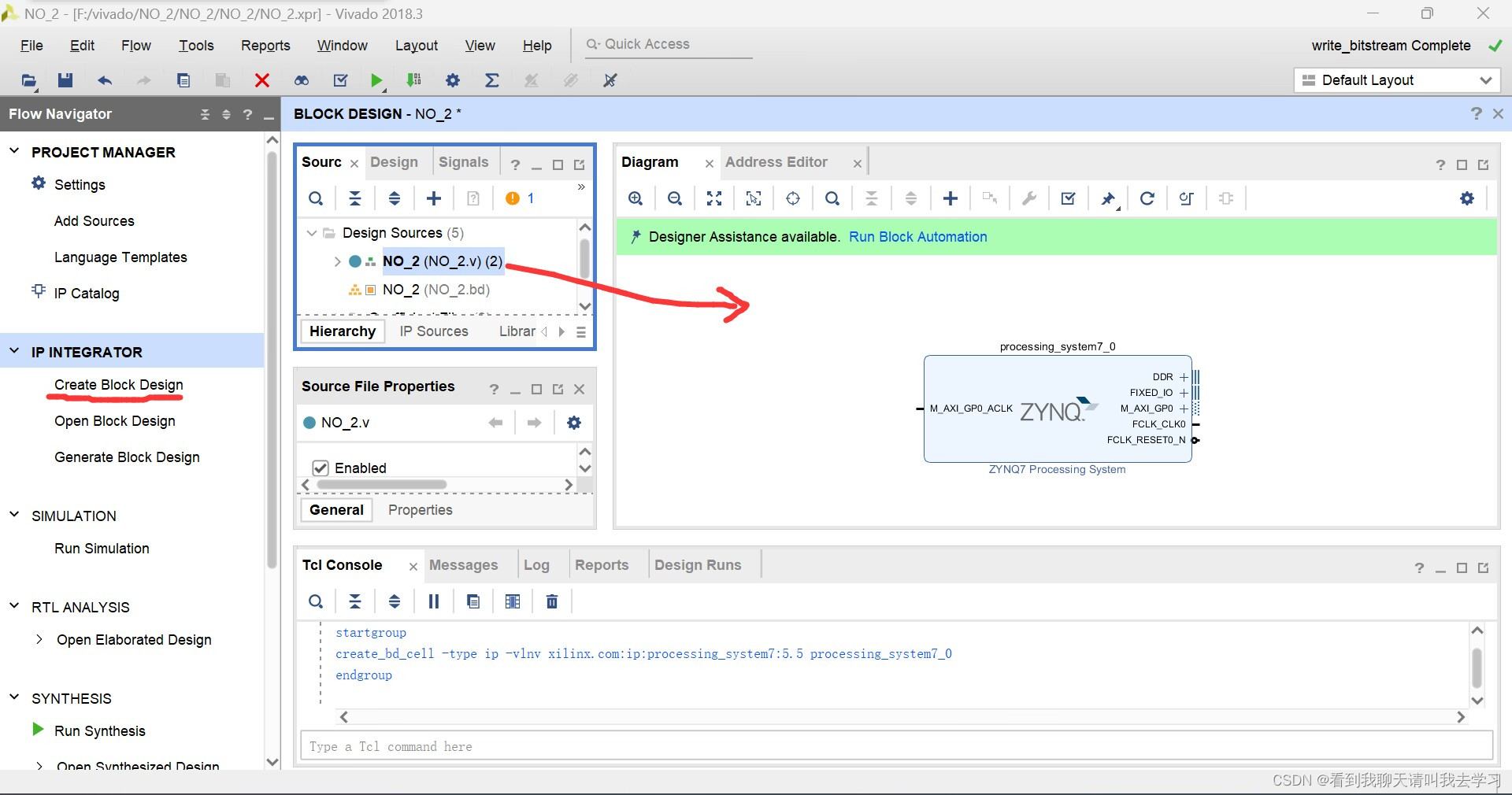

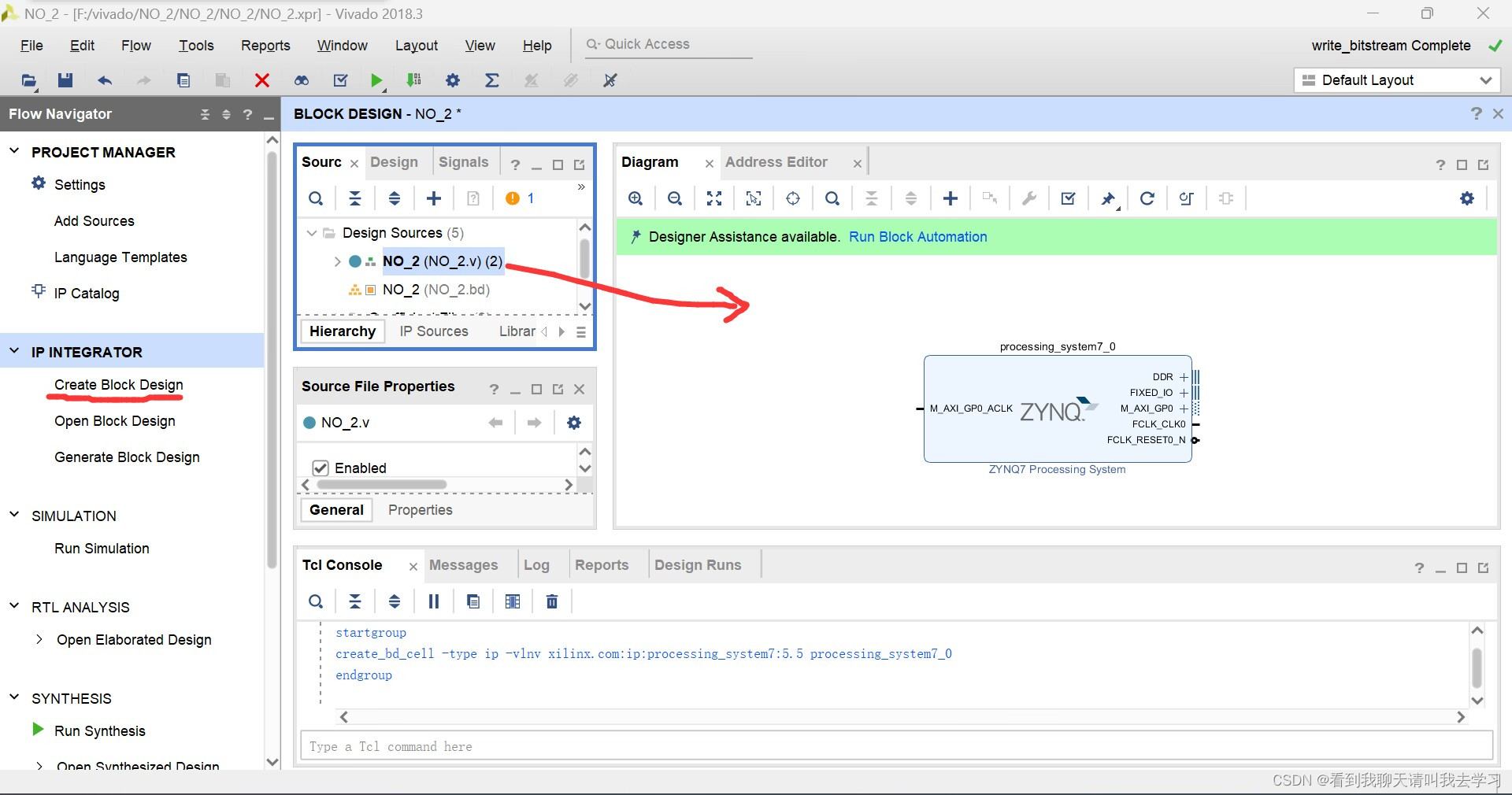

把工程.v文件拖出到diagram窗口里面

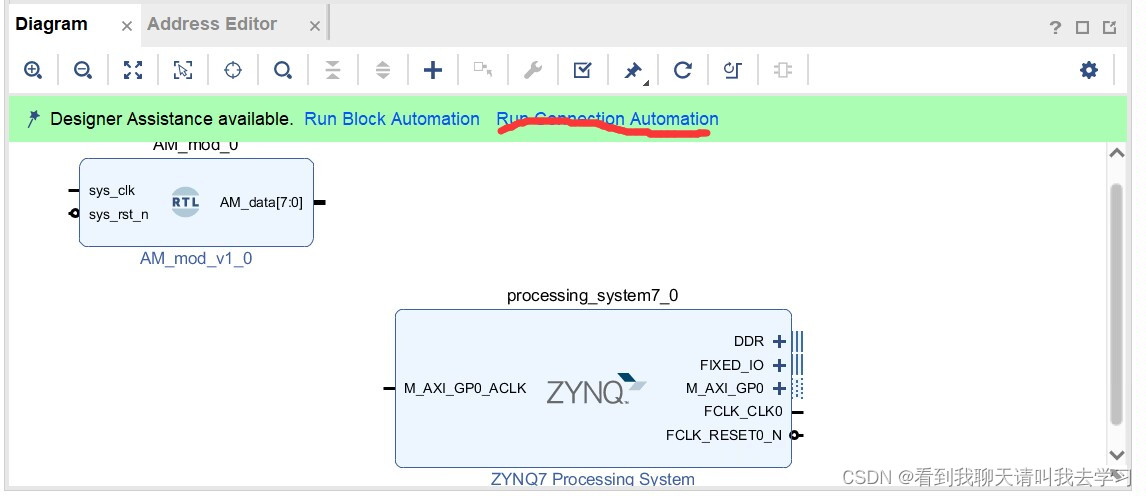

拖进去后,点run

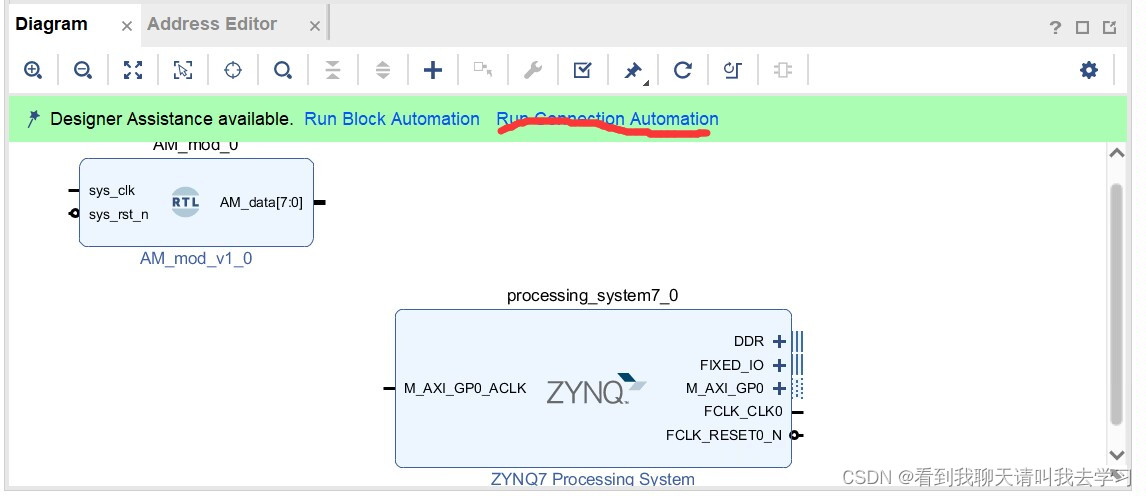

之后vivado会自动连线,连线后,右击自己的模块,点击methed,引出其它线

打开vivado工程文件(我这边打开的是之前已经烧录的),打开后:点击Create block design,设置一个名字,然后ok,会弹出一个diagram的图窗,点击➕(图示两种方法都可以)

添加Zynq

把工程.v文件拖出到diagram窗口里面

拖进去后,点run

之后vivado会自动连线,连线后,右击自己的模块,点击methed,引出其它线

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?