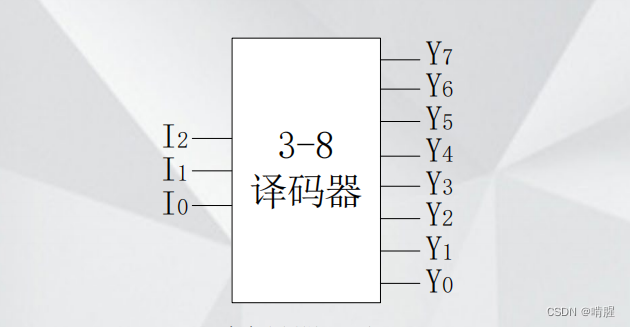

下图为3-8译码器的示意图:

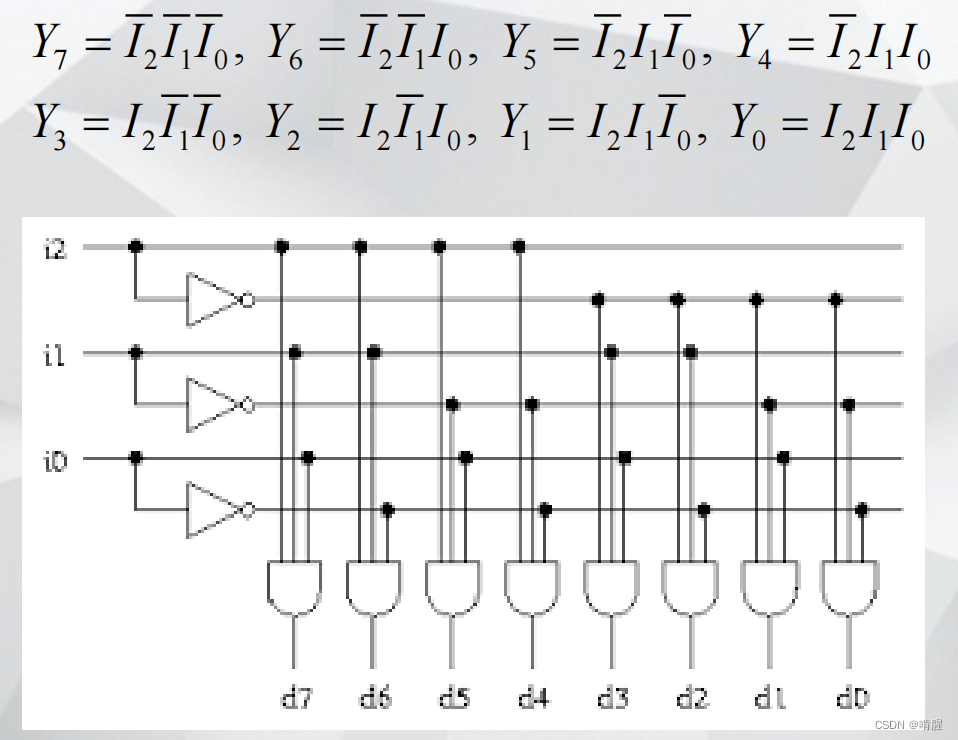

输出与输入的逻辑表达式:

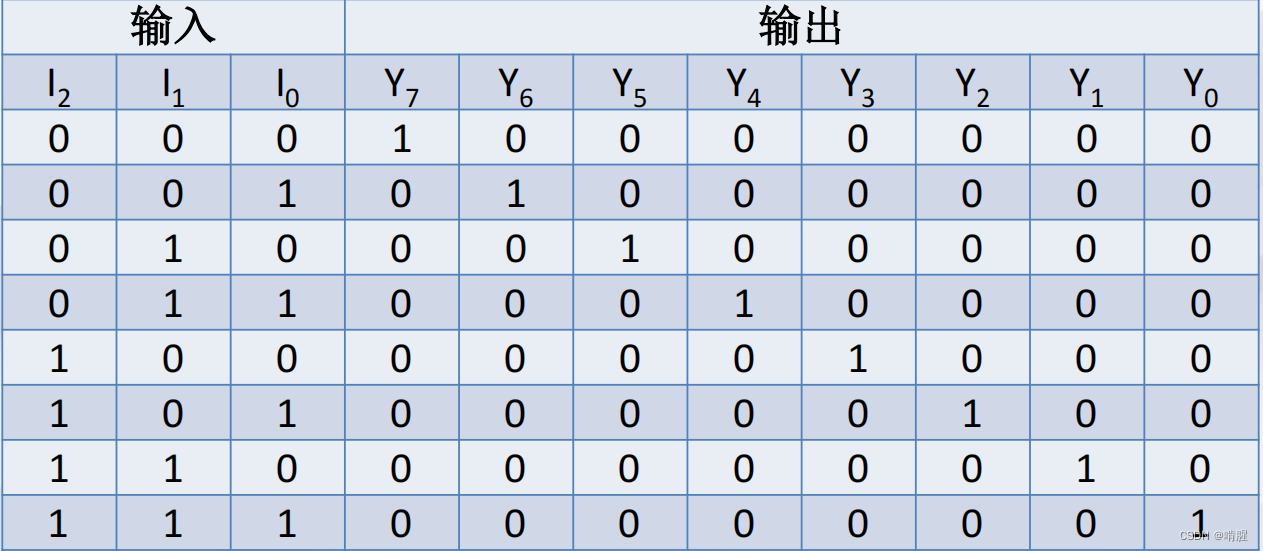

8-3编码器真值表:

代码实现:

module decoder38(data_in,data_out);

input [2:0] data_in;

output reg [7:0] data_out;

always@(data_in) begin

case(data_in)

3'b000: data_out = 8'b1000_0000;

3'b001: data_

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?