以下是关于STM32 RCC(Reset and Clock Control)模块的详细解析,结合其核心功能、时钟架构、配置流程及常见问题。

一、RCC的核心功能

RCC是STM32的时钟与复位控制核心,负责以下关键任务:

1. 多时钟源管理

高速时钟源:HSI(8MHz内部RC)、HSE(4-16MHz外部晶振)、PLL(锁相环倍频输出)。

低速时钟源:LSI(40kHz内部RC)、LSE(32.768kHz外部晶振)。

时钟选择:通过寄存器切换不同时钟源以满足性能与功耗需求(如HSE用于高精度场景,LSI用于低功耗RTC)。

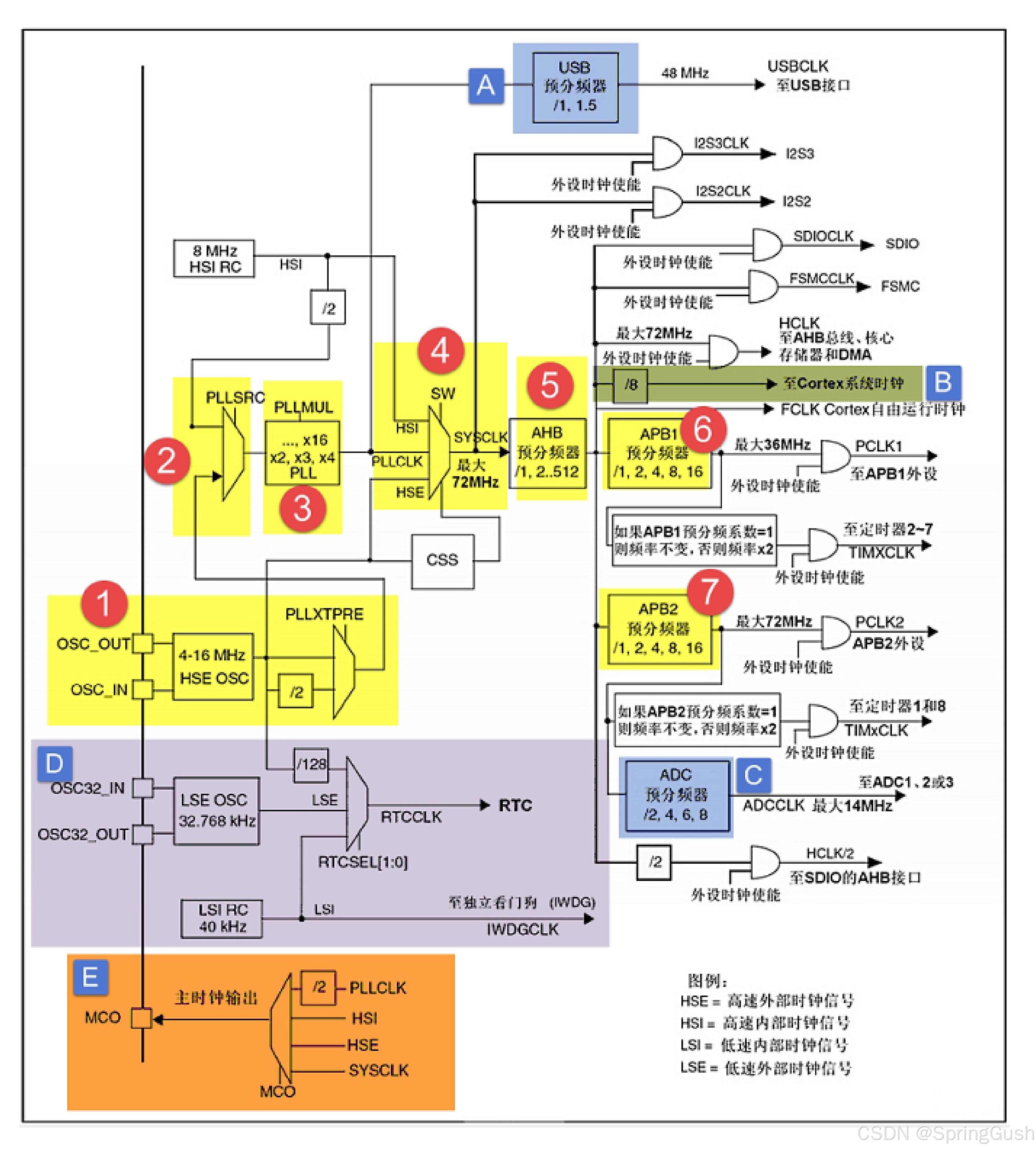

2. 时钟树分配

系统时钟(SYSCLK):最高频率由芯片型号决定(如STM32F103为72MHz,F407为168MHz),通过PLL或直接选择HSE/HSI。

总线时钟:

(1) AHB总线:用于CPU内核、内存、DMA,由SYSCLK分频(1/2/4/8/16等)。

(2) APB1/APB2总线:APB1最大36MHz(低速外设如I2C、SPI2),APB2最大72MHz(高速外设如GPIO、ADC)。

3. 外设时钟门控

独立控制每个外设的时钟使能(如GPIOA、USART1),默认关闭以降低功耗。

4. 时钟安全与监控

CSS(时钟安全系统):检测HSE失效时自动切换到HSI,并触发中断。

二、时钟树架构与关键分频逻辑

1. 时钟树结构

输入源:HSI/HSE/LSI/LSE → PLL配置(倍频与分频) → SYSCLK → AHB分频 → APB1/APB2分频 → 外设时钟。

特殊规则:

若APB分频系数≠1,定时器时钟(TIMxCLK)将自动×2(如APB1分频为2时,TIM2时钟为36MHz×2=72MHz)。

2. PLL配置示例(STM32F103)

HSE→PLL:外部晶振8MHz → PLL分频因子M=8 → PLL倍频因子N=9 → 输出SYSCLK=72MHz。

HSI→PLL:内部8MHz → 分频M=2 → 倍频N=18 → SYSCLK=72MHz。

三、RCC配置流程(以STM32F103配置72MHz为例)

1. 初始化步骤:

步骤1:启用HSE并等待稳定(RCC_CR寄存器设置)。

步骤2:配置PLL参数(M、N、P分频/倍频因子)并启动PLL。

步骤3:切换系统时钟源到PLL,等待切换完成。

步骤4:设置AHB/APB分频因子(如AHB=72MHz,APB1=36MHz,APB2=72MHz)。

步骤5:使能外设时钟(如RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOA, ENABLE))。

2. 代码模板关键点:

// 启动HSE

RCC_HSEConfig(RCC_HSE_ON);

while (!RCC_WaitForHSEStartUp());

// 配置PLL,HSE=8MHz, PLL输出72MHz

RCC_PLLConfig(RCC_PLLSource_HSE_Div1, RCC_PLLMul_9);

RCC_PLLCmd(ENABLE);

while (RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET);

// 切换系统时钟

RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);

while (RCC_GetSYSCLKSource() != 0x08);

// 设置总线分频

RCC_HCLKConfig(RCC_SYSCLK_Div1); // HCLK=72MHz

RCC_PCLK1Config(RCC_HCLK_Div2);// APB1=36MHz

RCC_PCLK2Config(RCC_HCLK_Div1);// APB2=72MHz

四、常见问题与解决方案

1. 主频异常

原因:HSE未就绪、PLL参数错误或晶振电路故障。

排查:通过MCO引脚输出SYSCLK并用示波器测量,检查寄存器状态。

2. 定时器时钟频率错误

根源:APB分频系数≠1时,定时器时钟自动×2(需根据实际分频调整预分频值)。

3. HSE失效导致系统卡死

解决:启用CSS功能,在HSE故障时触发中断并切换到HSI。

五、应用建议

1. 低功耗设计:关闭未使用外设时钟,切换低速时钟源(如RTC使用LSE)。

2. 多型号兼容:不同STM32系列时钟树差异大(如F1与F4),需参考具体手册调整参数。

3. 工具辅助:使用STM32CubeMX图形化配置时钟树,避免手动计算分频/倍频。

六、总结

RCC模块是STM32高效运行的核心,其灵活的多时钟源配置、分频策略及安全机制为不同应用场景(高速计算、低功耗、实时控制)提供了基础支持。开发者需深入理解时钟树逻辑,结合硬件特性与库函数规范,才能实现稳定可靠的系统设计。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?