一、实验目的

1.掌握中规模(MSI)集成译码器的逻辑功能和使用方法;

2.验证3—8线译码器和七段显示译码器的逻辑功能;

3.掌握数码管与译码器配合使用的方法。

二、实验原理

译码器的作用是进行代码间的“翻译”,将具有特定含义的二进制码进行辨别,并转换成控制信号。

译码器分通用译码器和显示译码器两大类。前者又分为变量译码器和代码变换译码器。

l.变量译码器(又称二进制译码器)

变量译码器用以表示输入变量的状态,如2—4线、3—8线和4—16线译码器。若有n个输入变量,则有2n个不同的组合状态,就有2n个输出端供其使用。例如,有3个输入变量(或称为地址端),那么就可以有23=8个不同的地址组合,分别为000、001、010、011、100、101、110、111,可以控制8个输出端,而每一个输出所代表的函数对应于n个输入变量的最小项。

图2-1 3—8线译码器74LS138逻辑图及引脚排列

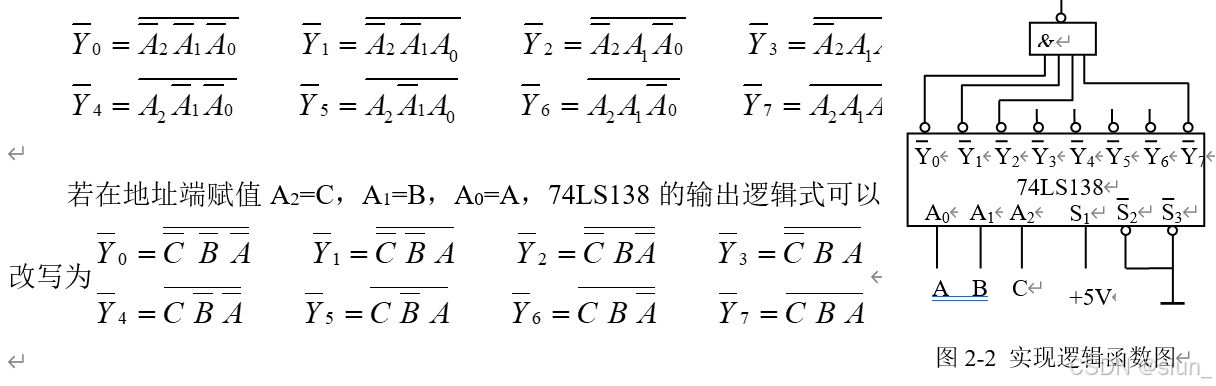

以3线—8线译码器74LSl38为例,图2-1(a)(b) (c)分别为其逻辑电路及引脚排列。其中A2、A1、A0为地址输入端, ̄Y0~ ̄Y7为译码输出端,S1、¯S2、¯S3为使能端。表2-1所示为74LSl38功能表。

当S1=1,¯S2+¯S3=0时,74LS138工作,地址码所指定的输出端输出0(被选中),其它输出端均输出1(未被选中)。当S1=0;¯S2+¯S3=×(注:“×”即不论是什么逻辑值的意思);或S1=×,¯S2+¯S3=1时,译码器被禁止,所有输出同时为l。

表2-1 74LS138功能表

| 输 入 |

输 出 |

|||||||||||

| S1 |

¯S2+¯S3 |

A2 |

A1 |

A0 |

`Y0 |

`Y1 |

`Y2 |

`Y3 |

`Y4 |

`Y5 |

`Y6 |

`Y7 |

| 1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

| 1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

| 1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

| 1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

| 1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

| 1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

| 1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

| 1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

| 0 |

× |

× |

× |

× |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

| × |

1 |

× |

× |

× |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

二进制译码器还可以用来实现逻辑函数。由表2-1知,74LS138正常工作时,每个输出端输出的逻辑关系为

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?