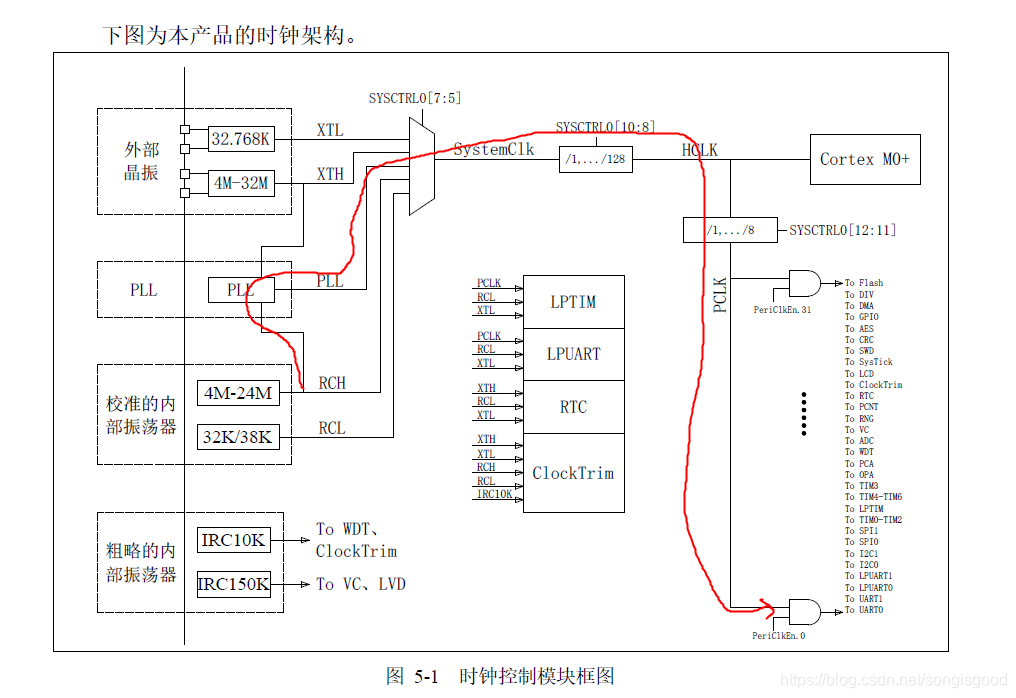

最近使用HC32L130xxx单片机做项目,使用内部RCH做为主时钟源,RCH时钟源最高频率为24M,但是可以通过倍频PLL到48M,时钟源示意图如下图所示。

配置时钟时注意事项

1、在配置时钟源频率时,不能配置当前正在用的时钟源。比如当前正在使用RCH作为时钟源,那么就不可更改RCH的时钟源,如果要更改,需要将时钟源切换到其他时钟源上,比如切换到RLH。然后设置RCH,时钟源切换完成后,时钟源在切换到RCH。

2、当时钟源HCLK大于24M,此处设置FLASH 读等待周期为1 cycle(前面已经配置,此处无需重复配置),否则当切换时钟源到PLL48M时钟源时就会死机。

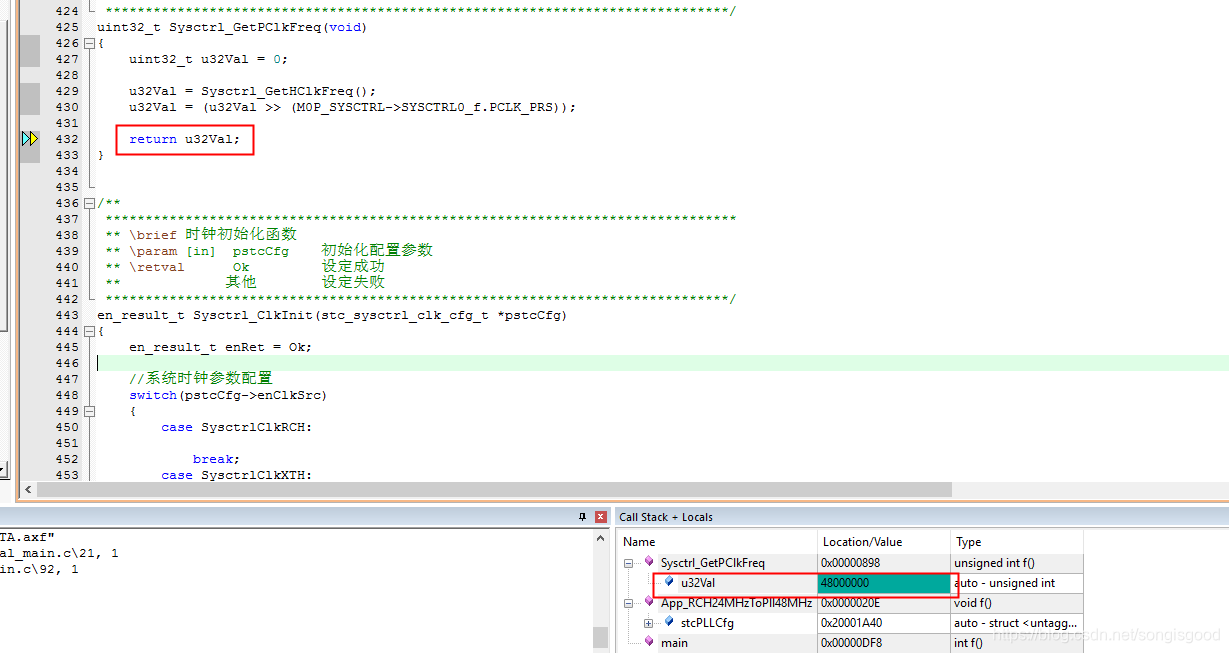

初始化程序如下所示。PCLK时钟可以通过Sysctrl_GetPClkFreq()函数读回,用以验证时钟是否设置正确。

void App_RCH24MHzToPll48MHz (void)

{

stc_sysctrl_pll_cfg_t stcPLLCfg;

///<============== 将时钟从RCH4MHz切换至RCH24MHz ==============================

///< RCH时钟不同频率的切换,需要先将时钟切换到RCL,设置好频率后再切回RCH

Sysctrl_SetRCLTrim(SysctrlRclFreq32768);

Sysctrl_ClkSourceEnable(SysctrlClkRCL, TRUE);

Sysctrl_SysClkSwitch(SysctrlClkRCL);

///< 加载目标频率的RCH的TRIM值

Sysctrl_SetRCHTrim(SysctrlRchFreq24MHz);

///< 使能RCH(默认打开,此处可不需要再次打开)

//Sysctrl_ClkSourceEnable(SysctrlClkRCH, TRUE);

///< 时钟切换到RCH

Sysctrl_SysClkSwitch(SysctrlClkRCH);

///< 关闭RCL时钟

Sysctrl_ClkSourceEnable(SysctrlClkRCL, FALSE);

///< 注意十分重要 当前时钟源HCLK大于24M:此处设置FLASH 读等待周期为1 cycle(前面已经配置,此处无需重复配置)

Flash_WaitCycle(FlashWaitCycle1);

stcPLLCfg.enInFreq = SysctrlPllInFreq20_24MHz; //RCH 24MHz

stcPLLCfg.enOutFreq = SysctrlPllOutFreq36_48MHz; //PLL 输出48MHz

stcPLLCfg.enPllClkSrc = SysctrlPllRch; //输入时钟源选择RCH

stcPLLCfg.enPllMul = SysctrlPllMul2; //24MHz x 2 = 48MHz

Sysctrl_SetPLLFreq(&stcPLLCfg);

Sysctrl_SetPLLStableTime(SysctrlPllStableCycle16384);

Sysctrl_ClkSourceEnable(SysctrlClkPLL, TRUE);

///< 时钟切换

Sysctrl_SysClkSwitch(SysctrlClkPLL);

Sysctrl_GetPClkFreq(); //获取PCLK时钟频率

}

debug在线调试读取结果。

378

378

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?