文章目录

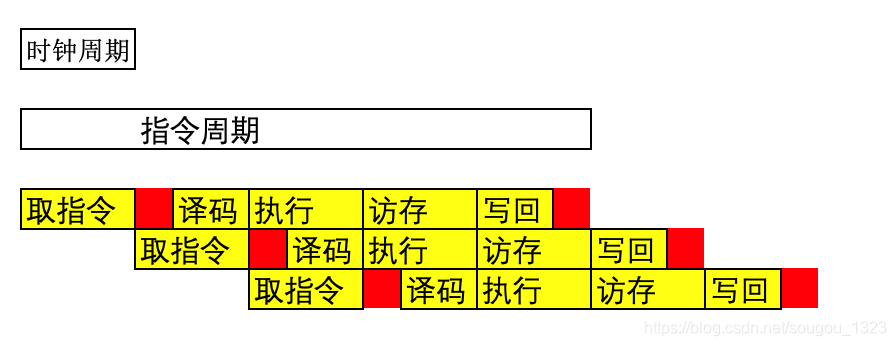

1. 时钟周期、机器周期、指令周期

时钟周期是由晶振决定的,晶振的一次震荡我们就叫做时钟周期。我们平时说的处理器的主频就可以理解为单位时间内执行的简单指令,例如3.8GHz主频就是一秒种可以执行简单指令3.8G条。

机器周期,也叫CPU周期。由于CPU运行很快,但是访问内存的速度相对来说就慢太多了,所以我们一般把从内存中读取一条指令的最短时间称为机器周期。

计算机每执行一条指令,都要经过取指令、指令译码、执行指令三个动作,这一系列动作我们就称为指令周期。

2. 单指令周期处理器

CPU执行指令的过程其实是分工协作的。取指令需要译码器把数据从内存取出,写入寄存器。指令译码需要另外的译码器,把指令解析成对应的控制信号、内存地址和数据。执行指令需要ALU完成计算工作。

处理器在一个时钟周期处理一整条指令,就称为单指令周期处理器。

由于不同指令的执行时间不同,为了让所有指令都在一个时钟周期内完成,就要让让执行快的指令迁就一下执行慢的指令,也就是把时钟周期设置成执行时间最长的那个指令的执行时间。也就是说,执行快的指令执行完后,我们必须等待满一个时钟周期后才能指令下一条指令。

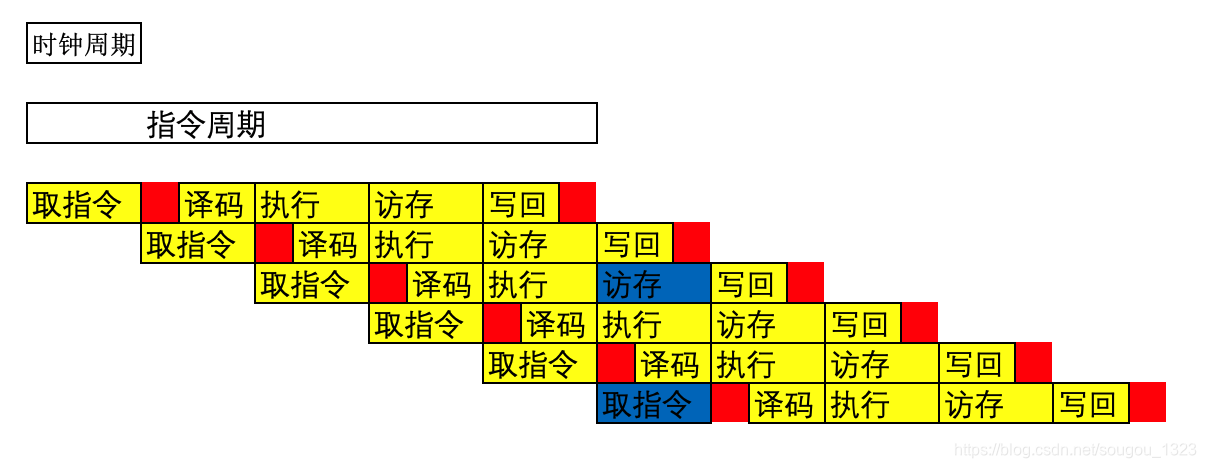

3. 流水线设计

单指令周期处理器,在某一个元器件工作的时候,其他的元器件就要等着,就太浪费资源了。

流水线设计就是在当前指令的某一阶段完成后,不需要等待整条指令全部完成,而是转而执行下一条指令的同一阶段。这样的设计就可以提高处理器主频,也就是缩短时钟周期。因为之前一条指令为一个时钟周期,现在一个阶段就可以设为一个时钟周期了。

同样,对比单指令周期处理器,我们需要找到最费时间的阶段,将其设置为时钟周期,来确保每一个阶段都可以在一个时钟周期内完成。如果某一个阶段的时间太长,明显会影响处理速度,因为其他阶段执行完之后都在等他,这时我们会考虑将这个阶段拆分成更小的阶段。现代的 ARM 或者 Intel 的 CPU,流水线级数都已经到了 14 级,也就是将一条指令拆成了14个阶段。

4. 结构冒险

结构冒险就是在两条指令的不同阶段都使用了同一个硬件,例如在访存和取指令的时候,都需要访问内存。

引入缓存

哈佛架构把内存分成了两部分,数据内存和程序

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6479

6479

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?