时钟树(f103系列):

可以看到stm32主要有五个时钟源:HSI、HSE、LSI、LSE、PLL。(四号指的是LSI,不是底下的MCO,其中SE是外部时钟的意思,SI是内部时钟的意思,S和E是external和internal的缩写,PLL是锁相环)

可见一般内部时钟都是由内部RC振荡电路产生,而外部时钟一般都是由外部晶振电路(晶体/陶瓷谐振器)产生,其中HSE还可以由用户外部时钟提供在CubeMX中LSE也有旁路时钟源选项,但是我们一般不用,只用固定的32.768kHz的晶振。而PLL则是由HSI或HSE倍频激活。

系统时钟只能由HSI、HSE、PLL产生:

其中CSS是时钟安全系统,时钟安全系统被激活后,时钟监控器将实时监控外部高速振荡器;如 果HSE时钟发生故障,外部振荡器自动被关闭,产生时钟安全中断,此中断被连接到Cortex-M3的NMI的中断;与此同时CSS将内部RC振荡器切换为STM32的系统时钟源。( 对于STM32F103 ,时钟失效事件还将被送到高级定时器TIM1的刹车输入端,用以实现电机保护控制)

HSI内部高速时钟:

HSI时钟是由内部8MHz的RC振荡电路产生的,可直接作为系统时钟或在2分频后作为PLL输入。HSI RC振荡器能够在不需要任何外部器件的条件下提供系统时钟。它的启动时间比HSE晶体振荡器短。然而,即使在校准之后它的时钟频率精度仍较差。

制造工艺决定了不同芯片的RC振荡器频率会不同,这就是为什么每个芯片的HSI时钟频率在出厂前已经被ST校准到1%(25°C)的原因。系统复位时,工厂校准值被装载到时钟控制寄存器的HSICAL[7:0]位。 如果用户的应用基于不同的电压或环境温度,这将会影响RC振荡器的精度。可以通过时钟控制寄存器里的HSITRIM[4:0]位来调整HSI频率。

也就是说出厂的时候有个校准值,一旦复位就会把这个值重装到寄存器中去,但是这个校准值是基于25摄氏度的,不同环境下这个值是不准的。

HSE外部高速时钟:

高速外部时钟信号(HSE)由以下两种时钟源产生:

● HSE外部晶体/陶瓷谐振器

● HSE用户外部时钟(旁路模式)

两种时钟源的接法如下:

使用外部时钟模式的时候应注意:

该模式下必须提供外部时钟。用户通过设置时钟控制寄存器中的HSEBYP和HSEON位来选择这一模式。外部时钟信号(50%占空比的方波、正弦波或三角波)必须连到SOC_IN引脚,此时OSC_OUT引脚对外呈高阻态。(hiz就是高阻态的意思,通过设置寄存器使得该引脚呈现高阻态)

使用晶振模式的时候应注意:

该时钟源是由外部无源晶体与MCU内部时钟驱动电路共同配合形成,有一定的启动时间,精度较高。

为了减少时钟输出的失真和缩短启动稳定时间,晶体/陶瓷谐振器和负载电容必须尽可能地靠近振荡器引脚。负载电容值必须根据所选择的晶体来具体调整。

我们使用的最小系统板上已经帮我们配置了8MHz的晶振,所以我们直接使用晶振模式,并且CubeMX配置的时候不要改动HSE的输入频率:

有两个箭头说明选择了晶振模式:

LSE外部低速时钟:

LSE晶体是一个32.768kHz的低速外部晶体或陶瓷谐振器。它为实时时钟或者其他定时功能提供一个低功耗且精确的时钟源。

在这个模式里必须提供一个32.768kHz频率的外部时钟源。你可以通过设置在备份域控制寄存器(RCC_BDCR)里的LSEBYP和LSEON位来选择这个模式。具有50%占空比的外部时钟信号(方波、正弦波或三角波)必须连到OSC32_IN引脚,同时保证OSC32_OUT引脚悬空。

因为是32.768kHz,所以引脚是OSC32,与HSE引脚区分开来。

LSI内部低速时钟:

LSI RC担当一个低功耗时钟源的角色,它可以在停机和待机模式下保持运行,为独立看门狗和自动唤醒单元提供时钟。LSI时钟频率大约40kHz(在30kHz和60kHz之间)。

PLL锁相环:

内部PLL可以用来倍频HSI RC的输出时钟或HSE晶体输出时钟。PLL的设置(选择HIS振荡器除2或HSE振荡器为PLL的输入时钟,和选择倍频因子)必须在其被激活前完成。一旦PLL被激活,这些参数就不能被改动。

如果PLL中断在时钟中断寄存器里被允许,当PLL准备就绪时,可产生中断申请。 如果需要在应用中使用USB接口,PLL必须被设置为输出48或72MHZ时钟,用于提供48MHz的USBCLK时钟。

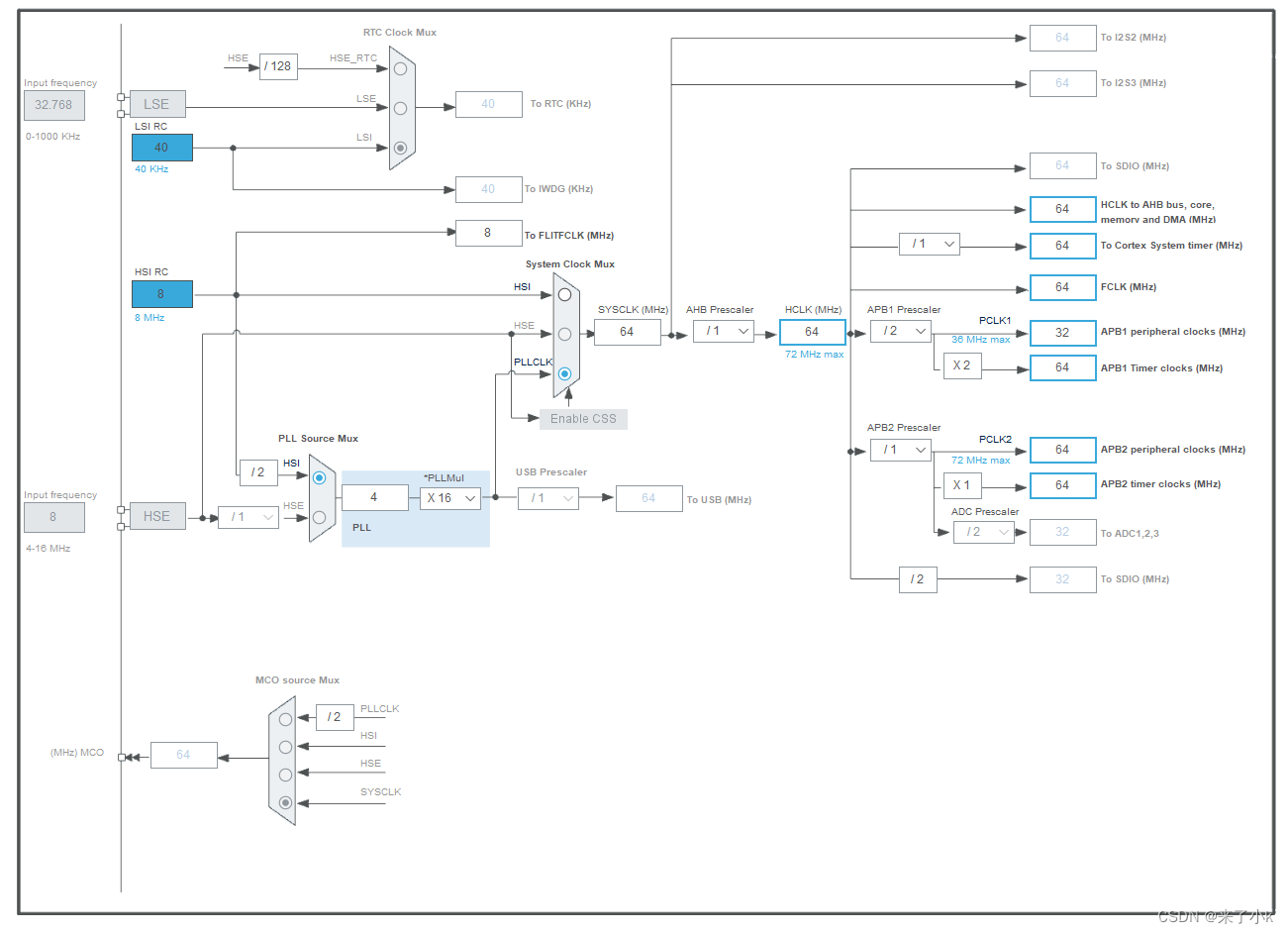

CubeMX时钟树:

要注意的是,使用内部高速时钟的话,最大能配置到64MHZ,使用外部高速时钟的话,能配置到72MHZ。

原因在于使用HIS通过PLL锁相环时,必须要先两分频才行,无法更改:

这导致了PLL倍频的时候初值只能是4,就算最大倍频x16倍,最多也只有64MHz。

AHB总线和APB总线以及HCLK、PCLK、FCLK:

AHB是高速总线,用于高性能模块(CPU、DMA、DSP等)的连接。

APB是低速总线,也是外围总线,主要用于外设之间的连接,分为APB1和APB2。其中APB1操作速度限于36MHz,APB2操作于全速(最高72MHz)。

APB1负责DAC、USB、SPI_23、I2C、CAN、串口2345、普通TIM;

APB2负责ADC、IO、高级TIM、串口1、SPI_1、EXTI、AFIO。

FCLK:提供给CPU内核的时钟信号,CPU的主频就是指这个信号;

HCLK:提供给高速总线AHB的时钟信号;

PCLK:提供给低速总线APB上外设的时钟信号。APB总线上的定时器信号不同过PCLK,而是直接由HCLK分频提供。

(HCLK、PCLK的P、H分别和AHB、APB的P、H对应)

时钟配置流程:

首先选择HSE晶振模式,一般没有用到RTC实时时钟模块就不使能LSE:

然后检查晶振输入频率和板子上的晶振频率是否一致:

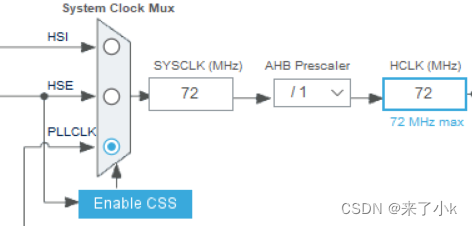

选择PLL,使得SYSCLK最大72MHz,这里通过AHB总线分频器,得到了HCLK时钟频率。HCLK一般不分频,等于系统时钟。:

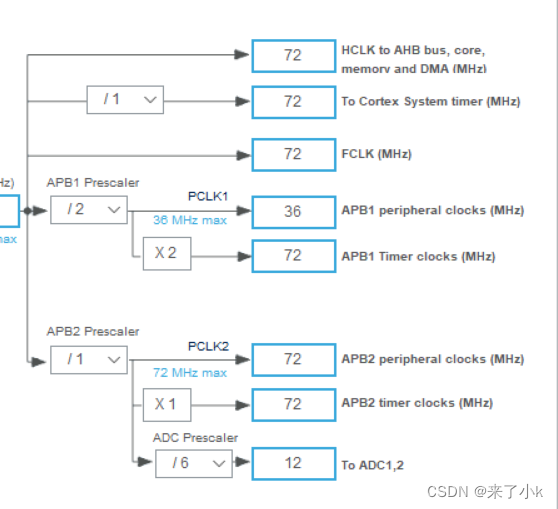

接着HCLK分给各个模块使用:

这个是送给AHB总线、内核、内存和DMA使用的HCLK时钟。

![]()

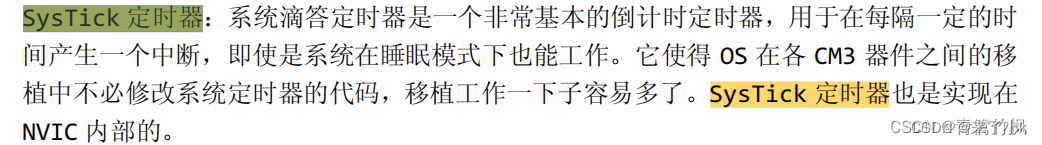

这个是提供给内核系统定时器使用的频率,只有一分频和八分频。也就是systick定时器(系统滴答定时器),SysTick系统定时器可以用于操作系统,用于产生时基,维持操作系统的心跳,一般操作系统都需要一个时基,进行任务的电镀,同步等功能的实现

![]()

直接送给Cortex的自由运行时钟(free running clock)FCLK。【ARMJISHU注:FCLK 为处理器的自由振荡的处理器时钟,用来采样中断和为调试模块计时。在处理器休眠时,通过FCLK 保证可以采样到中断和跟踪休眠事件。 Cortex-M3内核的“自由运行时钟(free running clock)”FCLK。“自由”表现在它不来自系统时钟HCLK,因此在系统时钟停止时FCLK 也继续运行。FCLK和HCLK 互相同步。FCLK 是一个自由振荡的HCLK。FCLK 和HCLK 应该互相平衡,保证进入Cortex-M3 时的延迟相同。】

送给APB1分频器。APB1分频器可选择1、2、4、8、16分频。

其输出一路供APB1外设使用(PCLK1,最大频率36MHz)。

另一路送给普通定时器,也就是TIM2、3、4、5使用。

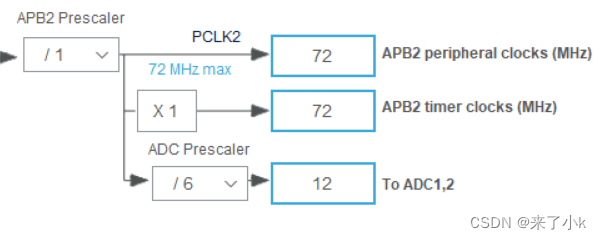

同上,通过APB2分频器,一路通过PCLK2给外设,一路给高级定时器TIM1、8。

不同的在于APB2负责ADC,所以通过ADC分频器提供给ADC1、2。

ADC1、2最高频率为12MHz。

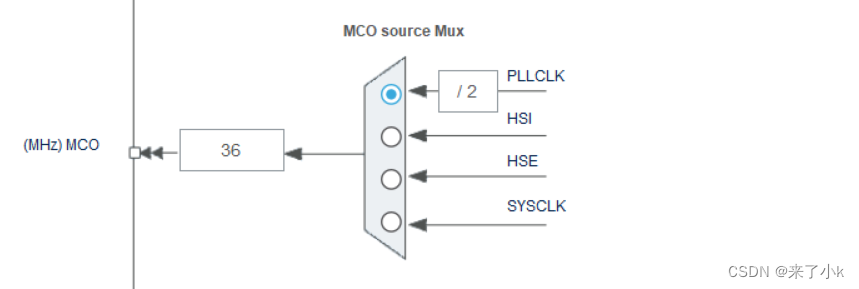

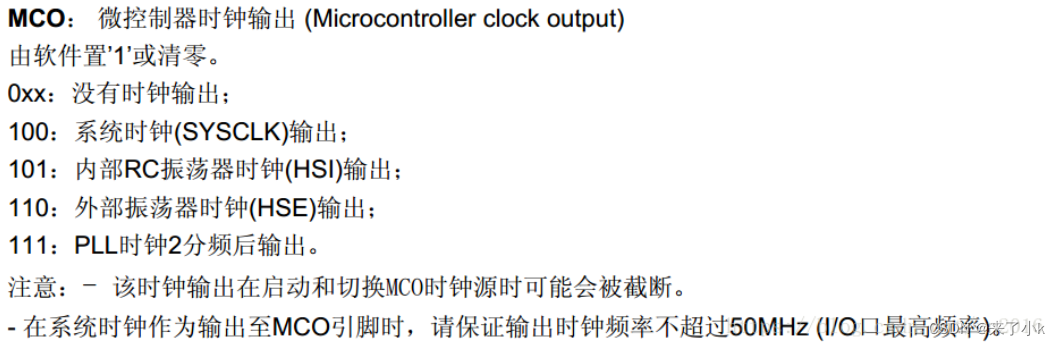

MCO是将单片机的时钟输出到MCO引脚上,可供选择的时钟源有4个,开启方式为勾选master clock output:

因为不超过50MHz,但是除了系统时钟,最高的就是PLL二分频后的36MHz,所以MCO引脚输出最多就是36MHz。

这玩意是啥暂时不知道。

4350

4350

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?