本文章并不是百分百的原创,并且仅仅是经验之谈,并不能完全保证其正确与严谨性。其中有一部分借鉴了网上的其他资源如AN799 Matching MOSFET Drivers to MOSFETs;以及诸多电子论坛上的文章如《MOS管及其外围电路设计》等,在这里向原文章作者表示感谢!

栅极驱动部分

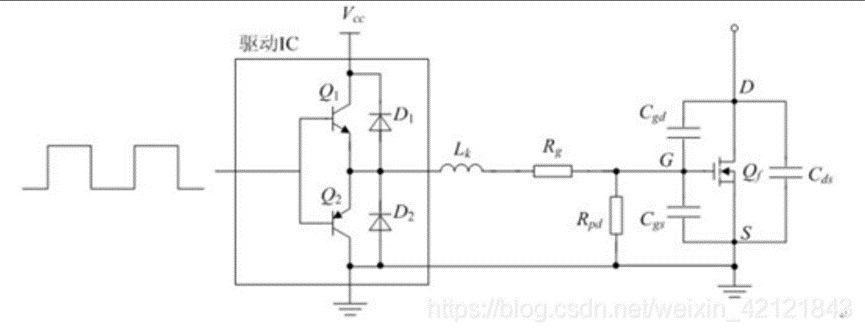

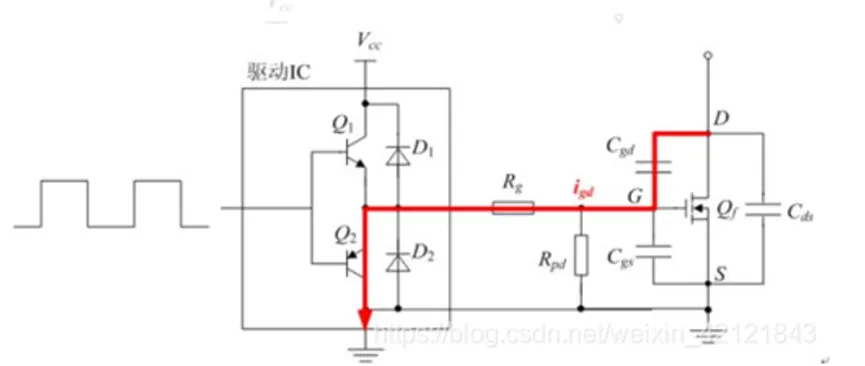

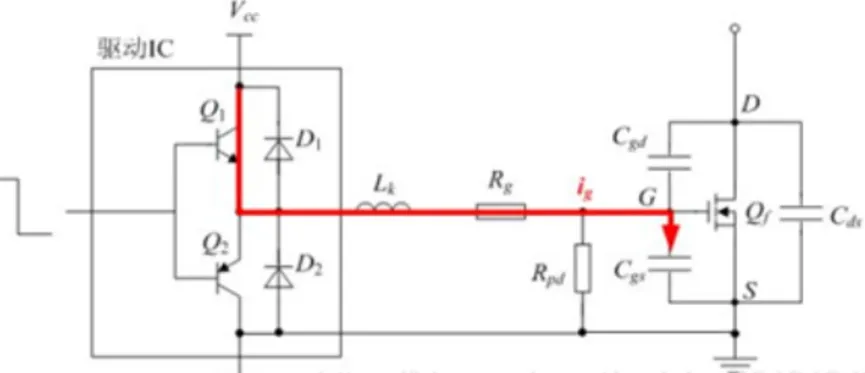

常用的mos管驱动电路结构如图1所示,驱动信号经过图腾柱放大后,经过一个驱动电阻Rg给mos管驱动。其中Lk是驱动回路的感抗,一般包含mos管引脚的感抗,PCB走线的感抗等。在现在很多的应用中,用于放大驱动信号的图腾柱本身也是封装在专门的驱动芯片中。本文要回答的问题就是对于一个确定的功率管,如何合理地设计其对应的驱动电路如驱动电阻阻值的计算,驱动芯片的选型等等。

注:若无特别说明,一般以驱动单个mos为例。

图中的Rpd为mos管栅源极的下拉电阻,其作用是为了给mos管栅极积累的电荷提供泄放回路,一般取值在10k~几十k这一数量级。由于该电阻阻值较大,对于mos管的开关瞬态工作情况基本没有影响,因此在后文分析mos的开关瞬态时,均忽略Rpd的影响。

注意,这个电阻在驱动电路的工作状态下是不起主要作用的,而是在电路停止工作的一瞬间,由于栅极电位是无法确定的,若MOS正在处于被驱动开通的状态,则其栅极会积累一定的电荷,假设此时断电,则处于高阻态的栅源极会导致这部分电荷一直被存储,就有可能会在电路下次启动的瞬间导致MOS的误开通或者栅极的击穿,为防止此类现象产生,则加一颗电阻下拉用于泄放电荷,起到保护栅极的作用。

注2:图中Cgd,Cgs,Cds为mos管的三个寄生电容,在考虑mos管开关瞬态时,这三个电容的影响至关重要。

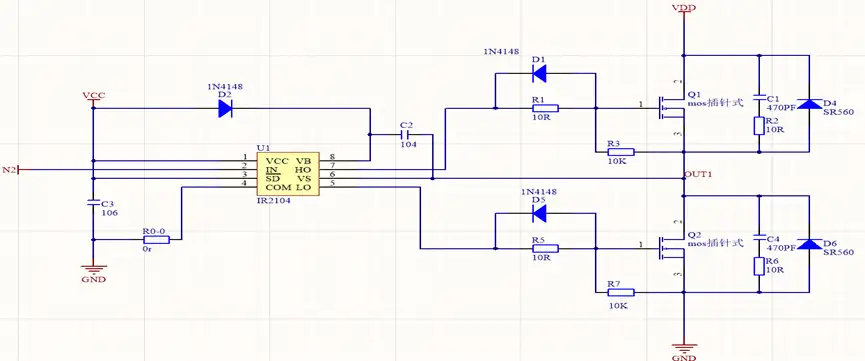

首先,给出一个较为成熟的半桥驱动芯片驱动MOS管的电路,这个电路经实测可以输出几乎不失真的波形,让我们以这个图为例,看看如何一步一步确定每个元器件的值:

关于驱动电阻下限值的计算与分析

驱动电阻下限值的计算原则为:驱动电阻必须在驱动回路中提供足够的阻尼,来阻尼mos开通瞬间驱动电流的震荡。

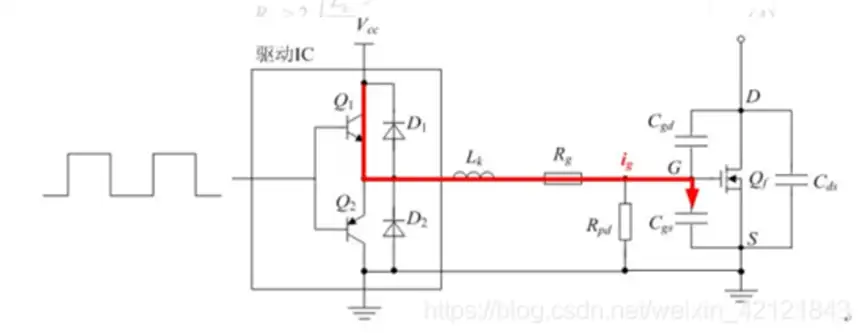

具体电流流向见下图:

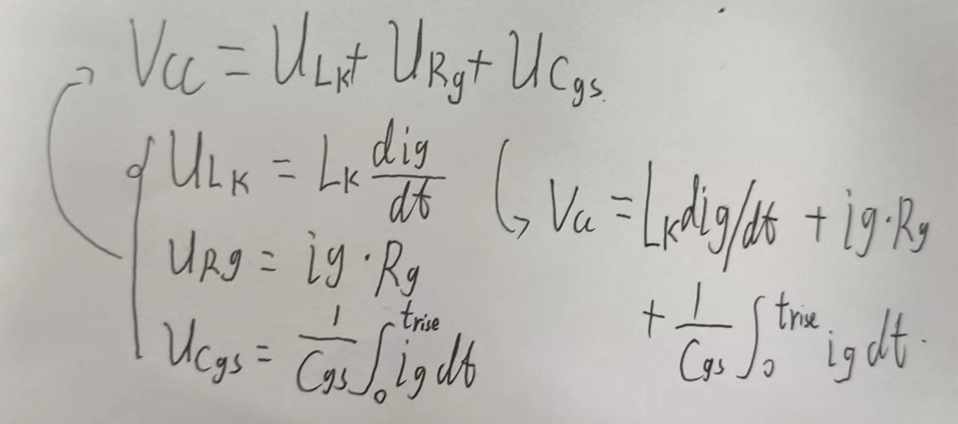

当mos开通瞬间,Vcc通过驱动电阻给Cgs充电,同时忽略Rpd的影响。根据上图,可以写出对于关心回路中的驱动电流列写频域的方程:

𝑠∗𝐿𝑘𝑖𝑔+𝑅𝑔𝑖𝑔+1/(𝑠∗𝐶𝑔𝑠)∗𝑖𝑔=𝑉𝑐𝑐/𝑠

化简、整理后,得到典型二阶系统的形式

𝑖𝑔=𝑣𝑐𝑐/(1/𝐿𝑘∗𝑆2+𝑅𝑔∗𝑆+1/𝑐(𝑔𝑆))

其中:

Rg:驱动电阻的电阻值

Cgs:MOS的GS间的寄生电容

Lk:驱动回路感抗(一般取50nH)

最终得到二阶系统阻尼比为

ξ=1/2𝑅𝑔√(𝑐𝑔𝑠/𝐿𝑘)

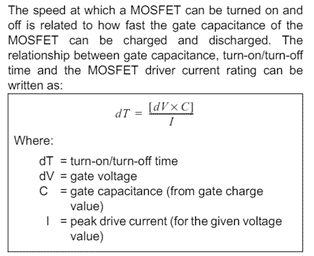

知识补充:mos的寄生电容

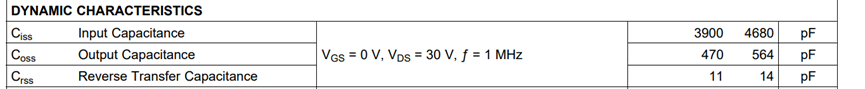

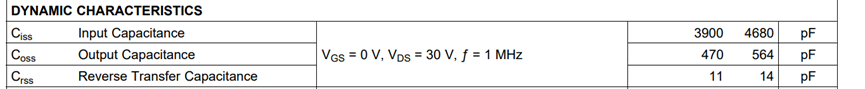

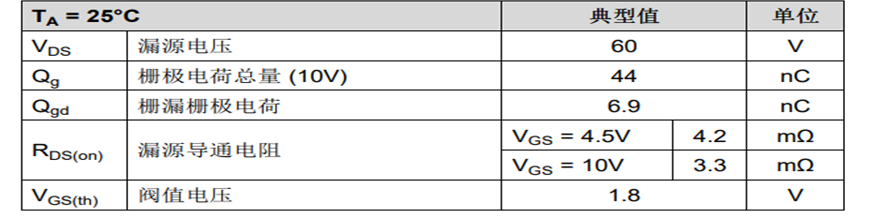

Mos的三个电极之间两两存在寄生电容,一般以Cxx命名,xx为电极名称,如Cgs就是栅源之间的寄生电容,但在MOS管的数据手册中很少出现单独的这三个数据,一般都是以这样的方式:

其中,他们是这样的关系

输入电容:Ciss=CGS+CGD;漏源短接,测得栅源之间的电容值

输出电容:Coss=CDS+CGD;栅源短接,测得漏源之间的电容值

反向传输电容:Crss=CGD;即栅漏电容。

Ciss对开关状态影响大,其实mos的开通与关断本质上可以理解为对这个的寄生电容的充放电,当其被充电至MOS的开通阈值电压,mos将开通,当其电压降落至开启阈值电压以下,mos也就关断了。

Coss主要在软开关应用中需要考虑它是否会引起震荡。

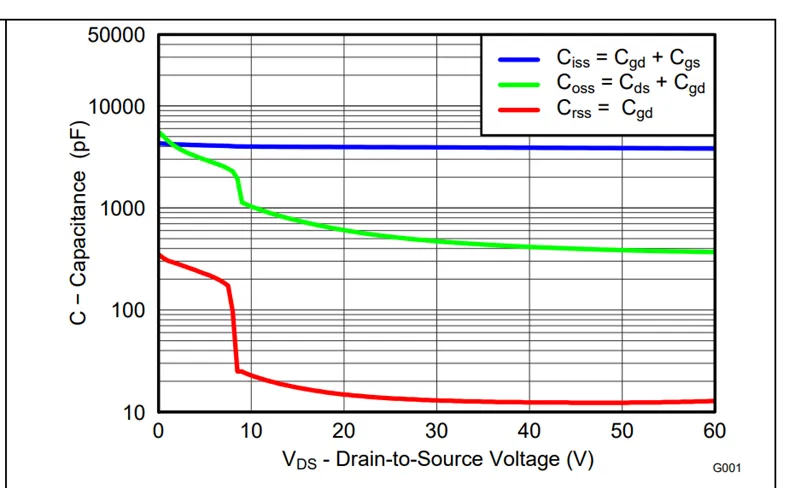

Cres主要影响输入阶跃信号下电平的上升下降时间(有点像压摆率)与处于开关状态下MOS的开通关断时间,注意这三个值由两个(除Ciss)都与Vds有很大关系,随着Vds的增大而减小。

///

为了不引起回路中电流的震荡,需要阻尼比大于1,经过整理后,公式化为:

𝑅𝑔≥2√(𝐿𝑘/𝐶𝑔𝑠)

这就是我们需要的驱动电阻计算公式的一部分。

实际应用,以CSD18532为例:

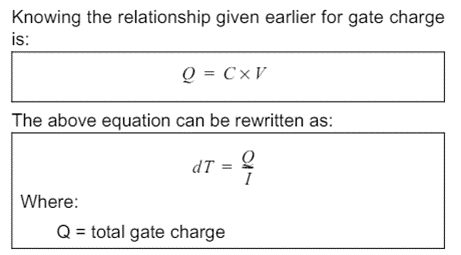

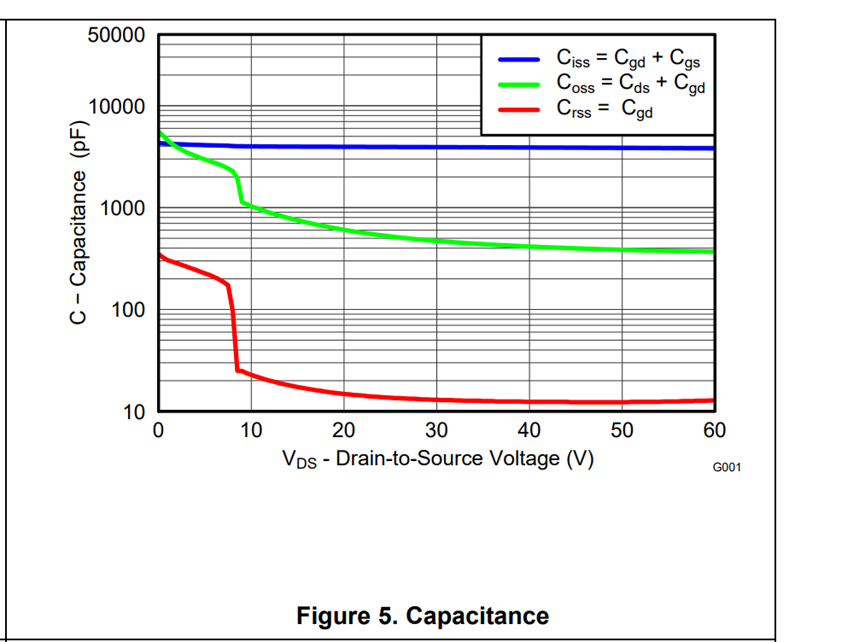

1、打开手册,找到我们需要的电容值

2、通过计算得到需要的寄生电容值

注意!不要只看标称值,要看图表,我们的电池电压在8V左右,所以在图中Crss取值大概在60-75pF之间。

Cgs=Ciss-Crss=3900pf-65pf=3.85nf

一般取Lk=50nH;

注:Lk是驱动回路的感抗,一般包含mos管引脚的感抗,PCB走线的感抗,驱动芯片引脚的感抗等,其精确的数值往往难以确定,但数量级一般在几十nH左右。

计算得到:

Rg≥7.18Ω

至此,驱动电阻的下限值得以确定。

驱动电阻的上限值

驱动电阻上限值的计算原则为:防止mos管关断时产生很大的dV/dt使得mos管再次误开通。

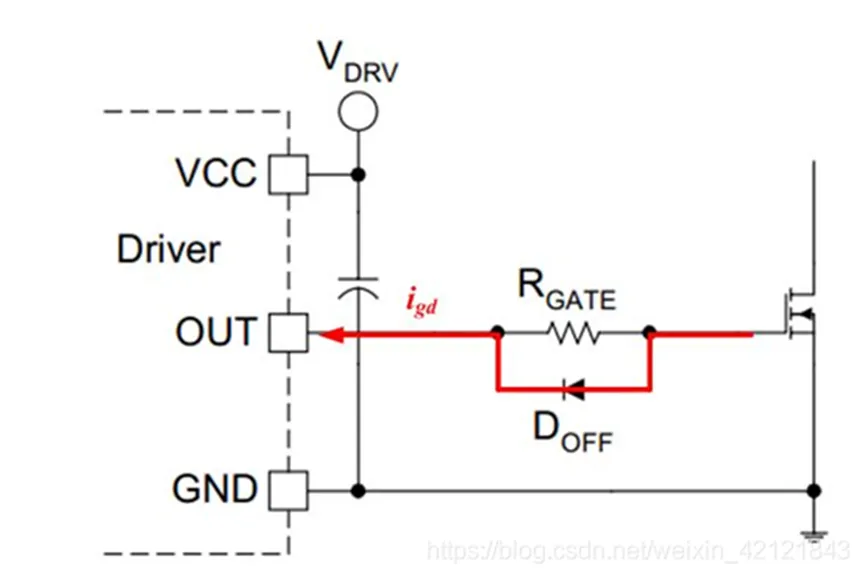

当mos管关断时,其DS之间的电压从0上升到Vds(off),因此有很大的dV/dt,根据公式:i=C*dV/dt,该dV/dt会在Cgd上产生较大的电流igd,如图3所示。

图3 mos关断时的对应电流

一个可能会有的疑问:为什么是Vds?

按照这种思路,当mos关断时,产生dV/dt的是漏源DS两极,又因为漏源两级之间的寄生电容是Cds,那么不应该产生一个从D到S的电流嘛,或者如果要在Cgd上产生电流,不应该使用栅漏两级之间的电位差吗?

这种想法是不正确的,不过要彻底讲清楚为何不是这样,还得从mos的开通关断条件入手。

自行了解图腾柱原理的驱动IC内部电路与开启关断的等效电路

很明显,Cgd的靠近漏极的那个等效极板的电位是VDD,而靠近栅极的那个极板的电位是驱动器的驱动电压加上一个接近VDD的电压(也就是Vdrive+VDD-I*Rgs(on));当驱动器的输出电平从“1”变成“0”时,首先在驱动器内部,其互补输出极的下管开通,输出端输出“0”驱动电平,等效栅极与源极相连。这时Cgd的漏极端电位还是VDD,但另一端则等效变成了与源极相同的电位,在这个模型中,则是与GND相连接的0V,正是这个电位的转换导致了电流的产生。

换句话说,是驱动输出的电位变化导致了MOS的开通关断,在分析时一定要理清先后顺序与逻辑因果关系。

第二个可能会有的疑问:dt为什么是MOS的关断时间?

如果按照上述理论,那么应该是驱动IC互补输出极的下管的开通时间才是我们所需要的dt,毕竟电流回路流经的不是mos而是从电容经过驱动IC流入GND,并且产生dv的根本原因还是驱动IC下管的开通所导致的,但我们为何在公式里使用的却是MOS的关断时间呢?

其实还是驱动逻辑顺序的问题。

首先,是驱动IC内部互补输出极的下管导通才导致了mos的开关状态发生了变化,也就是在产生dv/dt的这一个极短的时刻附近,驱动中负责产生回路的下管就已经是存在通路,并且正在逐渐趋向于完全导通的了,这时候虽然回路是由驱动芯片构建的,但不能等效为有开关动作的全响应过程,故不应该使用驱动IC的上升/下降时间作为式中的dt。

那么既然是渐开的等效通路,dt又应该由什么来决定呢?

乍一看没有头绪,因为这个动态过程过于复杂,涉及到的变量太多,让我们不妨先计算一下以电容为研究对象回路的时间常数,然后根据这个最直接通路的时间常数的数量级去分析其可能会影响到的过程。

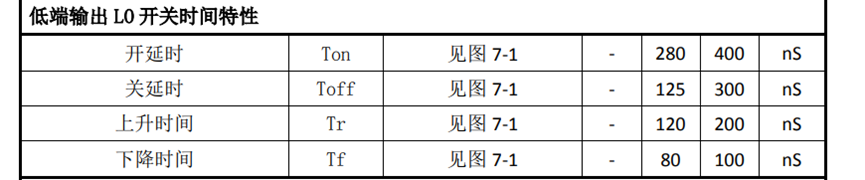

首先,以EG2104驱动csd18532为例,设定工况为8v工作电压,半桥下管。

从2104手册中可以查到,其上升时间为80ns/100ns(标况/最大),电容Cds=Crss=65pF,以驱动回路为研究对象,则等效阻抗为驱动电阻与驱动IC导通电阻和回路阻抗之和,但后两项最大值也在毫欧级别,与驱动电阻Rg差了至少两个数量级,则在此条件下可以忽略不计,即:R=Rg,在这里我们取典型值的最小/最大值Rg=10Ω/100Ω(MIN/MAX)进而得到一个时间区间。

电容原则上为驱动回路寄生电容与Cgd串联,但在这里为突出研究对象为Cgd(其本身值并不大)故选用C=Cgd

有了这两项数据,可以计算得到时间常数

τ=𝑅∗𝐶

约为6.5*10-10/6.5*10-9秒即650ps/6.5ns(MIN/MAX), 这个值是远远小于驱动IC互补输出极的下管开通时间的,但是却与MOS的下降时间较为接近。

顺便插一句嘴,这也是为啥寄生电容上的电荷在正常工作周期内不会通过栅源之间的电阻Rpd来与地平面构成放电回路,因为这颗电阻的阻值一般在10kΩ级别,导致其时间常数将会很大,在以微秒甚至纳秒计算的开关周期内可以忽略不计。

现在再让我们回到一开始的问题上去:为什么是计算dv/dt时使用的时间是关断时间。

2024.05.10更新:dv/dt的解释

当然不是因为这两个数值仅仅是差不多而选择了后者作为dt的取值,而是由于此处所考虑的电容cgd,在驱动芯片的互补输出级下管联通,也就是驱动管子关闭的时刻时,是等效并联在场效应管的GD两端的,而这两端电位差的变化时间其实就是管子从开通

Vgd=(Vdrive+VDD-I*Rgs(on))-(VDD)

=Vdrive-I*Rgs(on)

≈Vdriv

到管子关断

Vgd=(0)-(VDD')

=-VDD'

时产生的电压变化,在Ggd等效电容上感应出的一个电流,不是等效电容放电产生的电流。这也就意味着这个电压变化过程(dt)时间,是开关管关断的时间。

/*此处的VDD与VDD'是不同的,VDD是管子开通(等效接地)后,GND电压值加上电流流过管子产生的压降组成的一个接近0V的电压;而VDD'是管子关断后,功率母线的电压值经过负载传递到管子上的电压*/

这是之前的解释,存在不合理的地方,现已重新解释,改正之前的原文如下

驱动回路在不产生震荡情况下,我们关心的是如何使得其关断过程中不受到电位抬升产生的影响,故采用了可能会产生问题的最大的时间区间(也就是mos的理论关断时间)作为考虑问题的时间基础。或者换句话说,为啥是下降时间?因为我们在关心的这段时间中,如果以其作为dt来计算的结果没有问题,那么就足够证明系统的稳定性了。

顺便说一下这个dt,其实这个时间应当由栅极总电荷与峰值驱动电流共同决定,不过近似计算中可以直接用数据手册中的值来确定。

节选自AN799 Matching MOSFET Drivers to MOSFETs

该电流igd会流过驱动电阻Rg,电流在流经电阻时会在其两侧引入电势差,而这个出现在驱动电阻Rg右侧的被抬升的电位将会在mos管GS之间又引入一个电压,当该电压高于mos管的门槛电压Vth时,mos管会误开通。为了防止mos管误开通,应当满足:

ⅆⅆ𝐶𝐺𝐷∗ⅆ𝑣/ⅆ𝑡∗𝑅𝑔<𝑉𝐺𝑆𝑡ℎ

上式给出了驱动电阻Rg的上限值,其中中Cgd为mos管gd的寄生电容,VGSth为mos管的门槛电压,均可以在对应的datasheet中查到,dV/dt则可以根据电路实际工作时mos的DS电压和mos管关断时DS电压上升时间(该时间一般在datasheet中也能查到)求得。

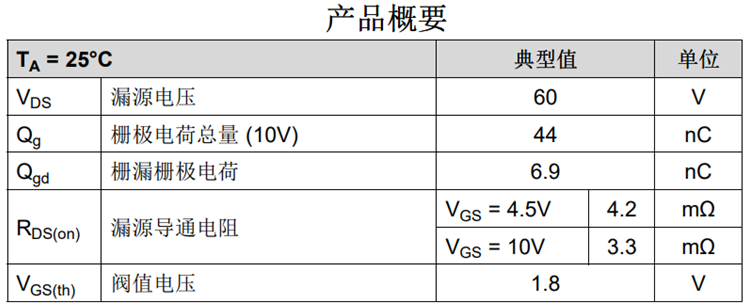

实际应用,以CSD18532为例:

首先,我们要找出计算Rg所需要的数据,这包括了栅漏寄生电容(Cgd),工作条件电压(dV),关断时间(dt),还有MOS的最小开启电压Vgsth。

从数据手册中查询得到:

Cgd=Crss,从上个计算中得到大概8v工作电压下的Crss大概是是65pF。

同样的,从数据手册中查找到:MOS关断时间tf(fall time)为5.6ns

对于Vgs(th),从手册中可以查到是1.8V。

经过计算,很容易得到:Rg<17.4Ω

改进电路

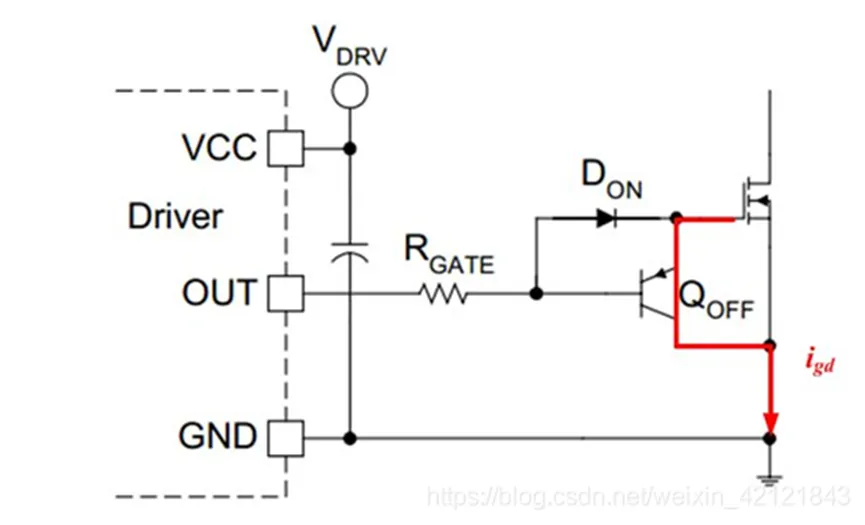

从上面的分析可以看到,在mos管关断时,为了防止误开通,应当尽量减小关断时驱动回路的阻抗。基于这一思想,下面再给出两种很常用的改进型电路,可以有效地避免关断时mos的误开通问题。

图4 改进电路1

图4给出的改进电路1是在驱动电阻上反并联了一个二极管,当mos关断时,关断电流就会流经二极管Doff,这样mos管gs的电压就为二极管的导通压降,一般为0.7V,远小于mos的门槛电压(一般为2.5V以上),有效地避免了mos的误开通。

图5 改进电路2

图5给出的改进电路2是在驱动电路上加入了一个开通二极管Don和关断三级管Qoff。当mos关断时,Qoff打开,关断电流就会流经该三极管Qoff,这样mos管gs的电压就被钳位至地电平附近,从而有效地避免了mos的误开通。

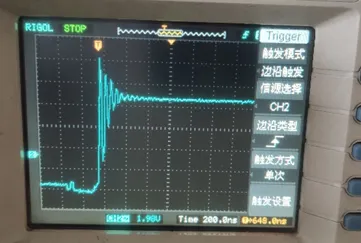

驱动电阻阻值的选择

根据1.1节和1.2节的分析,就可以求得mos管驱动电阻的上限值和下限值,一般来说,mos管驱动电阻的取值范围在5~100欧姆之间,那么在这个范围内如何进一步优化阻值的选取呢?这就要从损耗方面来考虑,当驱动电阻阻值越大时,mos管开通关断时间越长,在开关时刻电压电流交叠时间久越大,造成的开关损耗就越大(如图7所示)。所以在保证驱动电阻能提供足够的阻尼,防止驱动电流震荡的前提下,驱动电阻应该越小越好。

比如通过计算得到驱动电阻的下限为5欧姆,上限为100欧姆。那么考虑一定的裕量,取驱动电阻为10欧姆时合适的,而将驱动电阻取得太大(比如50欧姆以上),从损耗的角度来讲,肯定是不合适的。

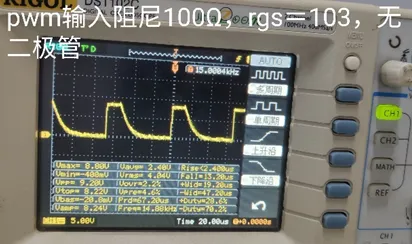

图6无栅极电阻,2104直接驱动mos所产生的高频振铃

图7 pwm(低电平无下拉能力)通过一个100欧姆电阻直接驱动mos

驱动芯片的选型

对于驱动芯片来说,选型主要考虑如下技术参数:驱动电流,功耗,传输延迟时间等,对隔离型驱动还要考虑原副边隔离电压,瞬态共模抑制等等(common mode transient immunity),下面就分别加以介绍。

最大电流

在mos管开通的时候,根据图2,可以得到mos开通瞬间的驱动电流ig为(忽略Lk的影响)

ⅈⅈ>(Δ𝑉𝑔𝑆)/𝑅𝑔

其中ΔVgs为驱动电压的摆幅,那么在选择驱动芯片的时候,最重要的一点就是驱动芯片能提供的最大电流要超过式(7)所得出的电流,即驱动芯片要有足够的“驱动能力”。

同样的,以2s电池(7.4v/8.4v)为驱动电压输入时,需要的最大驱动电流

i=8.4V/10Ω=840ma

如果采用eg2104系列驱动芯片,查看其最大驱动电流,分别为:

| 芯片名 | EG2104 | EG2104S | EG2104M |

| 最大驱动电流 | +1.5A | +1.5A | +0.6A |

| 最大吸收电流 | -1A | -1A | -0.3A |

从这里可以看出,同为EG2104系列,但很明显EG2104M不满足最大驱动电流>840ma的要求,故不能采用EG2104M作为此MOS半桥方案的驱动器。

功耗

驱动功率计算表达式如下:

〖〗𝑃=𝑄𝑔〖∗Δ𝑉𝑔𝑆∗𝑓〗𝑆

其中Qg为栅极充电电荷,可以在datasheet中查到,ΔVgs为驱动电压的摆幅,fs为mos的开关频率,在实际选择驱动芯片时,应选择驱动芯片所能提供的功率大于式(8)所计算出来的功率。

把Qg=44nC、ΔVgs=8.4V、fs一般取15kHz(智能车电机驱动场景)带入公式,得到

Pmax=52.8mW

这个数据我并没有在EG2104的数据手册中找到,不过在ir2104的手册中找到了他的封装功率为1W(直插)0.625W(贴片)

![]()

即使发热等导致效率折半也远远大于52.8mW,明显符合要求。

//这个地方我总觉得计算有问题,但实际打板测试完全满足要求,跟计算一致,也就没有深究········

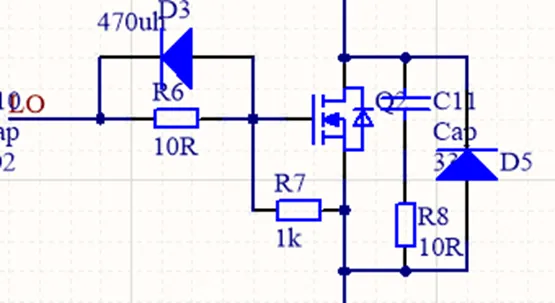

2.外围保护电路

R7作用:防静电影响MOS以及提供电荷的泄放通道,管子的DG,GS之间分别有结电容, DS之间电压会给电容充电,这样G极积累的静电电压就会抬高直到mos管导通,电压高时可能会损坏管子. 同时为结电容提供泄放通道,可以加快MOS开关速度。 阻值一般为几千左右。

其实这个地方可以理解为防止电荷的存在导致GS之间存在电位差,从而导致这个管子在下一次上电时处于不正确的开通状态。

R6和D3作用:在MOS工作于开关状态时,这个回路快速放掉栅极结电容的电荷,栅极电位快速下降,因此可以加快MOS开关速度。另外,高频时, MOSFET的输入阻抗将降低,而且在某个频率范围内将变成负阻,会发生振荡,这个电阻可以减少震荡。R6阻值一般较小,几欧到几十欧左右。

C11,R8和d5作用:MOS有分布电感,关断时会有反峰电压。Rc部分用于吸收尖波,这个设计给这个反峰提供了释放回路。D5是为了防止高电压击穿mos。经实验,去掉该回路后波形有很大的震荡。在全桥或半桥驱动电动机等大电感应用情况时,D5又被称作续流二极管,可以为电感关断的电压反冲提供一个回路。

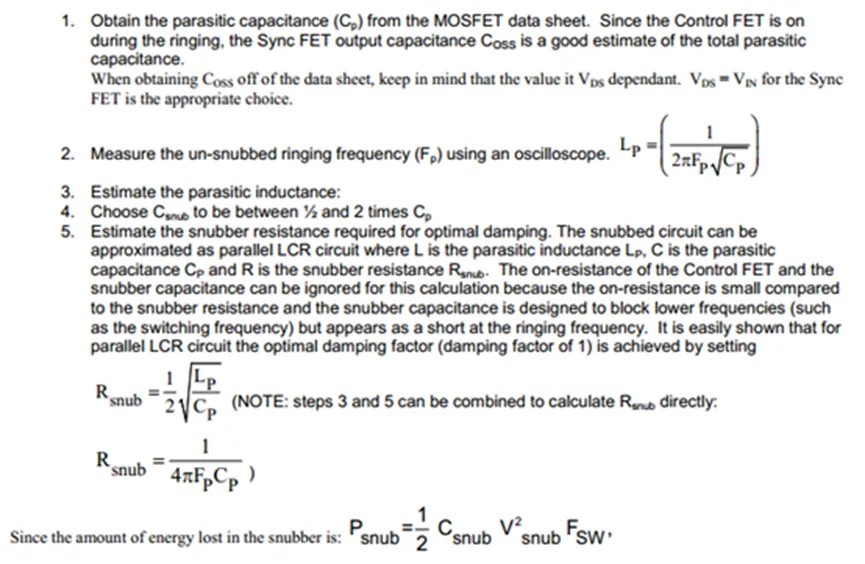

RC吸收设计

●RC吸收的设计方法的难点在于:吸收与太多因素有关,比如分布电感电容、器件等效电感电容、电流、电压、功率等级、di/dt、dv/dt、频率、二极管反向恢复特性等等。而且其中某些因素是很难获得准确的设计参数的。

●工程上一般应该在通过计算或者仿真获得初步参数后,还必须根据实际布线在板调试,才能获得最终设计参数。

给出理论近似公式:

2𝐶𝑜𝑠𝑠≥𝐶𝑠𝑛𝑢𝑏≥1/2𝐶𝑜𝑠𝑠

()𝑅𝑠𝑛𝑢𝑏=1/(4∗𝑝𝑖∗𝐹𝑝∗𝐶𝑝)

关于自举电容的取值与选型

究其本质,自举电容起到了一个储存电荷以等效抬升电位的作用,那么如何选择合适的容量使其工作正常是十分重要的。

给出公式:

𝐶𝑔=𝑄𝐶/𝑉𝐺𝐸

𝑉𝐺𝐸≈𝑉𝐷𝐷−𝑉𝐷𝐵𝑜𝑜𝑇

𝐶𝐵𝑜𝑜𝑇>10∗𝐶𝑔

通过此计算式即可得到最终Cboot的取值。

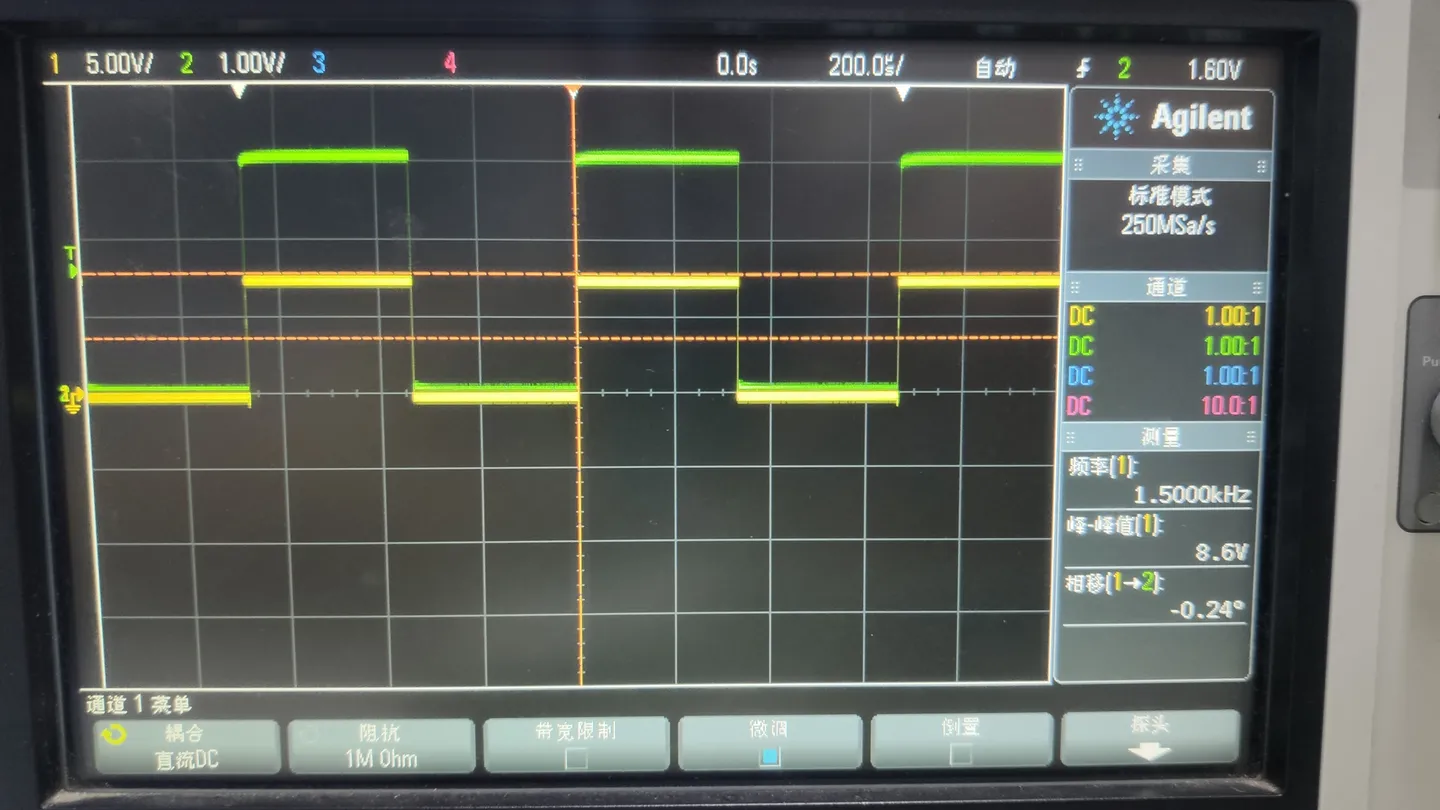

最终的板子与测试波形

测试环境:驱动板输入电压8.4V,占空比0.5,预驱电压8.4V,无升压,带540电机,无堵转。

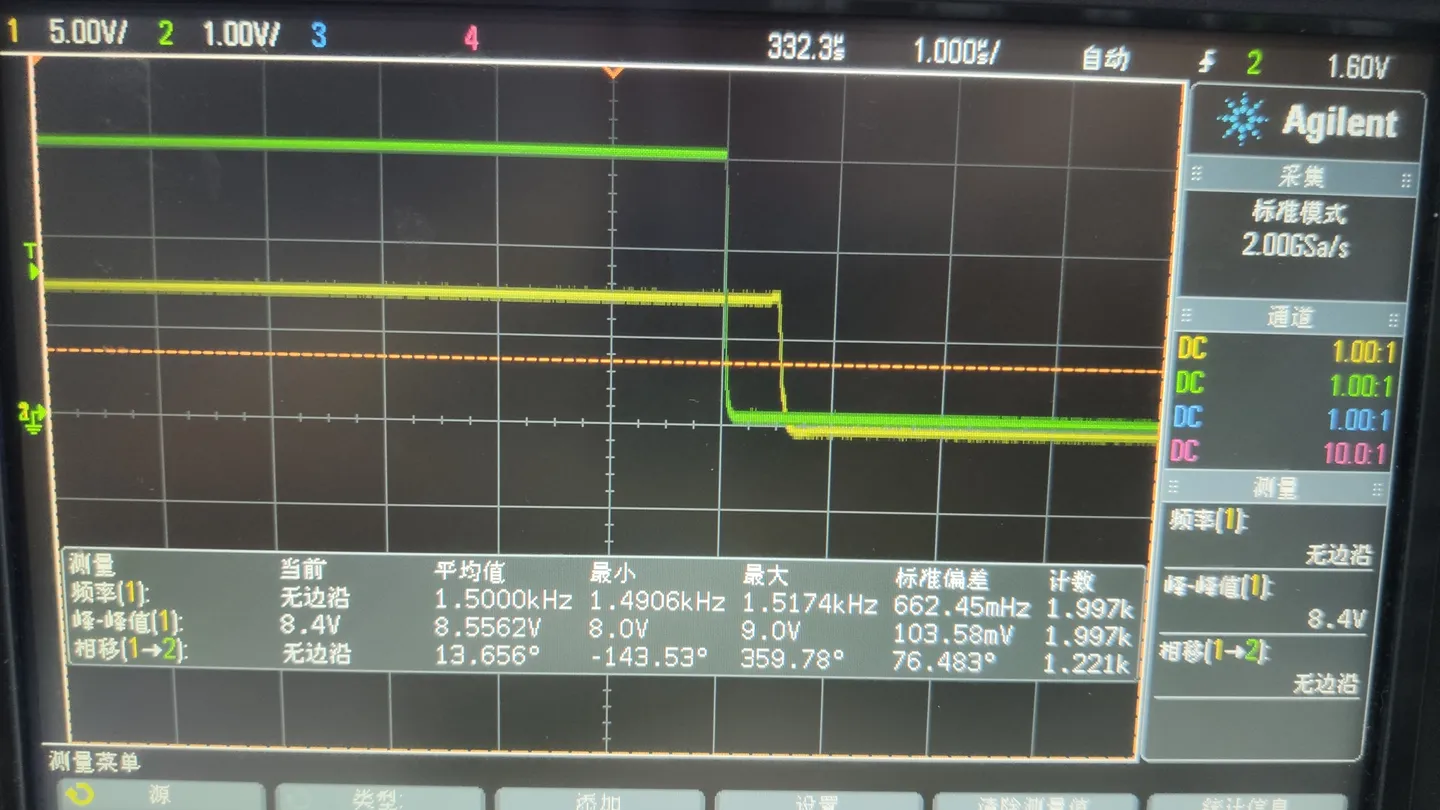

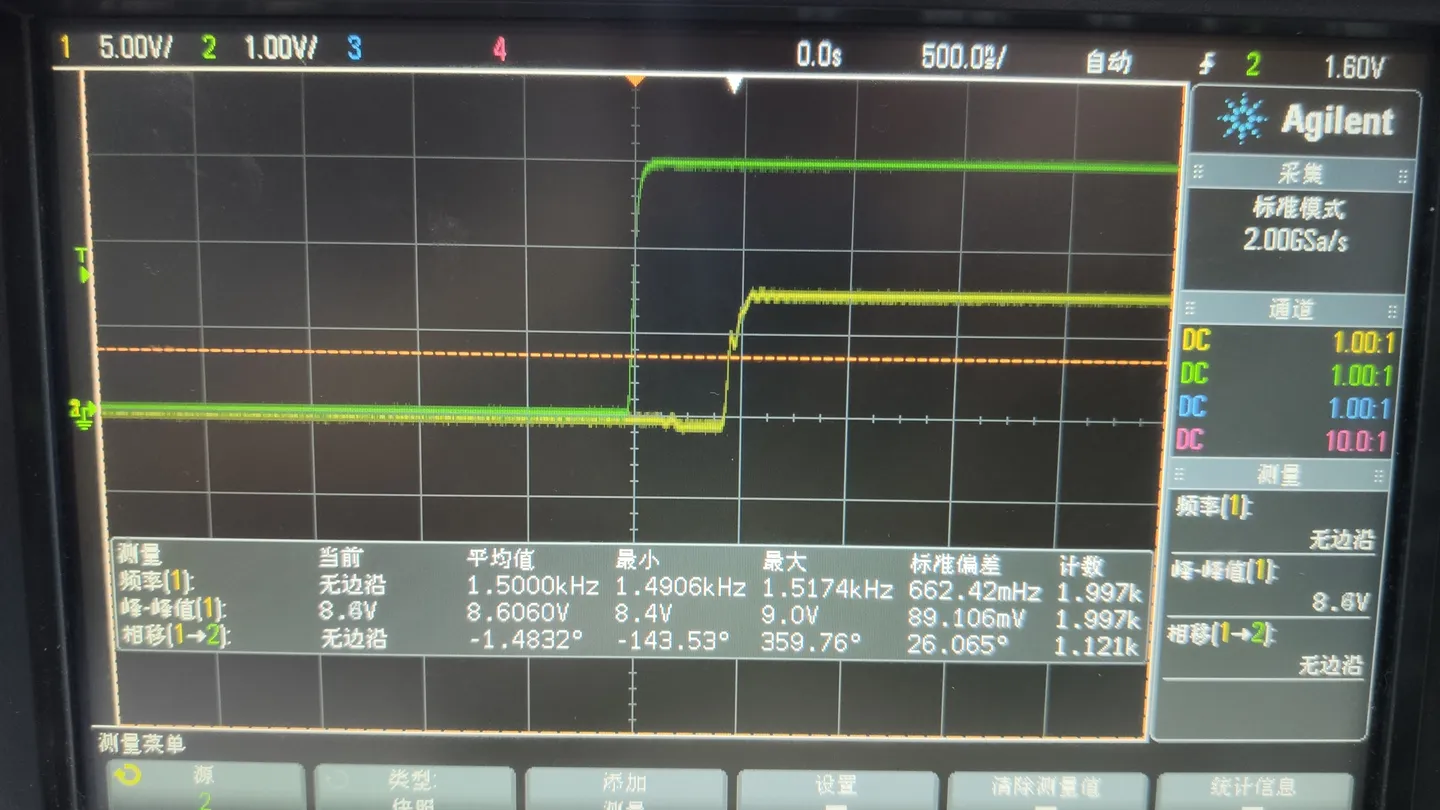

下降沿,绿色为驱动波形,黄色为驱动输出波形

上升沿,绿色为驱动波形,黄色为驱动输出波形

对齐

2023.06.17更新:建模过程

MOSFET开启过程的模型建立

1、首先,分析出控制系统所包含的物理过程,对于MOS的驱动来说,这个过程是是驱动器对于MOS的GS之间的寄生电容充电的过程

1.5、对关心的回路建立电压的微分方程等式(驱动IC内部图腾柱上管的管压降一般较小且随驱动电流变化不大,所以在本建模过程中被忽略)

2、对于关心回路中的驱动电流列写频域的方程,做拉普拉斯变换,结果如下

s*Lk*ig+Rg*ig+[1/(s*Cgs)]*ig=Vcc/s

2979

2979

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?