4.2 组合逻辑电路的分析方法

所谓分析一个给定的组合逻辑电路,就是要通过分析找出电路的逻辑功能。通常采用的分析方法是从电路的输入到输出逐级写出逻辑函数式,最后得到表示输出与输入关系的逻辑函数式。然后用公式化简法或卡诺图化简法将得到的函数式化简或变换,以使逻辑关系简单明了。为了使电路的逻辑功能更加直观,有时还可以将逻辑函数式转换为真值表的形式。

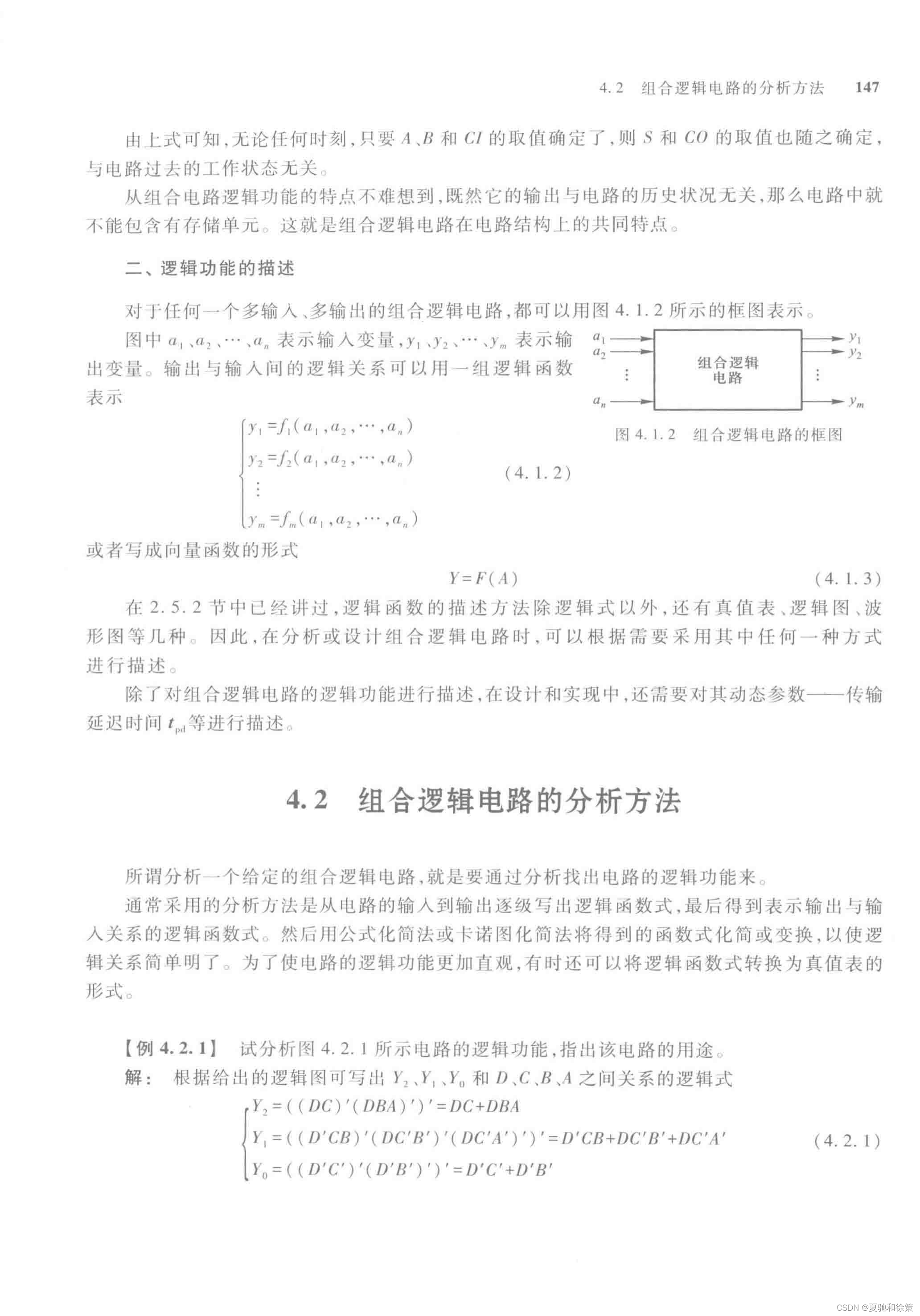

例4.2.1 试分析图4.2.1所示电路的逻辑功能,指出该电路的用途

根据给出的逻辑图可写出 𝑌2Y2、 𝑌1Y1 和 𝑌0Y0 与 𝐷D、 𝐶C、 𝐵B、 𝐴A 之间关系的逻辑式:

𝑌2=𝐷⋅𝐶⋅𝐵‾⋅𝐴‾+𝐷⋅𝐶‾⋅𝐵⋅𝐴‾+𝐷‾⋅𝐶⋅𝐵⋅𝐴Y2=D⋅C⋅B⋅A+D⋅C⋅B⋅A+D⋅C⋅B⋅A

𝑌1=𝐷‾⋅𝐶‾⋅𝐵⋅𝐴+𝐷‾⋅𝐶⋅𝐵‾⋅𝐴+𝐷⋅𝐶⋅𝐵‾⋅𝐴Y1=D⋅C⋅B⋅A+D⋅C⋅B⋅A+D⋅C⋅B⋅A

𝑌0=𝐴‾⋅𝐵‾⋅𝐶‾⋅𝐷‾+𝐴⋅𝐵‾⋅𝐶‾⋅𝐷‾+𝐴‾⋅𝐵⋅𝐶‾⋅𝐷‾+𝐴‾⋅𝐵‾⋅𝐶⋅𝐷‾Y0=A⋅B⋅C⋅D+A⋅B⋅C⋅D+A⋅B⋅C⋅D+A⋅B⋅C⋅D

从上面的逻辑函数式中我们还不能立刻看出这个电路的逻辑功能和用途。为此,还需将式(4.2.1)转换成真值表的形式,得到表4.2.1。

| 输入 | 输出 |

|---|

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?