一、呼吸灯

呼吸灯是指灯光在微电脑的控制之下完成由亮到暗的逐渐变化,使用开发板上的四个led灯实现1s间隔的呼吸灯。

二、代码实现

```c

module pwm_led(

input clk ,

input rst_n ,

output reg [3:0] led

);

parameter CNT_US = 6'd49;//50x20=1000ns=1us

parameter CNT_MS = 10'd999;//1usx1000=1ms

parameter CNT_S = 10'd999;//1msx1000=1s

reg [5:0] cnt_us;

wire add_cnt_us;

wire end_cnt_us;

reg [9:0] cnt_ms;

wire add_cnt_ms;

wire end_cnt_ms;

reg [9:0] cnt_s;

wire add_cnt_s;

wire end_cnt_s;

reg flag;//闪烁标志

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt_us <= 0;

end

else if(add_cnt_us)begin

if(end_cnt_us)begin

cnt_us <= 0;

end

else begin

cnt_us <= cnt_us + 1;

end

end

else begin

cnt_us <= cnt_us;

end

end

assign add_cnt_us = 1'd1;

assign end_cnt_us = add_cnt_us && cnt_us == CNT_US;

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt_ms <= 0;

end

else if(add_cnt_ms)begin

if(end_cnt_ms)begin

cnt_ms <= 0;

end

else begin

cnt_ms <= cnt_ms + 1;

end

end

else begin

cnt_ms <= cnt_ms;

end

end

assign add_cnt_ms = end_cnt_us;

assign end_cnt_ms = add_cnt_ms && cnt_ms == CNT_MS;

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt_s <= 0;

end

else if(add_cnt_s)begin

if(end_cnt_s)begin

cnt_s <= 0;

end

else begin

cnt_s <= cnt_s + 1;

end

end

else begin

cnt_s <= cnt_s;

end

end

assign add_cnt_s = end_cnt_ms;

assign end_cnt_s = add_cnt_s && cnt_s == CNT_S;

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

flag <= 1'b0;

end

else if(end_cnt_s)begin

flag <= ~flag;//1s取反

end

else begin

flag <= flag;

end

end

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

led <= 4'b0;

end

else begin

if(flag)begin//亮pwm

led <= {cnt_s > cnt_ms, cnt_s > cnt_ms,cnt_s > cnt_ms,cnt_s > cnt_ms};

end

else begin//灭pwm

led <= {cnt_s < cnt_ms, cnt_s < cnt_ms,cnt_s < cnt_ms,cnt_s < cnt_ms};

end

end

end

endmodule

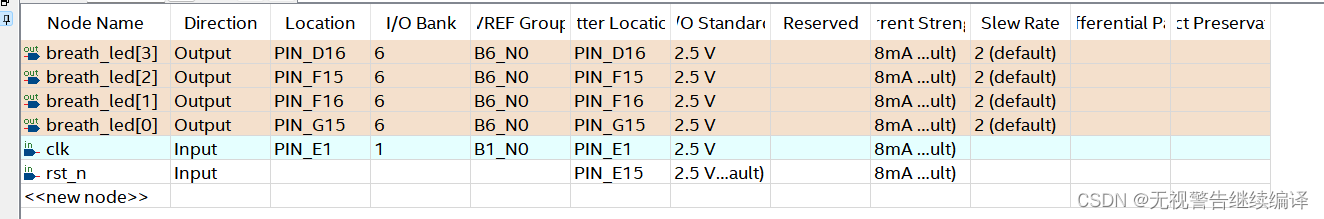

三、引脚分配

该文详细介绍了如何使用Verilog语言编程实现一个呼吸灯效果,通过控制四个LED灯的亮度变化,每秒进行一次亮暗交替。代码中设置了不同时间单位的计数器,以实现1s的周期,并通过取反标志来切换亮灯和灭灯的PWM状态。

该文详细介绍了如何使用Verilog语言编程实现一个呼吸灯效果,通过控制四个LED灯的亮度变化,每秒进行一次亮暗交替。代码中设置了不同时间单位的计数器,以实现1s的周期,并通过取反标志来切换亮灯和灭灯的PWM状态。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?