The Memory Hierarchy

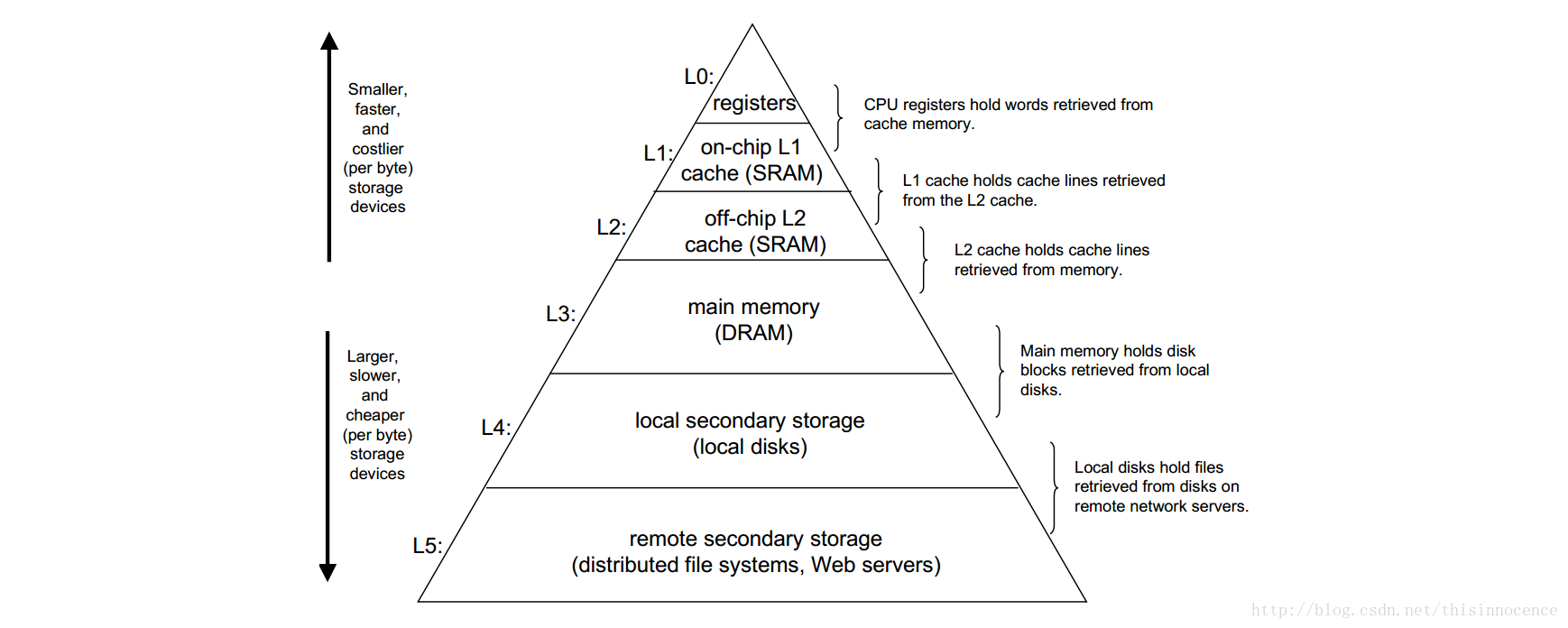

存储系统是有层次的,从快到慢依次是:CPU寄存器、静态SRAM、动态DRAM、磁盘。如下图:

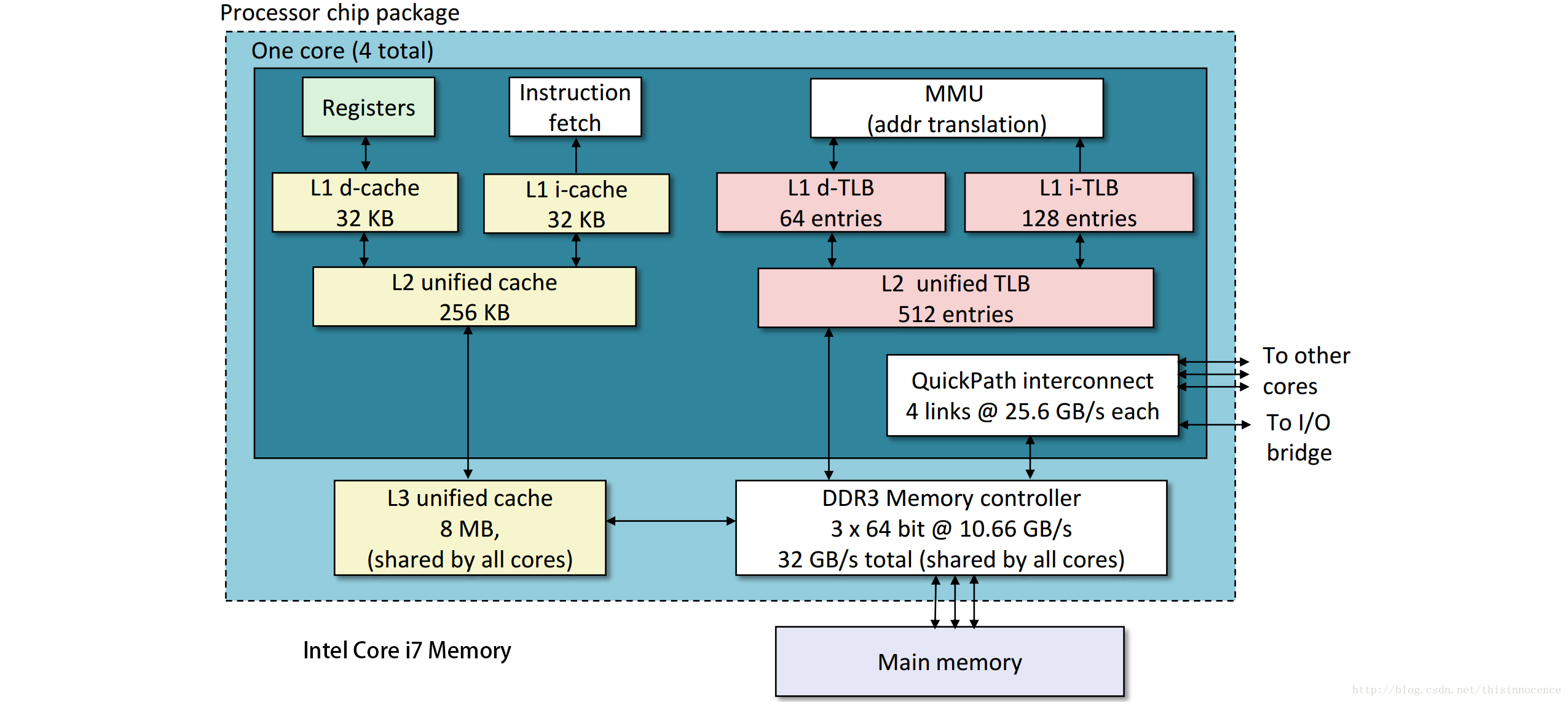

如 Inter Core i7 存储结构如下:

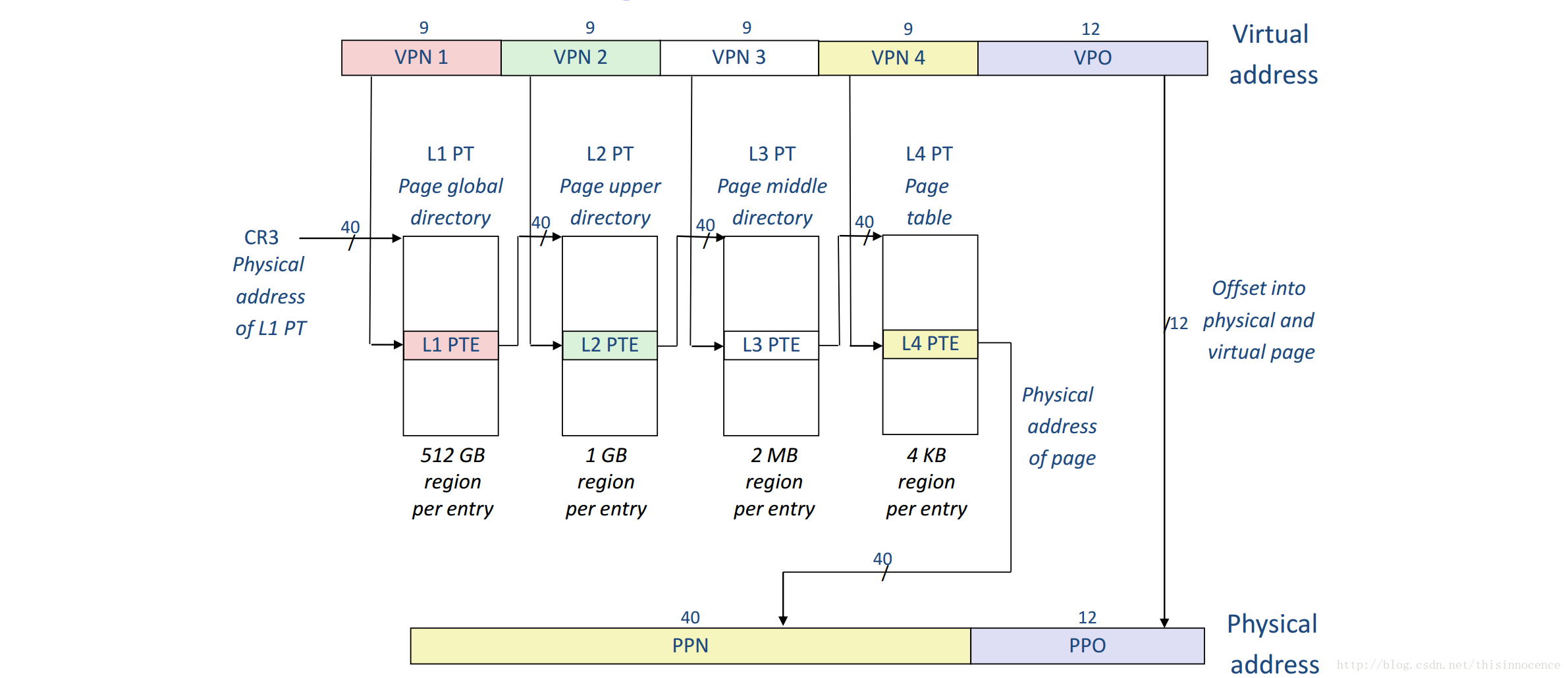

i7的存储架构支持48-bit虚拟地址,52-bit物理地址. Page Size启动时可配置 4KB or 4MB, Linux使用4KB,4-level page table hierarchy。

Segmentation and Paging

在CPU保护模式下,进程使用虚拟地址,这也给每个进程一个大的、一致的私有的地址空间。虚拟地址也简化了程序的链接与加载,代码段、数据段、共享库总是从相同的虚拟地址开始,执行程序时,execve()调用会使内核分配virtual pages给进程,按page从磁盘拷贝代码段数据段到内存。

地址翻译分段与分页相结合,linux更加关注的是分页机制。Linux分段机制使用的很有限,RISC架构的CPU就不支持分段机制,并且分段机制也没有分页机制更灵活。

逻辑地址

-->[Segmentation]-->线性地址(虚拟地址)-->[Paging]-->物理地址Linux分段机制使用的很有限,逻辑地址与线性地址是一致的。

linux下分段机制使用的很有限,仅仅有四种段:用户代码段、用户数据段、内核代码段、内核数据段。相应的段描述符由宏

__USER_CS,__USER_DS,__KERNEL_CS,和__KERNEL_DS分别定义,且所有段都从0x00000000开始。

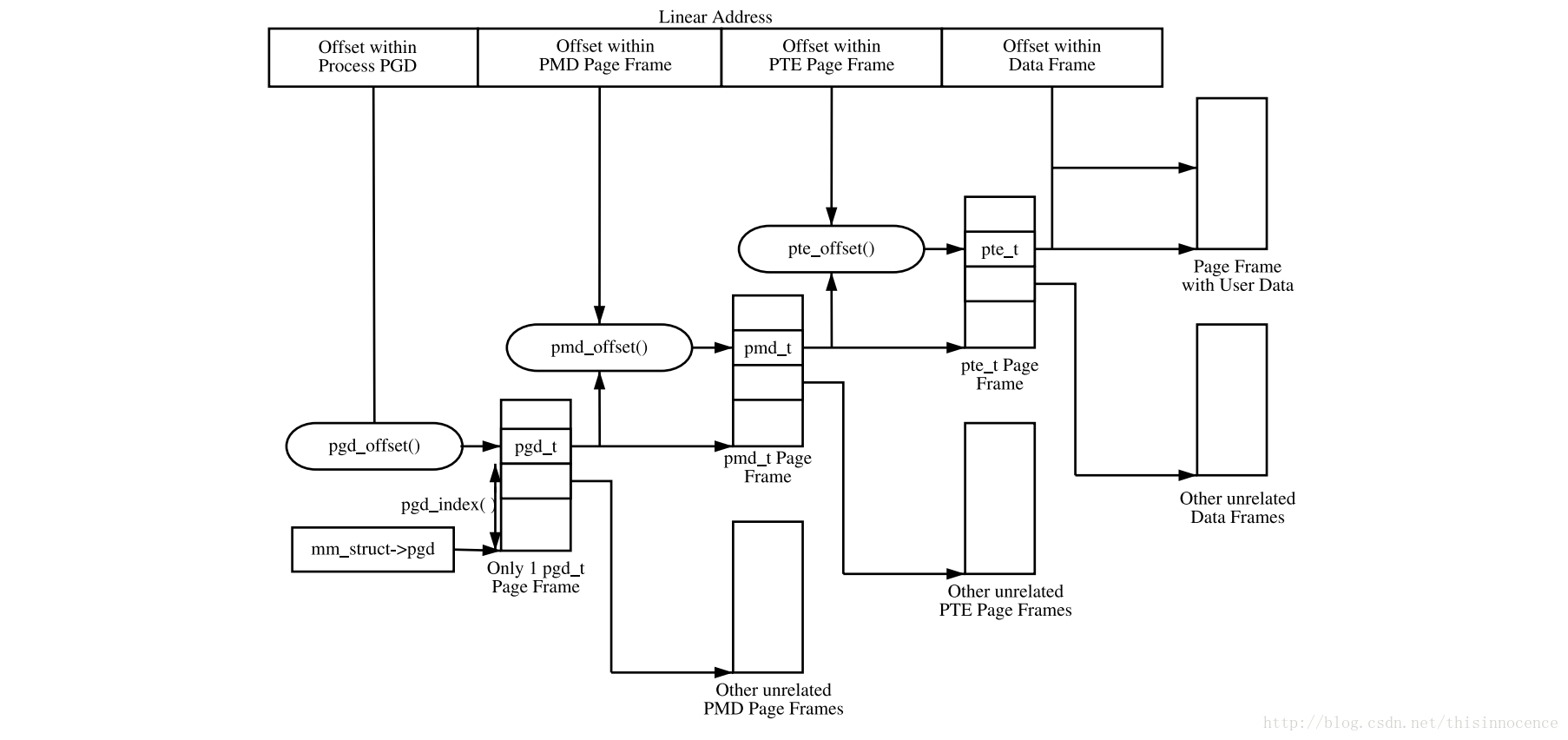

Linux使用分页机制,每个进程都有自己的页表,任务切换就会有页表切换,x86下通过修改控制寄存器CR3完成,CR3控制寄存器是PDBR(Page-Directory Base address Register),加载进程页表通过拷贝mm_stuct->pgd到CR3寄存器完成。

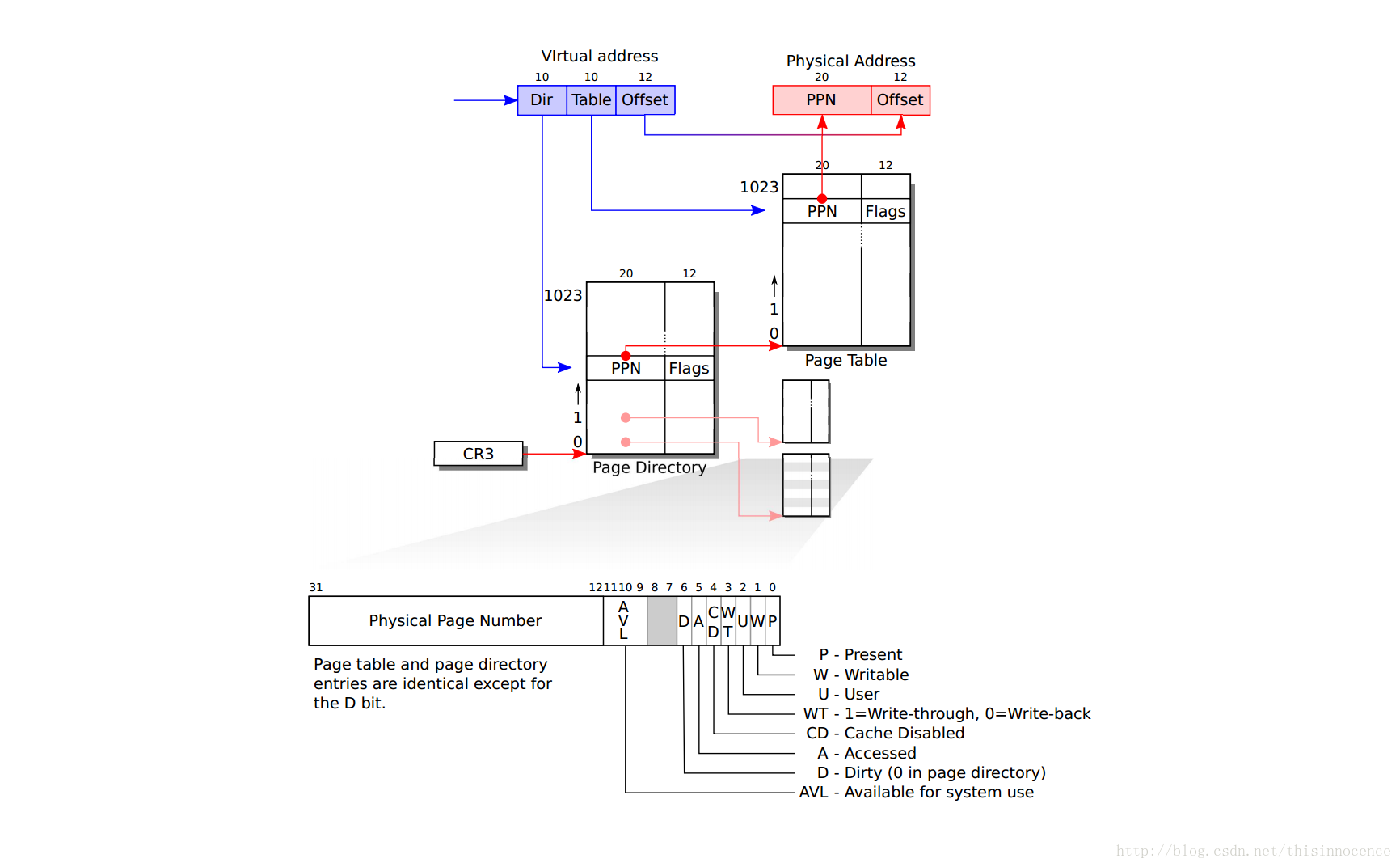

页表可以把虚拟地址页映射为物理地址页,x86 32位系统的机制大致如下(MIT xv6):

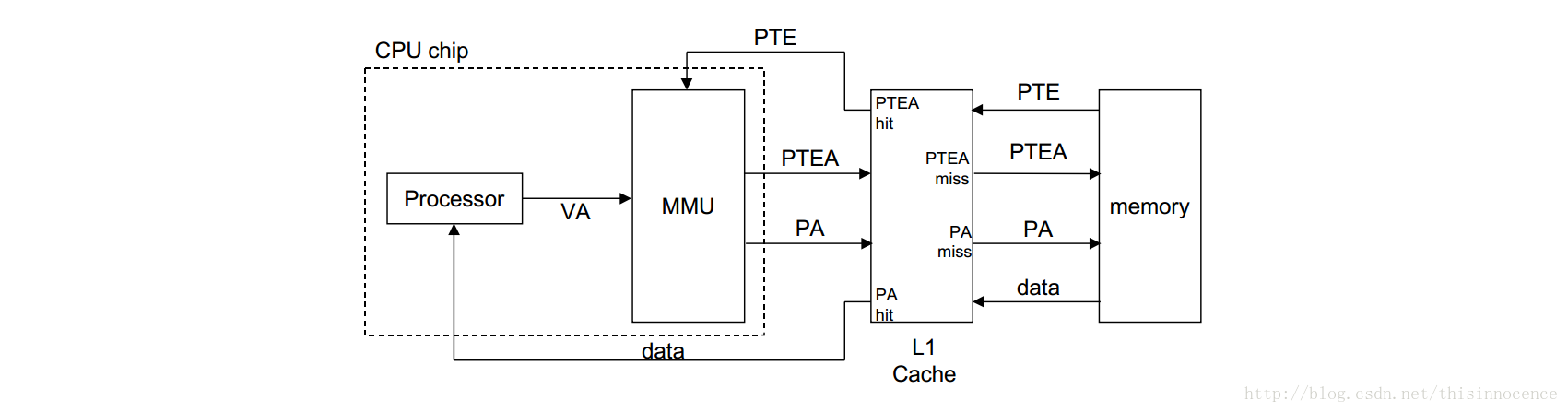

为了加快速度,地址翻译有专门的硬件MMU(Memory Management Unit),MMU中包含了一个小的PTE(Page Table Entry)缓存TLB(Translation Lookaside Buffer), 大致工作原理如下图:

举个多级页表的例子,Inter i7页表翻译,采用了4级页表,如下图:

从操作系统的实现看:

还有很多有意思的细节可以看后面的参考资料。

Reference

Operating Systems: Three Easy Pieces

Xv6, a simple Unix-like teaching operating system

Computer Systems: A Programmer’s Perspective, 3/E (CS:APP3e)

Professional Linux Kernel Architecture

Understanding the Linux® Virtual Memory Manager

Computer Systems Organization

1679

1679

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?