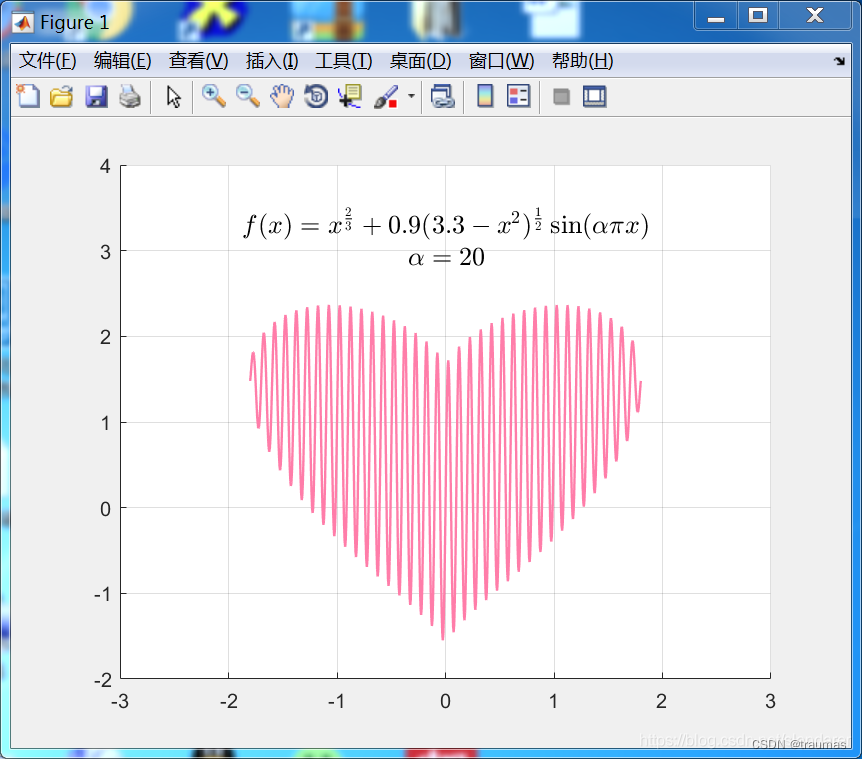

心形函数

具体的matlab代码:

% 定义匿名函数

a= 16;

f=@(x)real(abs(x)^(2/3) + 0.9*sqrt(3.3-x^2) * sin(a*pi*x));

%把离散的整数序列(1, 1024)映射到函数的定义域

for i = 1:1024

j = (i / 1024 -0.5)*2*sqrt(pi);

X(i) = j;

Y(i) = f(j);

end

%把值域映射到0-1023,并且取整

Y = round((Y - min(Y)) / (max(Y) - min(Y)) .* 1023);

%上面的步骤做到了信号的A\D转换

% 打开文件

fid=fopen('heart.coe', 'wt');

%按照coe文件格式输出数据

fprintf(fid, 'MEMORY_INITIALIZATION_RADIX=16;\n');

fprintf(fid, 'MEMORY_INITIALIZATION_VECTOR=\n');

%输出数据

for i = 1 : 1023

fprintf(fid, '%x,\n', Y(i));

end

% 单独处理最后一行

fprintf(fid, '%x;\n', Y(1024));

%关闭文件

fclose(fid);

其中a是可以调节的,计算数据保存在后缀为“coe”的heart.coe文件中。

文件内部为:

MEMORY_INITIALIZATION_RADIX=16;

MEMORY_INITIALIZATION_VECTOR=2c2 2ca 2d6 2e3 2f4 306 319 32e 342 355 367 377 384 38e 394 396 393 38d 382 372 35f 349 330 315 2f9 2dd 2c1 2a7 28e 27a 268 25c 254 251 254 25c 269 27b 292 2ad 2ca 2ea 30a 32b 34b 369 384 39c 3af 3bc 3c4 3c6 3c1 3b7 3a6 38f 374 354 332 30c 2e6 2bf 29a 277 257 23c 225 215 20b 208 20c 217 228 240 25e 27f 2a5 2cd 2f6 320 348 36e 390 3ad 3c4 3d5 3df 3e1 3dc 3cf 3bb 3a0 37f 359 330 303 2d5 2a7 27b 251 22b 20a 1ef 1dc 1d0 1cc 1d0 1dd 1f1 20d 22f 256 281 2b0 2e0 310 33e 36a 392 3b4 3cf 3e3 3ef 3f2 3ed 3df 3c8 3aa 385 35b 32c 2fa 2c6 292 25f 230 205 1e0 1c1 1ab 19d 198 19c 1a9 1bf 1de 203 22e 25e 292 2c7 2fc 330 361 38d 3b3 3d2 3e9 3f7 3fb 3f6 3e8 3d0 3b0 388 35a 326 2f0 2b7 27e 247 213 1e3 1ba 198 17f 16f 169 16d 17a 191 1b1 1d9 208 23c 273 2ad 2e6 31f 354 384 3ae 3d0 3e9 3f9 3ff 3fa 3ec 3d3 3b1 387 356 31f 2e5 2a8 26c 230 1f8 1c5 198 173 157 145 13d 141 14e 166 187 1b1 1e2 219 253 290 2ce 30a 343 377 3a4 3c9 3e5 3f6 3fe 3fa 3eb 3d2 3af 383 350 317 2da 29a 259 21a 1df 1a8 178 151 132 11e 115 117 124 13c 15e 18a 1bc 1f5 233

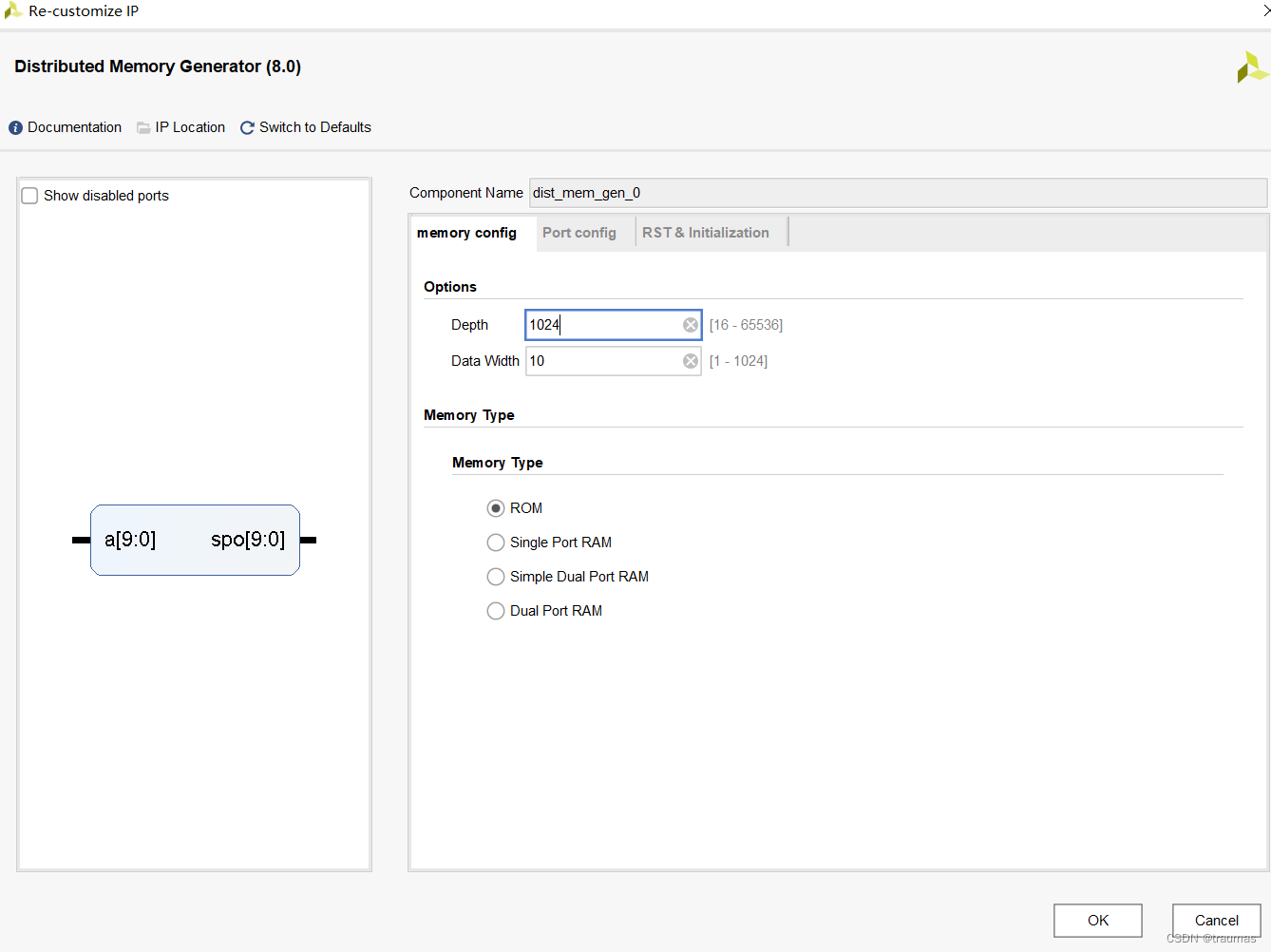

调用ROM

Verilog代码为:

module heart(

input clr,

input clk,

output [9:0]heart

);

reg [9:0]counter;

always@(posedge clk or negedge clk)

begin

if(clr == 0)

counter <= 0;

else

counter <= counter + 1;

end

dist_mem_gen_0 your_instance_name (

.a(counter),

.spo(heart)

);

endmodule

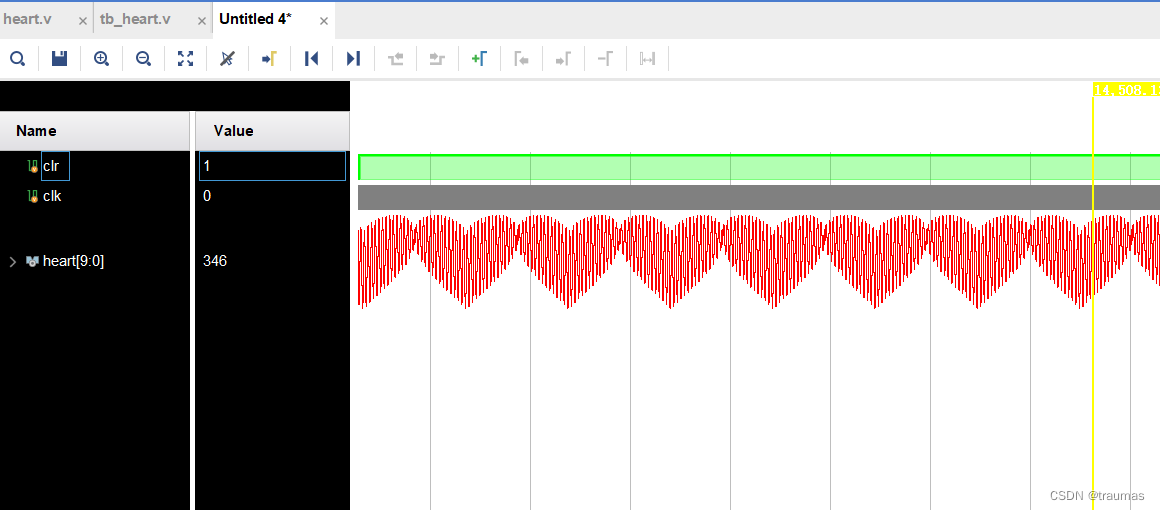

testbench:

module tb_heart(

);

reg clr;

reg clk;

wire [9:0]heart;

heart heart_tb1(

.clr(clr),

.clk(clk),

.heart(heart)

);

initial

begin

clr <= 0;

clk <= 0;

#10 clr <= 1;

end

always #5 clk <= ~clk;

endmodule

仿真出的波形为:

本文介绍了一个使用MATLAB生成心形函数数据并将其转换为适用于硬件描述语言的数据格式的方法。通过MATLAB脚本,将心形函数的计算结果转化为16进制数据并保存至特定格式的文件中。接着,利用Verilog代码实现了一个简单的ROM模块,该模块能够读取这些数据并在时钟信号的触发下输出。

本文介绍了一个使用MATLAB生成心形函数数据并将其转换为适用于硬件描述语言的数据格式的方法。通过MATLAB脚本,将心形函数的计算结果转化为16进制数据并保存至特定格式的文件中。接着,利用Verilog代码实现了一个简单的ROM模块,该模块能够读取这些数据并在时钟信号的触发下输出。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?