monitor的作用是监视DUT的行为,monitor是收集DUT端口数据,将其转换成数据包交给reference model 和scoreboard处理。它的功能主要包括监控端口信息生成数据包、协议时序的检查。

monitor可分为两种monitor,一种是采样输入接口的数据给reference model,我们叫imonitor,这里为什么不用driver的数据包直接给refrence model?有两种考虑:

1,driver中数据包随机的数据不一定直接给的接口,随机之后可能做其他的处理,用monitor采样更合理。

2,除去driver给接口驱动数据之外,用户还可能直接改动接口的数据,这种行为只有monitor能检测到。

另一种monitor就是采样输出接口的数据给reference model,我们叫omonitor。

part1/monitor是UVM monitor的实验,代码2.12是dadd_imonitor的代码,在main_phase中首先等reset_n信号为高,为高之后再采样DADD模块输入接口的数据。

File:dadd_imonitor.sv

Class:dadd_imonitor

task dadd_imonitor :: main_phase(uvm_phase phase);

dadd_item item;

wait(tb_dadd.dadd_if.reset_n);

forever

begin

if(tb_dadd.dadd_if.pcb.dadd_in_en)

begin

item = new();

item.data_en = tb_dadd.dadd_if.pcb.dadd_in_en;

item.data = tb_dadd.dadd_if.pcb.dadd_in;

item.addr = tb_dadd.dadd_if.pcb.dadd_in_addr;

$display("dadd_imonitor,item.addr = %h, item.data = %h",item.addr,item.data);

end

@(posedge tb_dadd.dadd_if.clk);

end

endtask: main_phase

代码2.12 monitor加入后dadd_imonitor代码

代码2.13是dadd_omonitor的代码,在main_phase中首先等reset_n信号为高,为高之后再采样DADD模块输出接口的数据。

File:dadd_omonitor.sv

Class:dadd_omonitor

task dadd_omonitor :: main_phase(uvm_phase phase);

dadd_item item;

wait(tb_dadd.dadd_if.reset_n);

forever

begin

@(posedge tb_dadd.dadd_if.clk);

if(tb_dadd.dadd_if.pcb.dadd_out_en)

begin

item = new();

item.data_en = tb_dadd.dadd_if.pcb.dadd_out_en;

item.data = tb_dadd.dadd_if.pcb.dadd_out;

item.addr = tb_dadd.dadd_if.pcb.dadd_out_addr;

$display("dadd_omonitor,item.addr = %h, item.data = %h",item.addr,item.data);

end

end

endtask: main_phase

代码2.13 monitor加入后dadd_omonitor代码

执行Makefile脚本:

make all

查看log和波形是一一对应的。

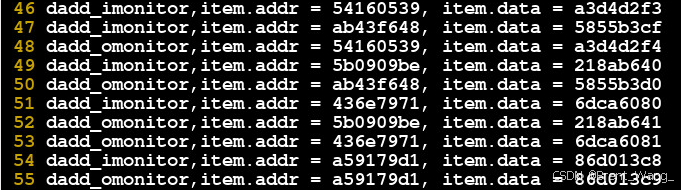

图2.17 monitor实验的仿真log截图

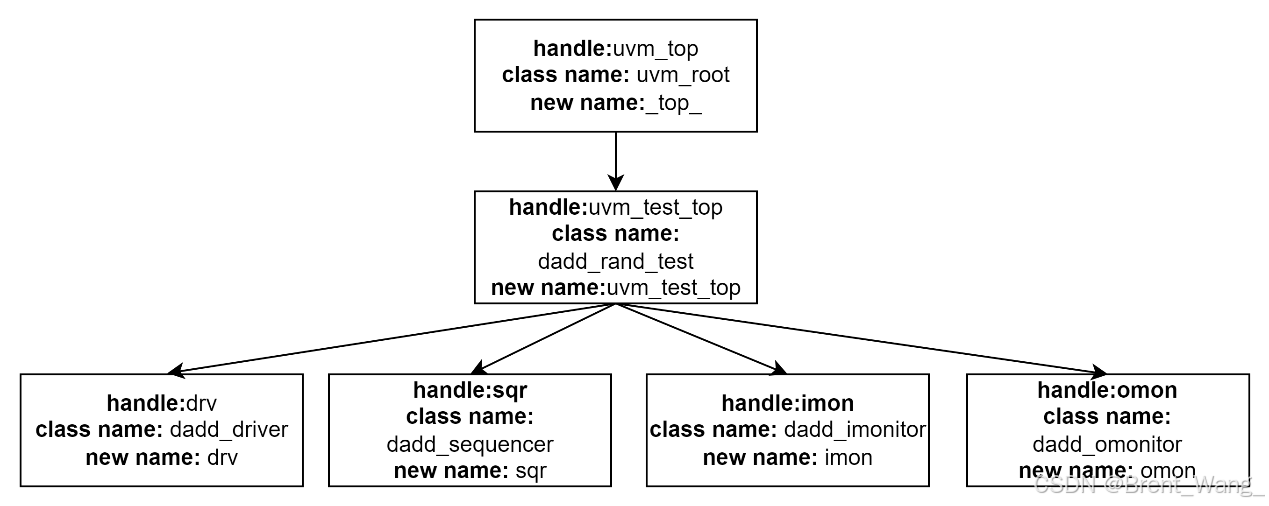

加入imonitor和omonitor之后UVM的树形结构为:

图2.18 monitor加入后UVM树形结构

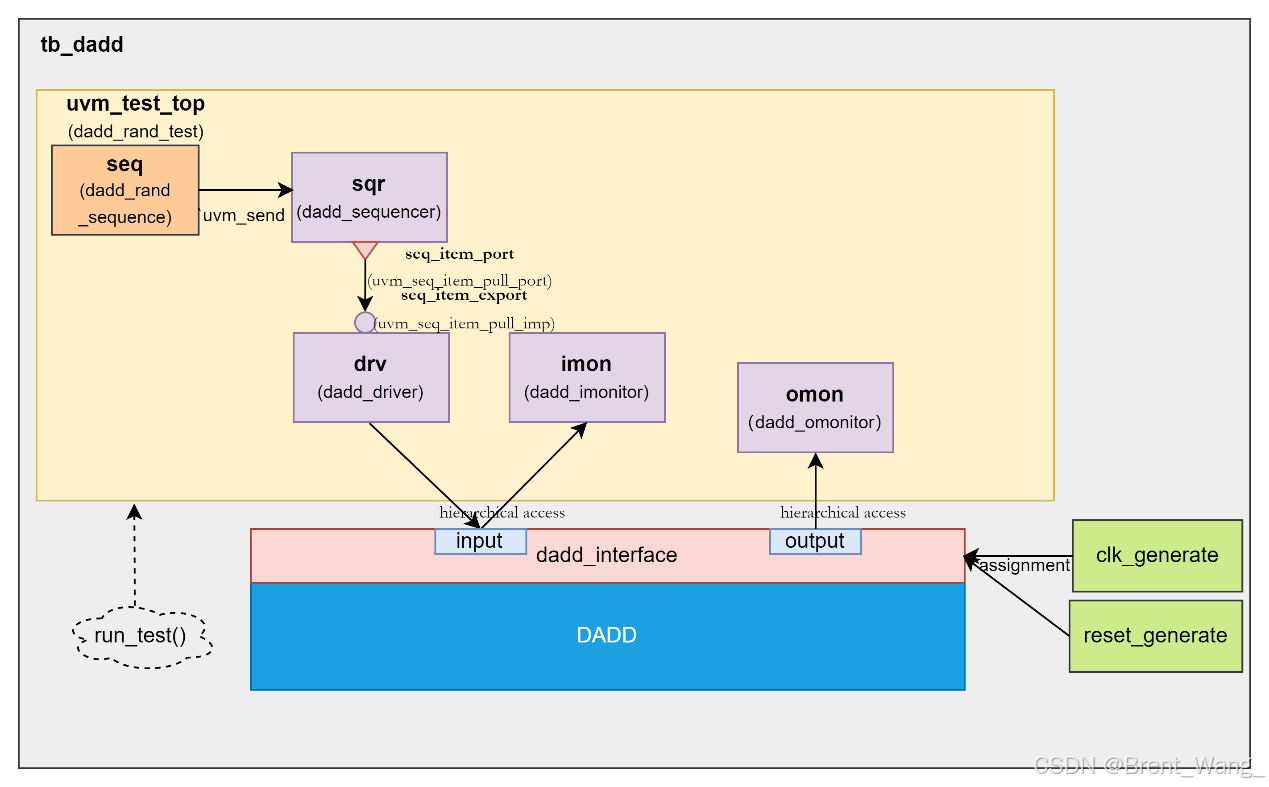

平台结构框图为:

图2.19 monitor加入后UVM平台框图

本书(《UVM实验教程-从平台、脚本到方法学全代码解析-王建利》)及其实验代码已上传至GitHub 访问网址为: https://github.com/brentwang-lab/uvm_tb_gen

8万+

8万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?