前 言

近年来,随着中国新基建、中国制造2025的持续推进,单ARM处理器越来越难胜任工业现场的功能要求,特别是能源电力、工业控制、智慧医疗等行业通常需要ARM+FPGA架构的处理器平台来实现特定的功能,例如多路/高速AD采集、多路网口、多路串口、多路/高速并行DI/DO、高速数据并行处理等。

那ARM+FPGA架构有什么优势?

ARM:接口资源丰富、功耗低,擅长多媒体显示、逻辑控制等。

FPGA:擅长多通道或高速AD采集、接口拓展、高速信号传输、高速数据并行处理等。

因此,ARM+FPGA架构能带来性能、成本、功耗等综合比较优势,ARM与FPGA既可各司其职,各自发挥原本架构的独特优势,亦可相互协作处理更复杂的问题。

对于成本不敏感且通信速率要求的较高分立式ARM+FPGA场合,一般使用PCIe通信接口。但对成本敏感的分立式ARM+FPGA场合,PCIe通信接口则令FPGA芯片成本高居不下。

对于能源电力、工业控制等众多工业领域,真正需要的是性能与成本均具有竞争力的方案,既要求能做到ARM与FPGA的高速通信,又要做到成本最优,并且最好能基于国产方案。

在这种需求背景下,创龙科技提供了基于国产ARM与低成本FPGA高速通信的3种方案。

* 硬件平台介绍(全志科技T3/A40i)

创龙科技TLT3-EVM/TLA40i-EVM是一款基于全志科技T3/A40i处理器设计的4核ARM Cortex-A7国产工业评估板,每核主频高达1.2GHz,由核心板和评估底板组成。T3与A40i两者pin to pin兼容。

评估板接口资源丰富,引出双路网口、双路CAN、双路USB、双路RS485等通信接口,板载Bluetooth、WIFI、4G(选配)模块,同时引出MIPI LCD、LVDS LCD、TFT LCD、HDMI OUT、CVBS OUT、CAMERA、LINE IN、H/P OUT等音视频多媒体接口,支持双屏异显、Mali400 MP2 GPU,1080P@45fps H.264视频硬件编码、1080P@60fps H.264视频硬件解码,并支持SATA大容量存储接口。

核心板采用100%国产元器件方案,并经过专业的PCB Layout和高低温测试验证,稳定可靠,可满足各种工业应用环境。评估底板大部分元器件均采用国产方案,方便用户快速进行产品方案评估与技术预研。

*官方商城选购入口:https://tronlong.tmall.com

本文主要介绍全志科技T3/A40i与紫光同创PGL25G/Xilinx Spartan-6基于SPI、SDIO、CSI的3种高速通信方案,最高通信速率可达到55.1MB/s。

为了简化描述,正文仅摘录方案功能描述与测试结果,详细开发文档(案例源码)请长按下方二维码识别进入下载资料。

备注:目前,创龙科技已推出T3/A40i+PGL25G全国产一体化工业核心板方案,国产化率100%(连接器亦为国产),需要的请自行咨询,文末有联系方式。

图 3 T3/A40i+PGL25G全国产工业核心板

(国产化率100%)

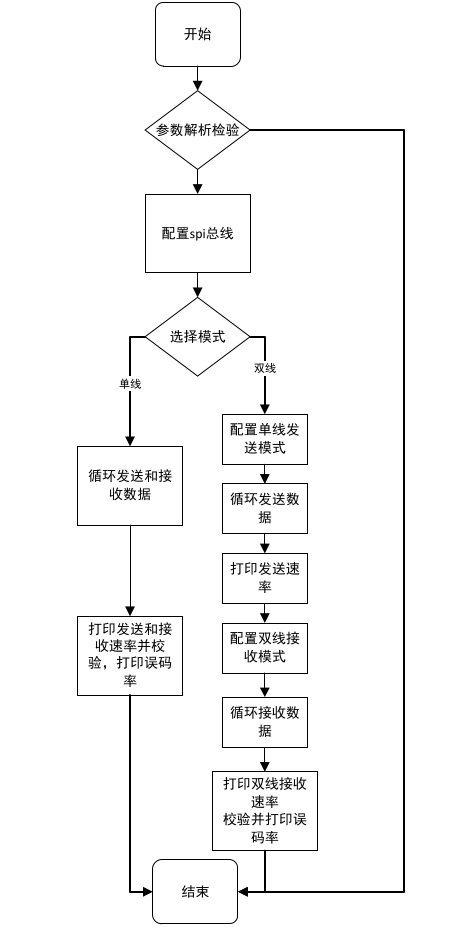

1 spi_rw案例

1.1 案例说明

案例功能:主要演示T3/A40i(ARM Cortex-A7)与PGL25G/Spartan-6(FPGA)处理器之间的SPI通信。

ARM端实现SPI Master功能

a.打开SPI设备节点,如:/dev/spidev0.0。

b.使用ioctl配置SPI总线,如SPI总线极性和相位、通信速率、数据字长度等。

c.选择模式为单线模式或双线模式。当SPI总线为双线模式时,发送数据是单线模式,接收数据是双线模式。

d.发送数据至SPI总线,并从SPI总线读取数据。(备注:如单次传输数据大于64Byte,驱动程序将会自动启用DMA传输功能。)

e.打印发送和接收速率。

f.校验读写数据,然后打印误码率。

FPGA端实现SPI Slave功能

a.FPGA将SPI Master发送的2KByte数据保存至BRAM。

b.SPI Master发起读数据时,FPGA从BRAM读取2KByte通过SPI总线传输给SPI Master。

c.当SPI总线为双线模式,接收数据支持双线模式,而发送数据不支持双线模式。

图 4 ARM端程序流程图

测试结果

(1) SPI单线模式

根据官方数据手册,SPI总线通信时钟频率理论值最大为100MHz。本次测试指定SPI总线通信时钟频率为最大值100MHz,则SPI单线模式理论速率为:(100000000/1024/1024/8)MB/s ≈ 11.92MB/s。实测SPI单线模式写速率为:10.924MB/s,SPI单线模式读速率为:10.924MB/s。

(2) SPI双线模式

根据官方数据手册,SPI总线通信时钟频率理论值最大为100MHz。本次测试指定SPI总线通信时钟频率为最大值100MHz,则SPI单线模式理论速率为:(100000000/1024/1024/8)MB/s ≈ 11.92MB/s;则SPI双线模式理论速率为:(100000000/1024/1024/4)MB/s ≈ 23.84MB/s。本次实测SPI单线模式写速率为11.631MB/s,SPI双线模式读速率为17.807MB/s。

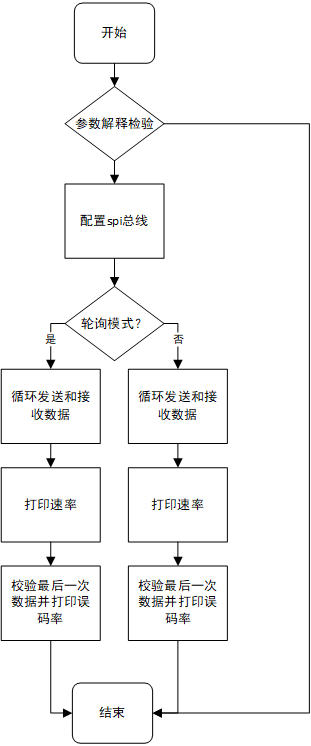

2 rt_spi_rw案例

2.1 案例说明

案例功能:基于Linux-RT系统,演示T3/A40i(ARM Cortex-A7)与PGL25G/Spartan-6(FPGA)处理器之间的SPI通信(单线模式)。

ARM端实现SPI Master功能

a.打开SPI设备节点。如:/dev/spidev0.0。

b.使用ioctl配置SPI总线。如SPI总线极性和相位、通信速率、数据字长度等。

c.创建实时线程。

d.发送数据至SPI总线,以及从SPI总线读取数据。

e.打印发送、接收的速率和传输耗时。

f.校验读写数据,然后打印误码率。

FPGA端实现SPI Slave功能

a.FPGA将SPI Master发送的2KByte数据保存至BRAM。

b.SPI Master发起读数据时,FPGA从BRAM读取2KByte通过SPI总线传输给SPI Master。

图 5 ARM端程序流程图

测试结果

(1) 非轮询方式

根据官方数据手册可知,SPI总线通信时钟频率理论值最大为100MHz。本次测试指定SPI总线通信时钟频率为最大值100MHz,则理论速率为:(100000000/1024/1024/8)MB/s ≈ 11.92MB/s。实测传输4Byte数据的最小耗时为49us,最大耗时为662us,平均耗时为227us;写速率为0.017MB/s,读速率为0.017MB/s。

(2) 轮询方式

根据官方数据手册可知,SPI总线通信时钟频率理论值最大为100MHz。本次测试指定SPI总线通信时钟频率为最大值100MHz,则理论速率为:(100000000/1024/1024/8)MB/s ≈ 11.92MB/s。实测传输4Byte数据的最小耗时为14us,最大耗时为59us,平均耗时为14us;写速率为0.239MB/s,读速率为0.239MB/s。

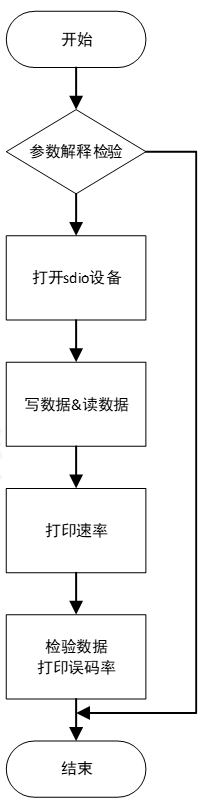

3 sdio_test案例

3.1 案例说明

案例功能:演示T3/A40i(ARM Cortex-A7)与PGL25G/Spartan-6(FPGA)处理器之间的SDIO通信。

ARM端实现SDIO Master功能

a.打开SDIO设备节点,如:/dev/generic_sdio0。

b.发送数据至SDIO总线,以及从SDIO总线读取数据。

c.打印发送和接收速率。

d.校验读写数据,然后打印误码率。

FPGA端实现SDIO Slave功能

a.FPGA将SDIO Master发送的2KByte数据保存至BRAM。

b.SDIO Master发起读数据时,FPGA从BRAM读取2KByte通过SDIO总线传输给SDIO Master。

图 6 ARM端程序流程图

测试结果

本次测试指定SDIO总线通信时钟频率为25MHz(最高50MHz),则理论通信速率为:(25 x 4 / 8)MB/s = 12.5MB/s。实测写速率为5.113MB/s,读速率为5.440MB/s,误码率为0.0%。

4 csi_test案例

4.1 案例说明

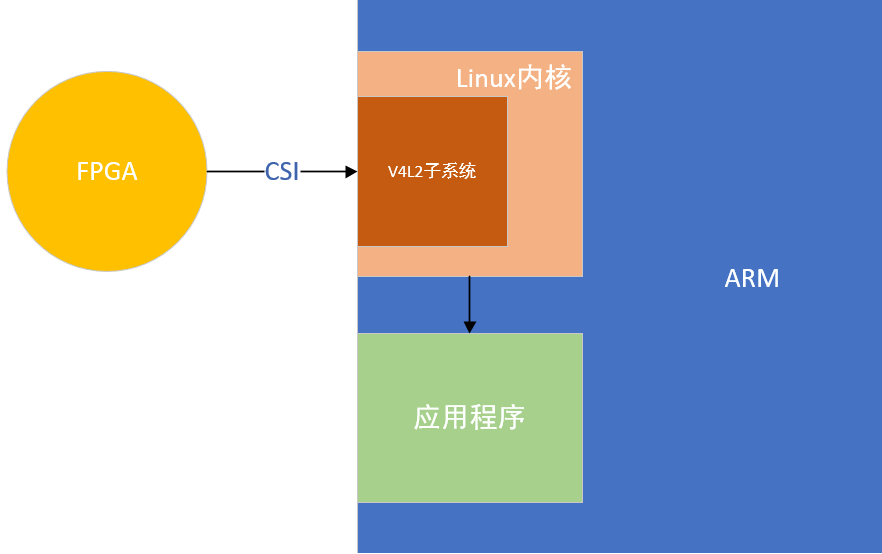

案例功能:演示T3/A40i(ARM Cortex-A7)与PGL25G/Spartan-6(FPGA)处理器之间的CSI通信案例。

ARM端功能

a)基于Linux子系统V4L2。

b)通过CSI总线,采集指定帧数数据。

c)计算总耗时。

d)打印平均采集速率,并校验最后一帧图像的数据。

FPGA端功能

a)将测试数据(0x00 ~ 0xFF)写入FIFO。

b)从FIFO读出数据,按行与帧的方式、1024 x 512的分辨率,通过CSI总线发送至ARM端。

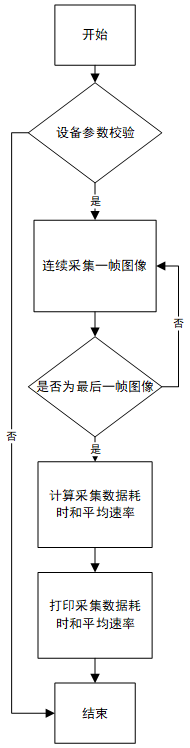

使用的CSI总线为CSI0,最高支持分辨率为1080P30,数据位宽为8bit。功能框图与程序流程图,如下图所示。

图 7 功能框图

图 8 ARM端程序流程图

测试结果

FPGA端将CSI_PCLK设置为65MHz,测试数据写入FIFO的时钟FIFO_WR_CLK设置为59MHz。由于FPGA端需将数据写入FIFO再从FIFO读出后发送,每一行与每一帧之间的间隔时间会受FIFO写入的速率影响,因此CSI通信的实际理论传输带宽应为:(59MHz x 8bit / 8)MB/s = 59MB/s。实测传输速率为55.1MB/s,误码率为0.0%。

查看更多详细案例说明/测试方法、案例源码,

请长按或微信扫描二维码下载

关于Tronlong

创龙科技(Tronlong)始创于2013年,是国内领先的嵌入式产品平台提供商,业务主要涵盖工业核心板、工业评估板、项目服务,总部位于广州科学城,下设独立运营的教仪事业部,并在北京、上海、深圳、西安等地设有业务及技术服务中心。

创龙科技专注于ARM、FPGA、DSP多核异构技术开发,是TI、Xilinx、NXP、紫光同创中国官方合作伙伴,产品线覆盖TI、Xilinx、NXP、全志、瑞芯微、紫光同创等厂商处理器平台,产品广泛应用于工业自动化、仪器仪表、能源电力、通信、医疗、安防等行业。

创龙科技始终致力于打造高品质工业核心板,以“提供高可靠性产品”、“快速响应需求”、“有效解决问题”为三大服务宗旨,已成功帮助超过12000家工业客户完成产品的快速开发与上市。

联系我们:

销售邮箱:sales@tronlong.com

技术邮箱:support@tronlong.com

创龙总机:020-8998-6280

技术热线:020-3893-9734

创龙官网:www.tronlong.com

技术论坛:www.51ele.net

官方商城:https://tronlong.tmall.com

在看点这里

1985

1985

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?