一、时钟有两种产生源

晶振:是用石英晶体经精密切割磨削并镀上电极焊上引线做成

PLL(锁相环)合成器:通用PLL合成器需要一个外部晶体并包含一个能够对晶体的特定频率加倍或分频的集成锁相环(PLL)电路

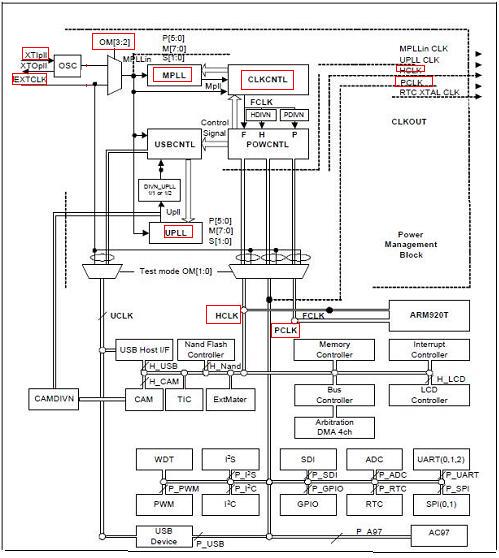

二、S3C2440时钟体系图

三、S3C2440时钟来源于两种,可以从图的左上角找到这两种来源

XTIPLL:外部晶振时钟

EXTCLK:外部时钟

具体ARM使用的是哪一种时钟,由寄存器OM[3:2]配置决定。

四、UPLL(锁相环)专用于USB

MPLL(锁相环)用于CPU及其它外围器件

通过MPLL会产生三个部分的时钟频率

(1)FCLK:用于CPU核

(2)HCLK:用于AHB (Advanced High-performance Bus:高速外设总线)的设备(比如SDRAM)

(3)PCLK:用于APB (Advanced Peripheral Bus:低速外设)总线的设备(比如UART)。

五:

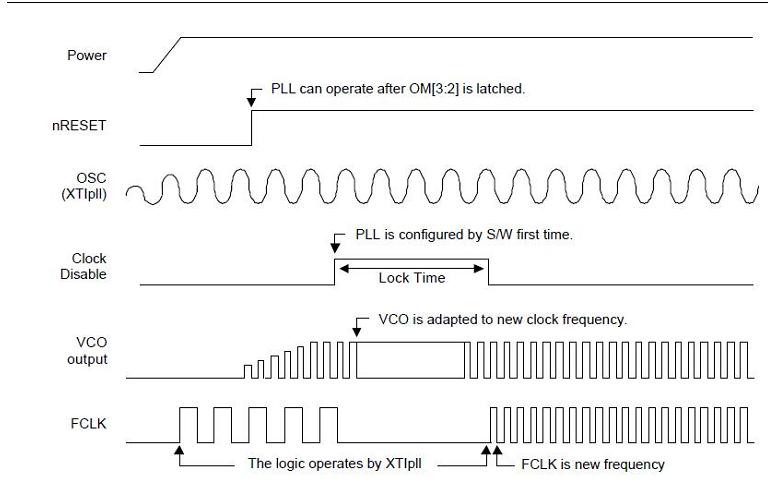

六、通过图得到以下信息

(1)电源power启动稳定后,CPU频率由FCLK控制(12MH),nRESET信号恢复高电平后,CPU开始执行指令。

(2)在设置MPLL的几个寄存器后,需要等待一段时间(Lock Time),MPLL的输出才稳定。在这段时间(Lock Time)内,FCLK停振,CPU停止工作。

Lock Time的长短由寄存器LOCKTIME设定。

(3). Lock Time之后,MPLL输出正常,CPU工作在新的FCLK(如400MHz)下

七、Lock Time的时间长度是由寄存器- LOCKTIME中配置的值配置的。LOCKTIME[31:16]用于UPLL,LOCKTIME[15:0]用于MPLL。使用确省值0xffffffff即可。、

八、寄存器- MPLLCON

该寄存器用于设置FCLK与Fin的倍数。

MPLLCON[19:12]的值称为MDIV

MPLLCON[9:4]的值称为PDIV

MPLLCON[1:0]的值称为SDIV

FCLK与Fin的计算关系式如下:

MPLL(FCLK)=(2*m*Fin)/(p*2^s)

其中:m=MDIV+8,p=PDIV+2,s=SDIV

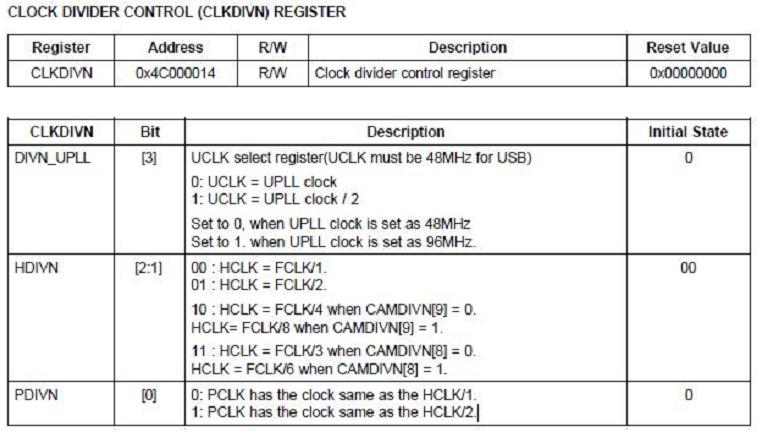

九、寄存器- CLKDIVN

该寄存器用于设置FCLK、HCLK、PCLK三者的比例

v HDIVN:位[2:1], 用来设置HCLK与FCLK比例关系

v PDIVN:位[0], 用来设置PCLK与HCLK比例关系

例如:

FCLK:HCLK:PCLK=4:1:2

FCLK=400M(主频)

HCLK=100M

PCLK=200M

1538

1538

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?