随着CPU的频率不断提升,而内存的访问速度却没有质的突破,为了弥补访问内存的速度慢,充分发挥CPU的计算资源,提高CPU整体吞吐量,在CPU与内存之间引入了一级Cache。随着热点数据体积越来越大,一级Cache L1已经不满足发展的要求,引入了二级Cache L2,三级Cache L3CPU Cache在存储器层次结构中的示意如下图:

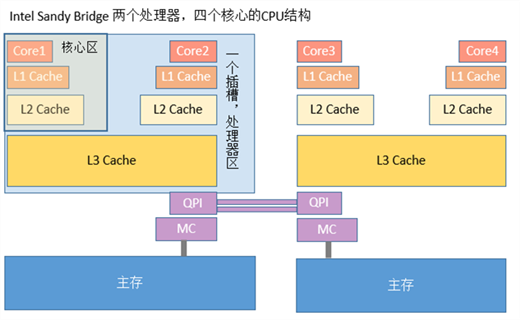

计算机早已进入多核时代,软件也越来越多的支持多核运行。一个处理器对应一个物理插槽,多处理器间通过QPI总线相连。一个处理器包含多个核,一个处理器间的多核共享L3 Cache。一个核包含寄存器、L1 Cache、L2 Cache,下图是Intel Sandy Bridge CPU架构,一个典型的NUMA多处理器结构:

多核之间为保持数据的一致性,提出了MESI协议。

单核Cache中每个Cache line有2个标志:dirty和valid标志,它们很好的描述了Cache和Memory(内存)之间的数据关系(数据是否有效,数据是否被修改),而在多核处理器中,多个核会共享一些数据,MESI协议就包含了描述共享的状态。

在MESI协议中,每个Cache line有4个状态,可用2个bit表示,它们分别是:

| 状态 | 描述 |

| M(Modified) | 这行数据有效,数据被修改了,和内存中的数据不一致,数据只存在于本Cache中。 |

| E(Exclusive) | 这行数据有效,数据和内存中的数据一致,数据只存在于本Cache中。 |

| S(Shared) | 这行数据有效,数据和内存中的数据一致,数据存在于很多Cache中。 |

| I(Invalid) | 这行数据无效。 |

MESI状态

M(Modified)和E(Exclusive)状态的Cache line,数据是独有的,不同点在于M状态的数据是dirty的(和内存的不一致),E状态的数据是clean的(和内存的一致)。

S(Shared)状态的Cache line,数据和其他Core的Cache共享。只有clean的数据才能被多个Cache共享。

I(Invalid)表示这个Cache line无效。

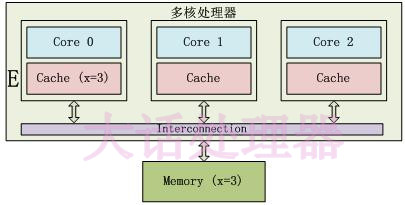

E状态示例如下:

E状态

只有Core 0访问变量x,它的Cache line状态为E(Exclusive)。

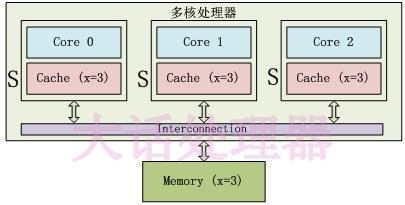

S状态示例如下:

S状态

3个Core都访问变量x,它们对应的Cache line为S(Shared)状态。

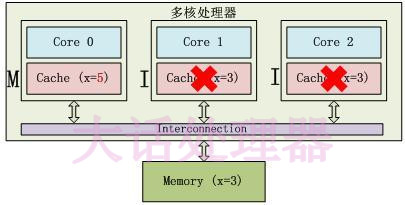

M状态和I状态示例如下:

M状态和I状态

Core 0修改了x的值之后,这个Cache line变成了M(Modified)状态,其他Core对应的Cache line变成了I(Invalid)状态。

相关性较好的文章:http://blog.csdn.net/zhang_shuai_2011/article/details/38119657

449

449

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?