视频链接:

https://v.youku.com/v_show/id_XNTkyNzQ2ODIwMA==.html?x&sharefrom=android&sharekey=fa1c2ad301a30a1d1edca6697bf67d285

第一,在Modelsim里面点击File的new里的project

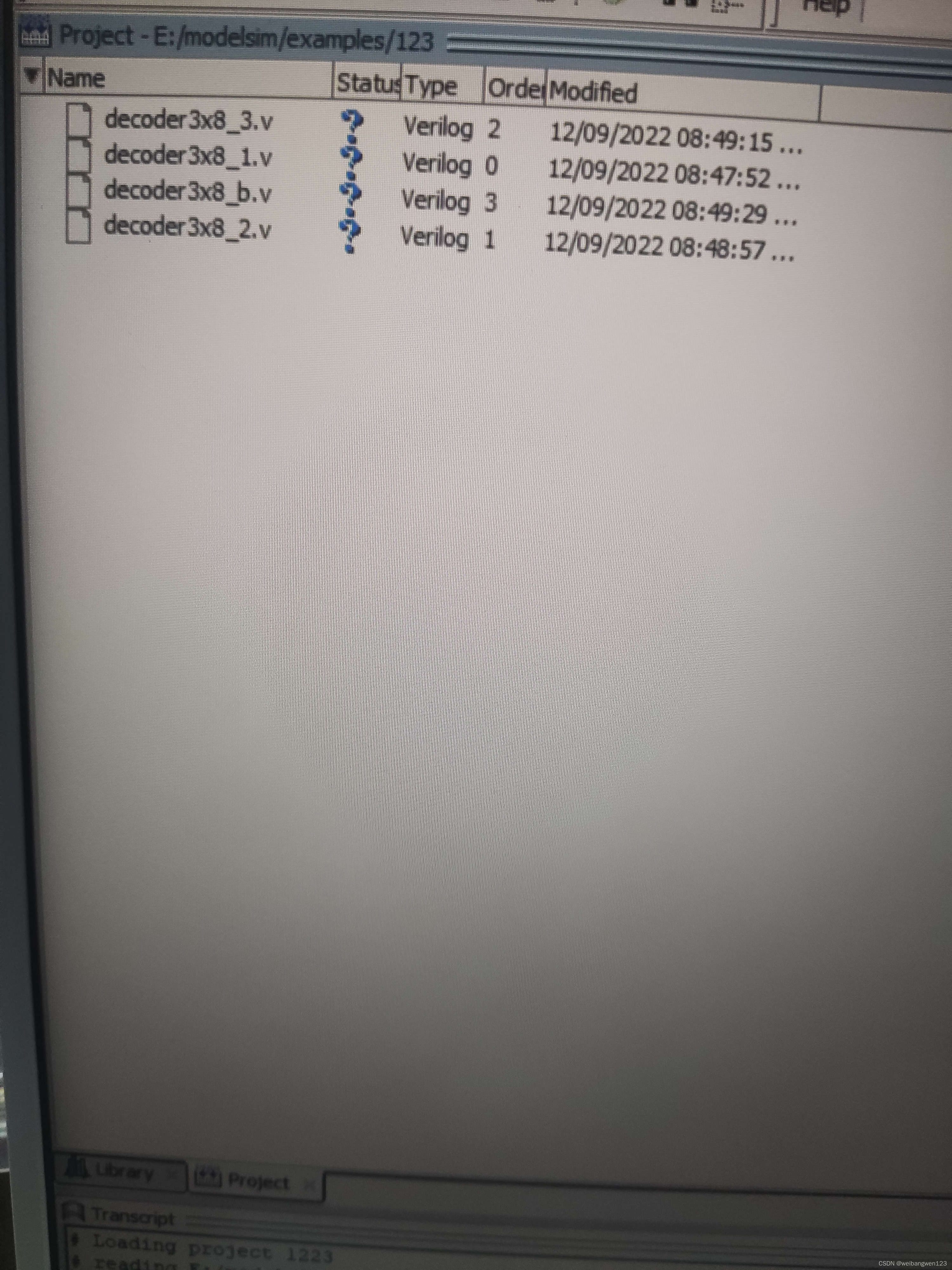

建立项目,先设置项目名称,在点击Creta New File,把Add file as type下的改成verilog点击OK,需要建立四个文件,命名不能重复。如这样

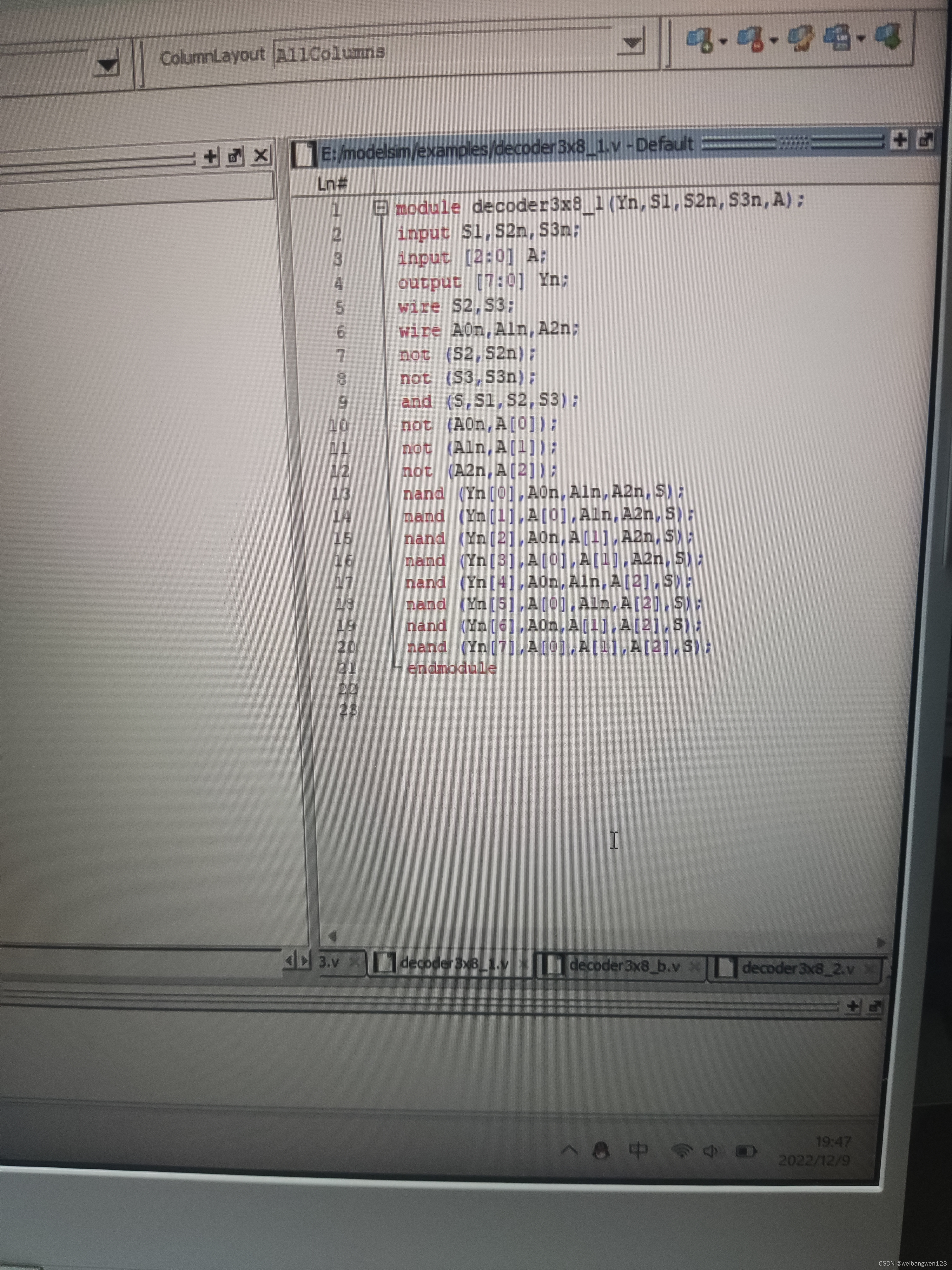

其中一个是激励模块,输入代码,注意每次输入完要保存一次ctrl加s。

这篇博客介绍了使用Modelsim进行Verilog HDL数字系统设计及仿真的步骤。首先在Modelsim创建项目并编写四个Verilog文件,然后编译并运行得到波形图。接着在Quartus软件中导入代码,通过特定工具生成更多图形。最后在Modelsim中调整激励模块的延时以获得不同波形。实验过程虽有挑战,但整体可操作。

这篇博客介绍了使用Modelsim进行Verilog HDL数字系统设计及仿真的步骤。首先在Modelsim创建项目并编写四个Verilog文件,然后编译并运行得到波形图。接着在Quartus软件中导入代码,通过特定工具生成更多图形。最后在Modelsim中调整激励模块的延时以获得不同波形。实验过程虽有挑战,但整体可操作。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?