请 尊重做者,勿 转载,谢谢 ~

简介

编者使用 Quartus II 9.0 进行编程,使用 VHDL语言 ,主要实验有两个,分别是基于芯片 MAX7000S: EPM7128SLC84-15的硬布线和流水硬连线。web

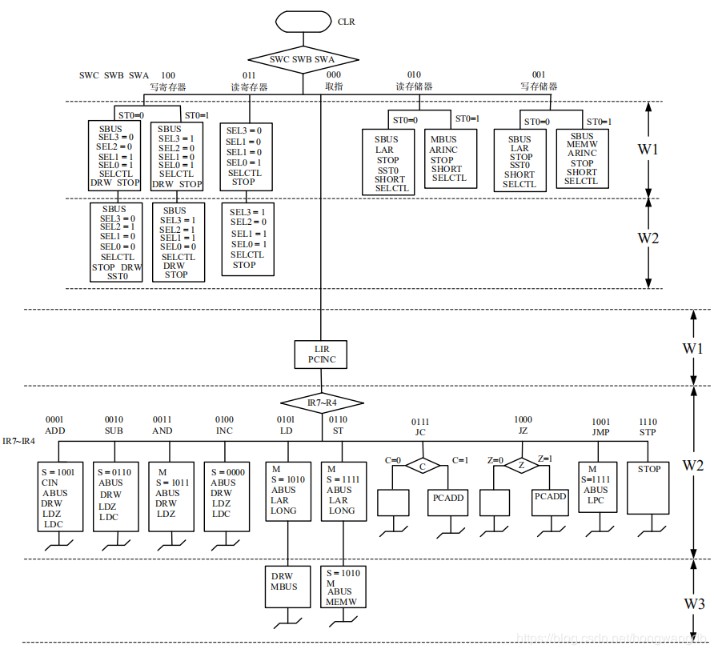

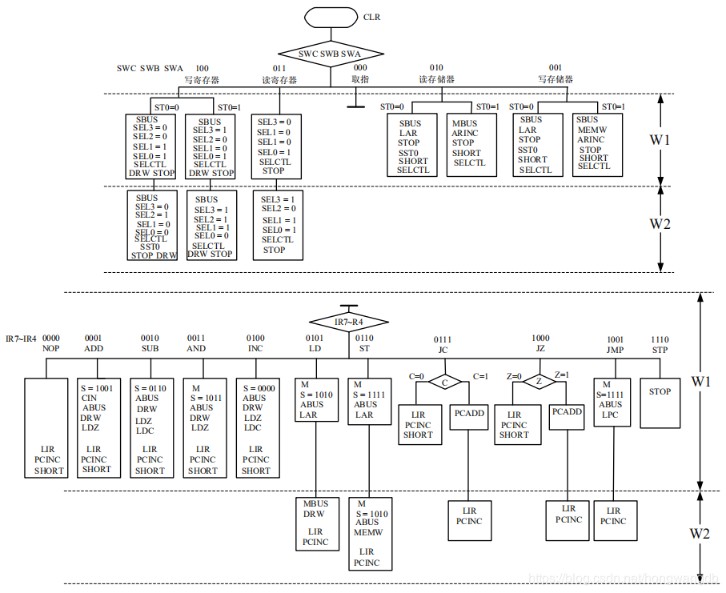

流程图

硬连线 :

流水硬连线 :

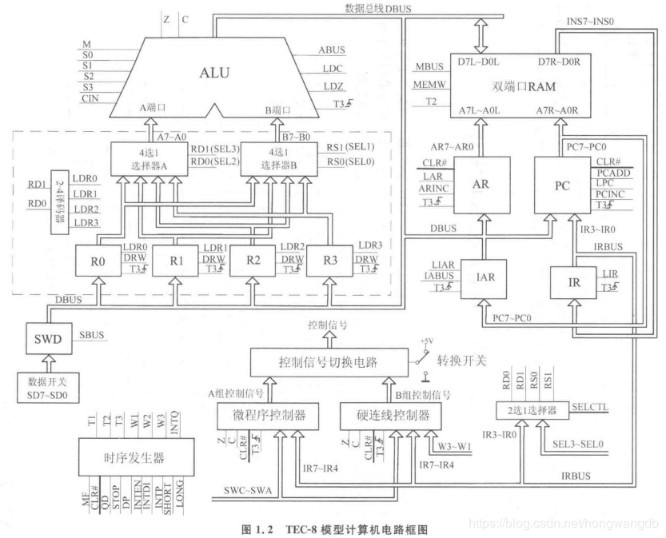

模型机流程图 :

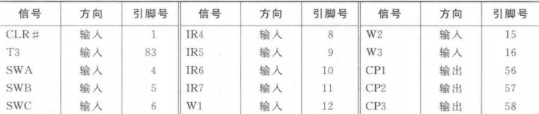

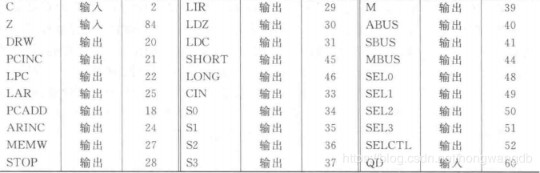

引脚配置

如图:

编程

编程

添加的功能

在原指令基础上要求扩指至少三条: 硬布线添加三条,流水添加四条svg

修改PC指针功能(任意指针)测试

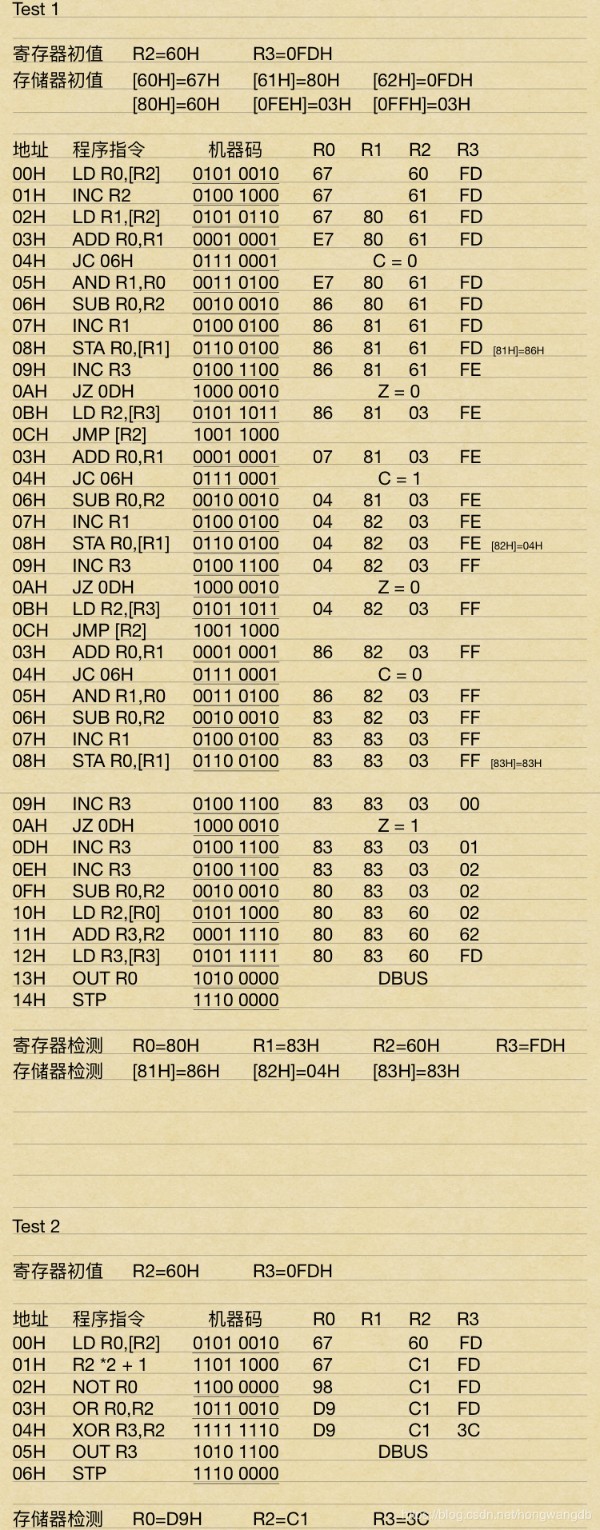

测试程序及检测结果

直接检测流水,相关如图:

.net

.net

代码(VHDL语言)

1.硬布线设计

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY Duang IS

PORT (

SWB : IN STD_LOGIC;

SWA : IN STD_LOGIC;

SWC : IN STD_LOGIC;

clr : IN STD_LOGIC;

C : IN STD_LOGIC;

Z : IN STD_LOGIC;

IRH : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

T3 : IN STD_LOGIC;

W1 : IN STD_LOGIC;

W2 : IN STD_LOGIC;

W3 : IN STD_LOGIC;

SELCTL : OUT STD_LOGIC;

ABUS : OUT STD_LOGIC;

M : OUT STD_LOGIC;

S : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

SEL1 : OUT STD_LOGIC;

SEL0 : OUT STD_LOGIC;

SEL2 : OUT STD_LOGIC;

SEL3 : OUT STD_LOGIC;

DRW : OUT STD_LOGIC;

SBUS : OUT STD_LOGIC;

LIR : OUT STD_LOGIC;

MBUS : OUT STD_LOGIC;

MEMW : OUT STD_LOGIC;

LAR : OUT STD_LOGIC;

ARINC : OUT STD_LOGIC;

LPC : OUT STD_LOGIC;

PCINC : OUT STD_LOGIC;

PCADD : OUT STD_LOGIC;

CIN : OUT STD_LOGIC;

LONG : OUT STD_LOGIC;

SHORT : OUT STD_LOGIC;

QD : IN STD_LOGIC;

STOP : OUT STD_LOGIC;

LDC : OUT STD_LOGIC;

LDZ : OUT STD_LOGIC

);

END Duang;

ARCHITECTURE art OF Duang IS

SIGNAL SWCBA : STD_LOGIC_VECTOR(2 DOWNTO 0);

SIGNAL ST0 : STD_LOGIC;

SIGNAL ST0_reg : STD_LOGIC;

SIGNAL SST0 : STD_LOGIC;

SIGNAL STOP_reg_reg : STD_LOGIC;

SIGNAL STOP_reg : STD_LOGIC;

BEGIN

STOP <= (STOP_reg_reg OR STOP_reg) WHEN (SWCBA /= "000") ELSE '0';

SWCBA(2 DOWNTO 0) <= (SWC & SWB & SWA);

ST0 <= ST0_reg;

PROCESS (clr, T3)

BEGIN

IF (clr = '0') THEN

ST0_reg <= '0';

STOP_reg_reg <= '1';

ELSIF (T3'EVENT AND T3 = '0') THEN

IF (SST0 = '1') THEN

ST0_reg <= '1';

END IF;

END IF;

END PROCESS;

PROCESS (SWCBA, IRH, W1, W2, W3, ST0, C, Z)

BEGIN

SHORT <= '0';

LONG <= '0';

CIN <= '0';

SELCTL <= '0';

ABUS <= '0';

SBUS <= '0';

MBUS <= '0';

M <= '0';

S <= "0000";

SEL3 <= '0';

SEL2 <= '0';

SEL1 <= '0';

SEL0 <= '0';

DRW <= '0';

SBUS <= '0';

LIR <= '0';

MEMW <= '0';

LAR <= '0';

ARINC <= '0';

LPC <= '0';

LDZ <= '0';

LDC <= '0';

STOP_reg <= '1';

PCINC <= '0';

SST0 <= '0';

PCADD <= '0';

CASE SWCBA IS

WHEN "000" =>

IF (ST0 = '0') THEN

LPC <= W1;

SBUS <= W1;

SST0 <= W1;

SHORT <= W1;

STOP_reg <= '0';

ELSIF (ST0 = '1') THEN

CASE IRH IS

WHEN "0001" =>--ADD

LIR <= W1;

PCINC <= W1;

S <= "1001";

CIN <= W2;

ABUS <= W2;

DRW <= W2;

LDC <= W2;

LDZ <= W2;

WHEN "0010" =>--SUB

LIR <= W1;

PCINC <= W1;

S <= "0110";

ABUS <= W2;

DRW <= W2;

LDZ <= W2;

LDC <= W2;

WHEN "0011" =>--AND

LIR <= W1;

PCINC <= W1;

S <= "1011";

M <= W2;

ABUS <= W2;

DRW <= W2;

LDZ <= W2;

WHEN "0100" =>--INC

LIR <= W1;

PCINC <= W1;

S <= "0000";

ABUS <= W2;

DRW <= W2;

LDZ <= W2;

LDC <= W2;

WHEN "0101" =>--LD

LIR <= W1;

PCINC <= W1;

S <= "1010";

M <= W2;

ABUS <= W2;

LAR <= W2;

LONG <= W2;

MBUS <= W3;

DRW <= W3;

WHEN "0110" =>--ST

LIR <= W1;

PCINC <= W1;

M <= W2 OR W3;

S(3) <= '1';

S(2) <= W2;

S(1) <= '1';

S(0) <= W2;

ABUS <= W2 OR W3;

LAR <= W2;

LONG <= W2;

MEMW <= W3;

WHEN "0111" =>--JC

LIR <= W1;

PCINC <= W1;

PCADD <= C AND W2;

WHEN "1000" =>--JZ

LIR <= W1;

PCINC <= W1;

PCADD <= Z AND W2;

WHEN "1001" =>--JMP

LIR <= W1;

PCINC <= W1;

M <= W2;

S <= "1111";

ABUS <= W2;

LPC <= W2;

WHEN "1010" =>--OUT

M <= W2;

S <= "1010";

ABUS <= W2;

WHEN "1011" =>--OR

LIR <= W1;

PCINC <= W1;

M <= W2;

S <= "1110";

ABUS <= W2;

DRW <= W2;

LDZ <= W2;

WHEN "1100" =>--NOT

LIR <= W1;

PCINC <= W1;

M <= W2;

S <= "0000";

ABUS <= W2;

DRW <= W2;

LDZ <= W2;

WHEN "1101" =>--A*2+1

LIR <= W1;

PCINC <= W1;

S <= "1100";

ABUS <= W2;

DRW <= W2;

LDZ <= W2;

LDC <= W2;

WHEN "1110" =>--STP

LIR <= W1;

PCINC <= W1;

STOP_reg <= W2;

WHEN OTHERS =>

LIR <= W1;

PCINC <= W1;

END CASE;

END IF;

WHEN "001" =>

SELCTL <= W1;

SHORT <= W1;

SBUS <= W1;

STOP_reg <= W1;

SST0 <= W1;

LAR <= W1 AND (NOT(ST0));

ARINC <= W1 AND ST0;

MEMW <= W1 AND ST0;

WHEN "010" =>

SELCTL <= W1;

SHORT <= W1;

SBUS <= W1 AND (NOT(ST0));

MBUS <= W1 AND ST0;

STOP_reg <= W1;

SST0 <= W1;

LAR <= W1 AND (NOT(ST0));

ARINC <= W1 AND ST0;

WHEN "011" =>

SELCTL <= '1';

STOP_reg <= W1 OR W2;

SEL3 <= W2;

SEL2 <= '0';

SEL1 <= W2;

SEL0 <= W1 OR W2;

WHEN "100" =>

SELCTL <= '1';

SST0 <= W2;

SBUS <= W1 OR W2;

STOP_reg <= W1 OR W2;

DRW <= W1 OR W2;

SEL3 <= (ST0 AND W1) OR (ST0 AND W2);

SEL2 <= W2;

SEL1 <= ((NOT(ST0)) AND W1) OR (ST0 AND W2);

SEL0 <= W1;

WHEN OTHERS =>

END CASE;

END PROCESS;

END art;

2.流水3d

相信聪明如你,应该能写出流水了吧,小编实在太困了,就不放代码啦(否则要慢慢排版呢

\n //手动换行嘿嘿

若是真的须要流水的代码的话就下载叭,我已经上传过了,文件名称为Duangg.vhd,连接为:https://download.csdn.net/download/hongwangdb/11225811

还有什么问题能够私小编嗷指针

1551

1551

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?