以下摘录《步骤吓得核心——软-core处理器的室内设计与分析》一本书

1 IMMU结构

OR1200中实现IMMU的文件有or1200_immu_top.v、or1200_immu_tlb.v、or1200_spram.v,当中使用or1200_immu_top.v实现了IMMU模块,使用or1200_immu_tlb.v实现了ITLB模块,or1200_spram.v是一个单口RAM。使用事实上现了ITLB的表项。如图10.5所看到的。

本小节将分别介绍IMMU模块与其余模块的连接关系、ITLB结构。

1.1 IMMU模块与其余模块的连接关系

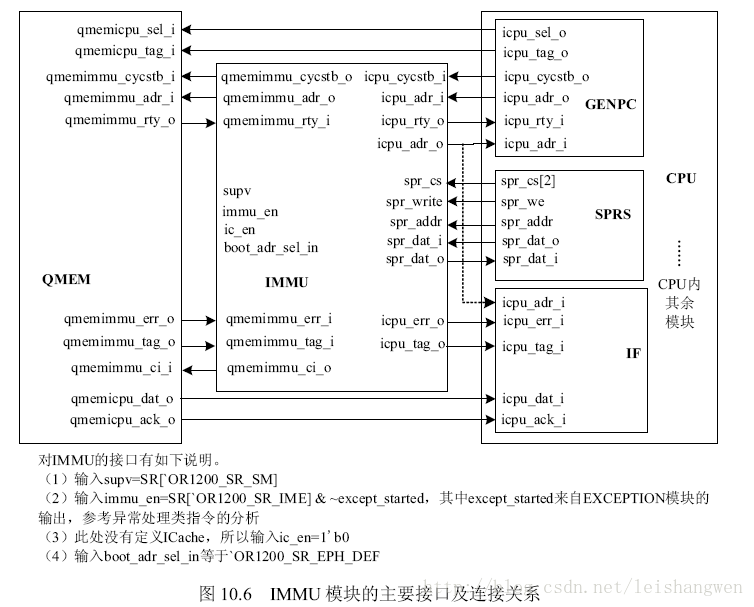

图10.6给出了IMMU与其它模块的连接关系。当中的大部分接口都非常直观。

IMMU与CPU之间的接口是指令Wishbone总线的一部分。IMMU与QMEM之间也是Wishbone总线的一部分,当没有配置IMMU时能够觉得CPU与QMEM是直接相连的,这一点在第3章中已有说明。此外,IMMU还有与特殊寄存器訪问有关的接口:spr_cs、spr_write、spr_addr、spr_dat_i、spr_dat_o,这说明在IMMU中存在特殊寄存器,而且该特殊寄存器可读(有spr_dat_o接口)、可写(有spr_dat_i接口)。

1.2 ITLB结构

前文已述。OR1200中MMU的功能主要就体如今TLB的实现上,对IMMU而言就是ITLB。所以首先给出ITLB的结构,图10.4是一个通用的TLB变换原理图。每一个处理器实现TLB的功能都会有详细的实现方式,此处讨论的是OR1200中的实现方式。

OR1200中ITLB将图10.4中的项分两部分存放,标识存放在MR_RAM表中。数据存放在TR_RAM表中,如图10.7所看到的。从名称上也能够知道这里的表实际是採用RAM实现的,表的索引相应RAM地址,表项相应RAM内容。

还是以默认配置中TLB有64项为例,同一时候依照OR1200中的习惯将虚拟地址称为有效地址。MR_RAM表每一项占14bit,当中高13bit是有效地址的19-31位,最低bit为V,代表该表项是否有效。TR_RAM表每一项占22bit,当中高19bit是物理地址的13-31位,低位的3bit各自是UXE(User Execute Enable)、SXE(Supervisor Execute Enable)、CI(Cache Inhibit)。分别代表用户模式是否可运行、特权模式是否可运行、是否禁止缓存。IMMU使用UXE、SXE实现对存储器中指令页的保护。CI的作用是指示处理器要不要将该页放置在缓存中,假设CI为1。则该页代码不会出如今缓存中。每次訪问都须要从存储器中读取。反之表示该页代码能够被缓存。

ITLB的翻译过程是:利用有效地址中的13-18bit作为索引同一时候查询MR_RAM、TR_RAM两个表。利用MR_RAM表中得到的结果推断ITLB是否命中,ITLB命中的条件是MR_RAM表项中的“有效地址的19-31位”与CPU提供的有效地址中的19-31位相等,而且V为1,反之ITLB未命中。也称为ITLB失靶。当ITLB命中的时候,将从TR_RAM表索引得到的表项中的“物理地址的13-31位”与CPU提供的有效地址低13位结合作为物理地址。

同一时候得到该页的属性SXE、UXE、CI。

IMMU利用ITLB的翻译结果进行下一步操作,分三种情况:

- ITLB命中。但SXE为0。而当前处理器处于特权模式。或者UXE为0。而当前处理器处于用户模式,均会违反页保护策略,引发指令页失效异常,处理器转移到指令页失效异常的处理例程,參考表1.3可知相应地址是0x400

- ITLB命中。而且没有违反页保护策略,那么会取得相应物理地址处的指令

- ITLB失靶。因为OR1200没有实现硬件的ITLB载入,所以仅仅能通过软件实现ITLB载入,ITLB失靶引发ITLB失靶异常,处理器转移到ITLB失靶异常的处理例程。參考表1.3可知相应地址是0xA00,用户需编写失靶异常的处理例程,在当中将须要的页表项载入入ITLB

版权声明:本文博客原创文章,博客,未经同意,不得转载。

5476

5476

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?