用FPGA对ASIC进行原型验证的过程

reference:http://xilinx.eetrend.com/d6-xilinx/article/2018-10/13736.html

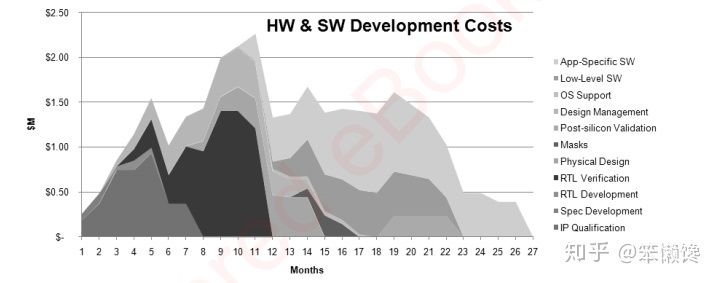

鉴于芯片设计的复杂度提升, 成功设计一个芯片所牵扯的步骤与过程也愈加复杂,所需花费的资金也成倍增加,一个典型的芯片开发项目的周期和花销如下所示

可以见到在芯片制造出来之前,很多精力会花费在RTL代码验证工作上,另外软件的相关开发工作,也会在得到芯片前开始,这2方面都需要借助FPGA原形来模拟芯片的行为,帮助硬件开发和软件开发者,共同提升工作效率。

FPGA原型在数字芯片设计中,基本是必不可少的,原因非常明显,相比用仿真器,或者加速器等来跑仿真,FPGA的运行速度,更接近真实芯片,可以配合软件开发者来进行底层软件的开发。当然FPGA原型作为芯片的替身,也是有诸多限制的,比如规模限制,速度限制,功耗限制,结构限制等,在使用FPGA原型作为芯片的替代时,需要进行相应的修改,才能完成相应功能,甚至有些功能最终无法覆盖。

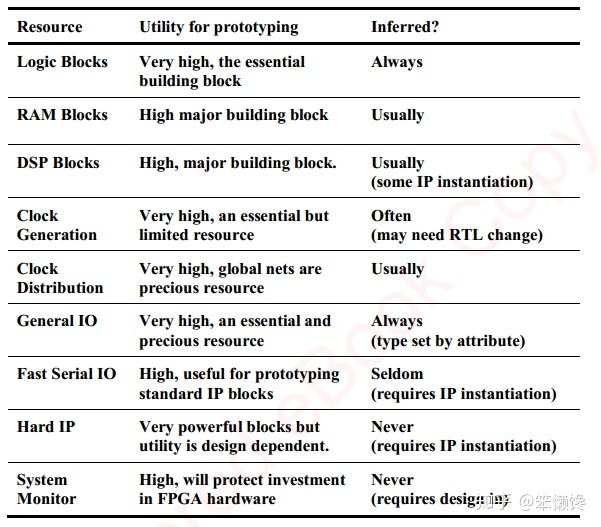

如果对FPGA中可以映射为ASIC的资源做逐一对比,我们可以得到这样的表格。

以上表格看出,除了普通的RTL逻辑以及基本端口,其他的类似存储时钟DSP等,最好都是做手动修改进行映射,把ASIC设计转换为FPGA比较靠谱。

要把一块ASIC做出FPGA的原型,需要大致一下步骤,

1 FPGA选型

2 做板或者购买原型板。

3 将ASIC设计转换装入FPGA

4 调试启动FPGA原型

5

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4833

4833

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?