1.先进入admin

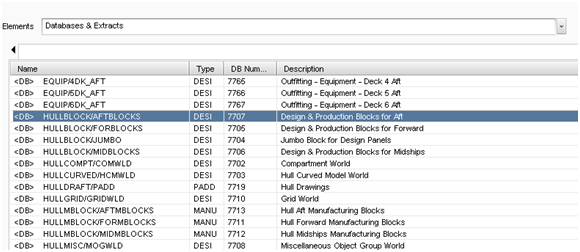

2.选数据库名:

比如这个HULLBLOCK/AFTBLOCKS

3.

选好数据库后在命令栏依次输入以下命令,输入每一行后回车一下:

FROM DB HULLBLOCK/AFTBLOCKS

TO FILE /REC1 /REC2

RCFCOPY ALL

RECON

------等待执行完毕

BACKTRACK HULLBLOCK/AFTBLOCKS SESS 2

------等待执行完毕

FROM FILE /REC1 /REC2

TO DB HULLBLOCK/AFTBLOCKS

RECONF SAMEREF

等待执行完就可以了,每选择一个数据库就需要执行一遍第三步

596

596

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?