来源:http://home.eeworld.com.cn/my/space-uid-639749-blogid-267593.html

一般的,在Verilog中最常用的编码方式有二进制编码(Binary)、格雷码(Gray-code)编码、独热码(One-hot)编码。

二进制码和格雷码是压缩状态编码。 若使用格雷编码,则相邻状态转换时只有一个状态位发生翻转,这样不仅能消除状态转换时由多条状态信号线的传输延迟所造成的毛刺,又可以降低功耗。

二进制编码也可称连续编码,也就是码元值的大小是连续变化的。如S0=3'd0,S1=3'd1,S2=3'd2,S3=3'd3....

格雷码的相邻码元值间只有一位是不同的,如S0=3'b000,S1=3'b001,S2=3'b011,S3=3'b010....

独热编码即 One-Hot 编码,又称一位有效编码,其方法是使用N位状态寄存器来对N个状态进行编码,每个状态都由他独立的寄存器位,并且在任意时候,其中只有一位有效。虽然使用较多的触发器,但由于状态译码简单,可减少组合逻辑且速度较快, 这种编码方式还易于修改,增加状态或改变状态转换条件都可以在不影响状态机的其它部分的情况下很方便地实现。另外,它的速度独立于状态数量。与之相比,压缩状态编码在状态增加时速度会明显下降。

独热码值每个码元值只有一位是'1',其他位都是'0',如S0=3'b001,S1=3'b010,S2=3'b100

问题:USB升级FPGA程序完成后,给板子通电,发现启动FLASH中程序非常的慢,等了超长时间LED灯才有反应。

用Xilinx下载线直接将MCS的FPGA程序固化到FLASH也出现同样的问题。

解决方法是在Vivado工具中设置配置FLASH时钟,默认是3MHZ,可改成50MHZ。

方法是先open implemented design,待打开实现设计窗口后,再Tools下拉菜单选择Edit Device Properties,该选项下Configuration中Configuration Rate(MHz).

Cypress赛普拉斯 Spansion Micron公司关系 存储器市场

来源:http://bbs.eetop.cn/viewthread.php?tid=386148

关于altera fpga 时钟切换(clk mux) 的讨论

首先我用fpga是 altera cyclone II: 里面有个时钟mux: 一个时钟来自 pll , 一个时钟来自tck (jtag)

// 需要不同时钟的debug_ram。

debug_ram

debug_ram_inst (.address (clk_sw ? jtag_addr : rom_addr),

.clken (jtag_wr|~rom_rd_n ),

.clock (debug_ram_clk ),

.data (jtag_data ),

.wren (jtag_wr ),

.q (rom_data )

);

(1)如果直接用rtl作逻辑选择:assign debug_ram_clk = clk_sw ? tck : clk; //使用此逻辑综合要报rom_addr hold violation 时序warning(估计是因为做时钟切换clk时钟延时太长,看时序报告rom_addr hold需要2点几纳钞)

(2) 如果使用quartus ii 里的 ip, altclkctrl :clk_ctrl

u_clk_ctrl(.clkselect( clk_sw ),

.inclk0x ( clk ),

.inclk1x ( tck ),

.outclk ( debug_ram_clk)

);

会报如此错:Error: inclk[0] port of Clock Control Block "clk_ctrl:u_clk_ctrl|clk_ctrl_altclkctrl_8af:clk_ctrl_altclkctrl_8af_component|clkctrl1" is driven by PLL LL_inst|altpll:altpll_component|_clk0, but must be driven by a clock pin

Error: inclk[1] port of Clock Control Block "clk_ctrl:u_clk_ctrl|clk_ctrl_altclkctrl_8af:clk_ctrl_altclkctrl_8af_component|clkctrl1" is driven by altera_internal_jtag~TCKUTAP, but must be driven by a clock pin

//不知道为什么会报错,还在查资料中,也请大神赐教。。。。

(3)使用时钟mux代码如下:

module clk_mux#(parameter num_clk = 2 )

(input [num_clk-1:0] clk ,

//input [num_clk-1:0] clk_rst,

input [num_clk-1:0] clk_sel,

output clk_o

);

genvar i;

reg [num_clk-1:0] ena_r0;

reg [num_clk-1:0] ena_r1;

reg [num_clk-1:0] ena_r2;

wire [num_clk-1:0] qualified_sel;

// A look-up-table (LUT) can glitch when multiple inputs

// change simultaneously. Use the keep attribute to

// insert a hard logic cell buffer and prevent

// the unrelated clocks from appearing on the same LUT.

wire [num_clk-1:0] gated_clks /* synthesis keep */;

wire [num_clk-1:0] tmp_mask[0:num_clk-1];

generate

for (i=0; i<num_clk; i=i+1)

begin : lp0

assign tmp_mask = {num_clk{1'b1}} ^ (1 << i);

assign qualified_sel = clk_sel & (~|(ena_r2 & tmp_mask));

always @(posedge clk) begin

ena_r0 <= qualified_sel;

ena_r1 <= ena_r0;

end

always @(negedge clk) begin

ena_r2 <= ena_r1;

end

assign gated_clks = clk & ena_r2;

end

endgenerate

// These will not exhibit simultaneous toggle by construction

assign clk_o = |gated_clks;

endmodule

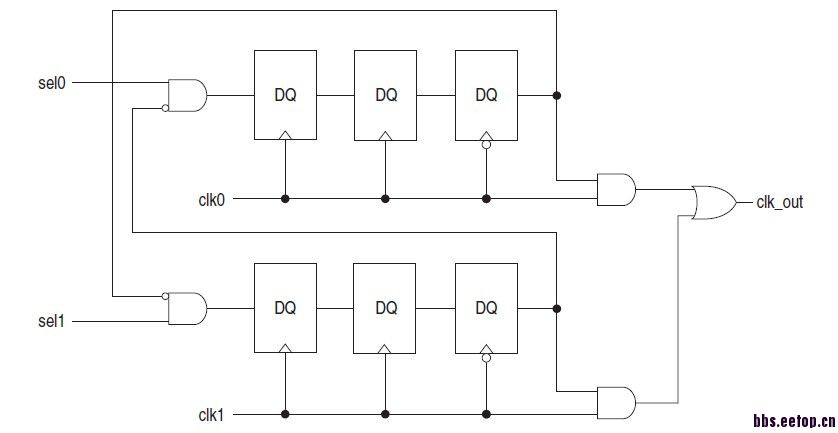

电路如下:

再实例化:clk_mux u_clk_mux({tclk,clk},{clk_sw,~clk_sw},debug_ram_clk); // 则这样就不会报错

(4)还有一种方法是动态配置pll(有些altera fpga支持),可是有一个时钟不是来自pll,故不能使用此方法了

前三种方法,暂时只有(3)不报错

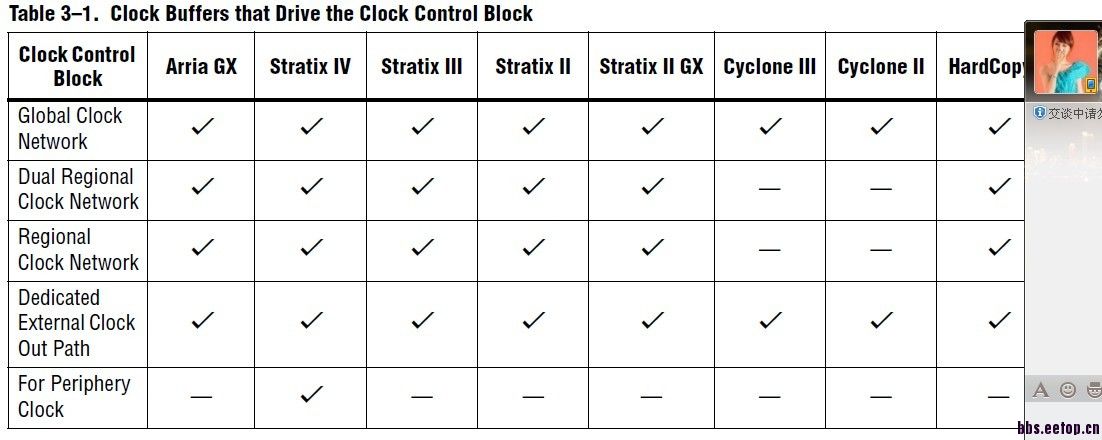

Clock Control Block (ALTCLKCTRL) Megafunction资料上有如此表格:

下有如此一段话:The global clock network allows a clock signal (or other global signals) to reach all parts of the chip with a similar amount of skew. The regional clock network allows a signal to reach one quadrant of the chip (though half of the chip can be reached by driving two quadrants). The external clock-out path represents the clock path from the outputs of the phase-locked loop (PLL) to the dedicated PLL_OUT pins. The ALTCLKCTRL megafunction also provides glitch-free implementation for multiple clock input signals.

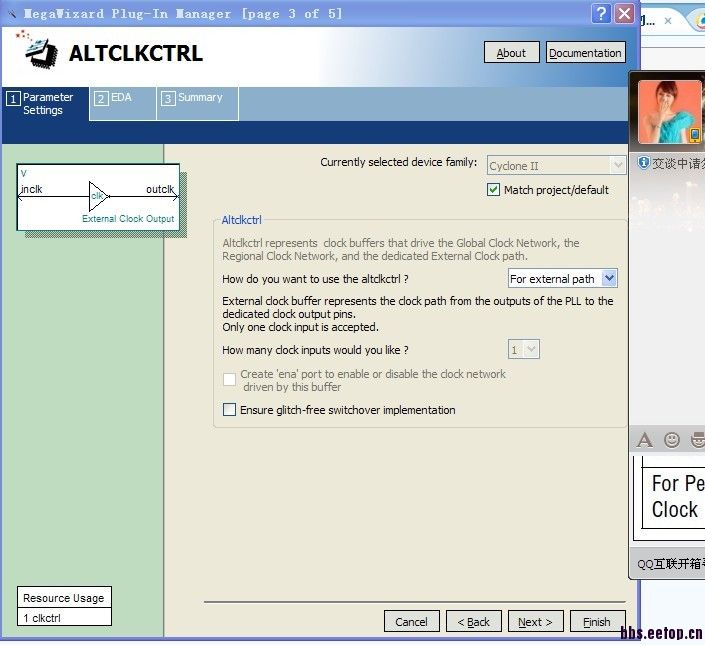

好像:cyclone II 只支持(1)global clock network ,(2) Dedicated External Clock Out Path , 但是选择(2)又无法支持时钟的mux,如下图:

完全无语呀,限制真心多

纠正:其实(3)也会报rom_addr相对clk的hold violation的WARNING(原因是之类代码有点问题)

欢迎大家多多讨论,不知道大家一般在fpga中怎么做clk的mux呢。。。

来源:http://bbs.elecfans.com/jishu_219906_1_1.html

为什么FPGA时钟频率不高,却适合做高速处理?Filed Programmable Gate Array 现场可编辑逻辑阵列

我在我的同学面前炫耀FPGA是做高速处理的,可是,当人家问我,我的时钟频率能达到多少时,我说利用PLL能拉到200MHz,他说,这么低啊?我的手机频率都是1.5G的呢。

我无语。。。

后来才了解到,他的1.5G要想完成一个运算的话,因为是串行处理,所以要n个时钟周期啊,而FPGA虽然起点(时钟频率慢),可是通过并行,处理数据的能力极大提高。

FPGA要实现高速的并行处理数据,那也得看处理什么数据!如果相关性比较大的一堆数据,那你是无法实现很好的并行性的。因此,FPGA更适合处理图像、视频等相关性不大的数据。

全同步的数字电路设计,一般使用一个全局时钟,作为驱动所有时序逻辑的主时钟。但如果设计比较复杂,可能会引入多个主时钟,即多时钟域的设计。这时,FPGA系统时钟频率约束就默认对应于所有主时钟的频率约束。如果希望设定不同的时钟频率约束,就必须单独给每个主时钟设定约束。

模拟(Emulation)是试图模仿一个设备的内部设计;仿真(Simulation)是试图模仿一个设备的功能。

http://china.xilinx.com/training/vivado/index.htm Vivado的视频辅导资料

《企业用verilog_代码风格规范》来源:http://www.docin.com/p-602544098.html

Verilog HDL 华为入门教程

http://wenku.baidu.com/view/1de5f06527d3240c8447ef95.html

Verilog典型电路设计 华为

http://wenku.baidu.com/view/daf2690e52ea551810a687e9.html

华为fpga设计规范(Verilog Hdl)

http://wenku.baidu.com/view/2c07b8e9856a561252d36f25.html

Vivado HLS全称是High Level Synthesis高层次综合。从以器件为中心的开发上升到以IP和系统为中心的开发。‘All Programmable’器件。嵌入ARM Cortex-A9双核的Zynq7000器件。

VBO与LVDS互转的厂家有Himax和THine。

LVDS转VBO的芯片:Himax家HX6512-A, 00DFAG-B,351GNBGC

VBO转LVDS的芯片:THime家0845TN43, THCV215 ES4

来源:http://china.xilinx.com/training/vivado/vivado-design-methodology.htm

HDL 代码建议目标硬件、约束生成和验证最佳方法、使用物理约束的规划和分析工具,如时钟和引脚规划,以及最佳性能的布局规划。

1118

1118

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?