verilog简易实现CPU的Cache设计

该文是基于博主之前一篇博客http://www.cnblogs.com/wsine/p/4661147.html所增加的Cache,相同的内容就不重复写了,可点击链接查看之前的博客。

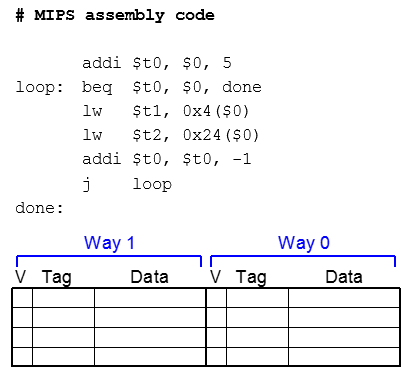

Cache结构

采用的是2-way,循环5遍的测试方式,和书本上一致,4个set

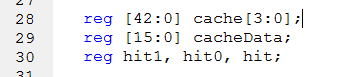

Cache设计

首先在PCPU模块里面增加寄存器

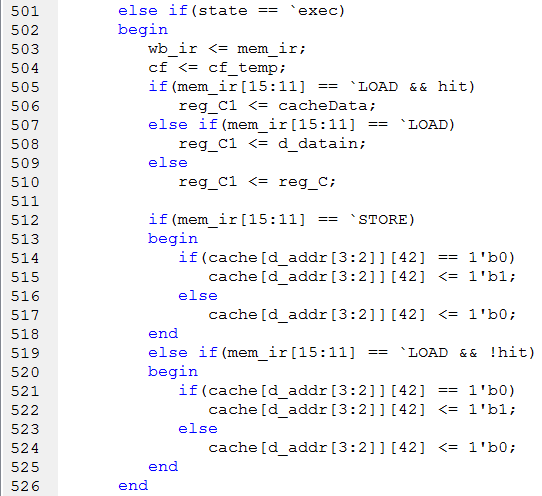

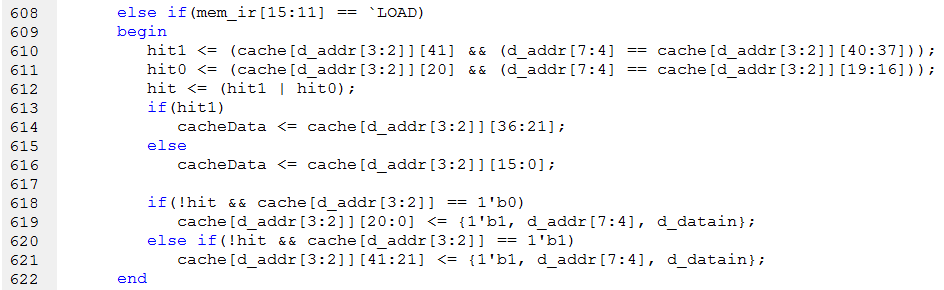

在流水线MEM那一阶段如果是STROE或者LOAD指令更新cache

采取的替换策略是FIFO策略,在cache上面增加了一个位U

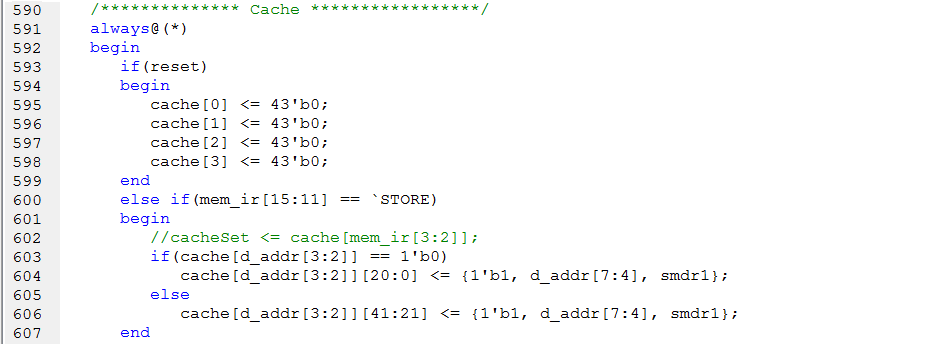

整个cache的控制部分如下:

如果读取时没有hit,则会成memory中取值并存到cache里面

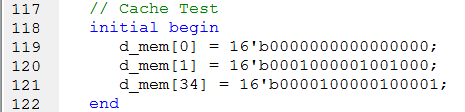

书本和ppt上的样例,初始化了datamemory的值

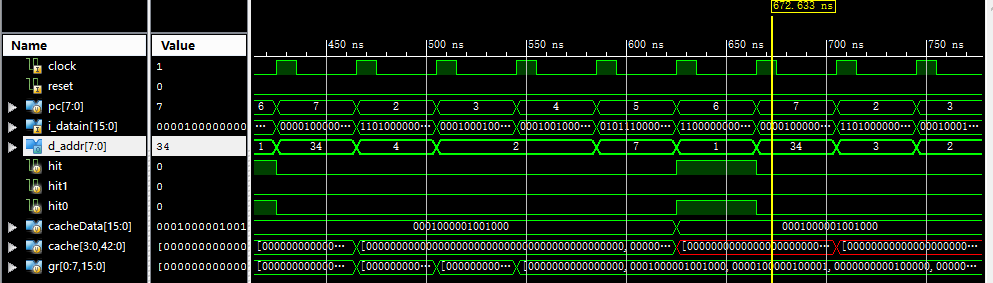

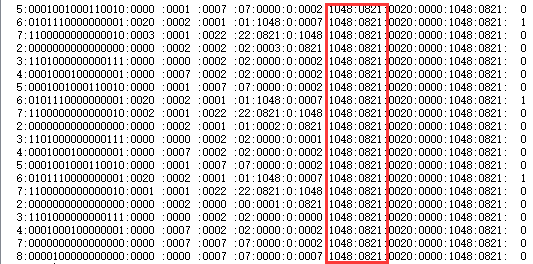

仿真结果

从仿真器可以比较容易观察数据的变化,特别是hit0和hit1的变化

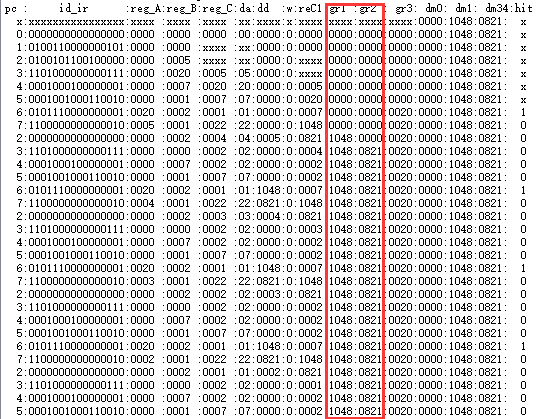

从仿真文本来看,gr1和gr2的load结果也是成功的。没有出现不能错误读取的xxxx结果

传送门:

- CPU2_Cache

点击这里

本文详细介绍了如何使用Verilog实现CPU的Cache设计,包括Cache结构、设计过程、控制部分以及仿真结果。通过增加寄存器和特定的替换策略,实现了在PCPU模块中对STROE或LOAD指令的高效处理。

本文详细介绍了如何使用Verilog实现CPU的Cache设计,包括Cache结构、设计过程、控制部分以及仿真结果。通过增加寄存器和特定的替换策略,实现了在PCPU模块中对STROE或LOAD指令的高效处理。

1492

1492

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?