I-Cache

I-Cache总的来讲比较简单,因为与内存的交互只有读入。

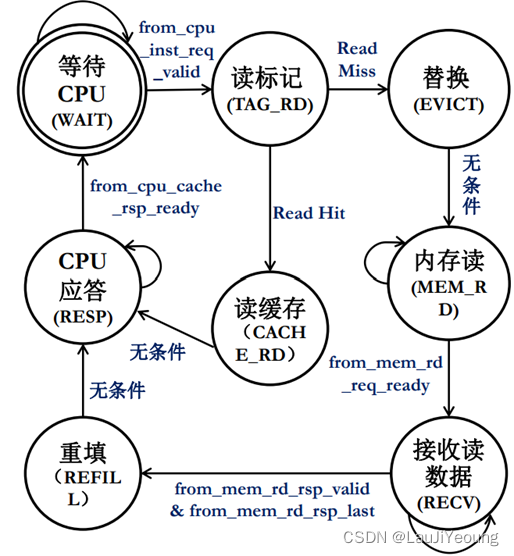

按照流程,写出自动机即可:

define WAIT 8'b00000001 define TAG_RD 8’b00000010

define EVICT 8'b00000100 define MEM_RD 8’b00001000

define RECV 8'b00010000 define REFILL 8’b00100000

define CACHE_RD 8'b01000000 define RESP 8’b10000000

always @ (posedge clk)begin

if(rst == 1’b1)begin

current_state<=`WAIT;

end

else begin

current_state<=next_state;

end

end

always @ (*)begin

case(current_state)

`WAIT :begin

if(from_cpu_inst_req_valid)

next_state = `TAG_RD;

else

next_state = `WAIT;

end

`TAG_RD :begin

if(Read_Hit)

next_state = `CACHE_RD;

else

next_state = `EVICT;

end

`EVICT :begin

next_state = `MEM_RD;

end

`MEM_RD :begin

if(from_mem_rd_req_ready)

next_state = `RECV;

else

next_state = `MEM_RD;

end

`RECV :begin

if(from_mem_rd_rsp_valid & from_mem_rd_rsp_last)

next_state = `REFILL;

else

next_state = `RECV;

end

`REFILL :begin

next_state = `RESP;

end

`CACHE_RD :begin

next_state = `RESP;

end

`RESP :begin

if(from_cpu_cache_rsp_ready)

next_state = `WAIT;

else

next_state = `RESP;

end

default: next_state = current_state;

endcase

end

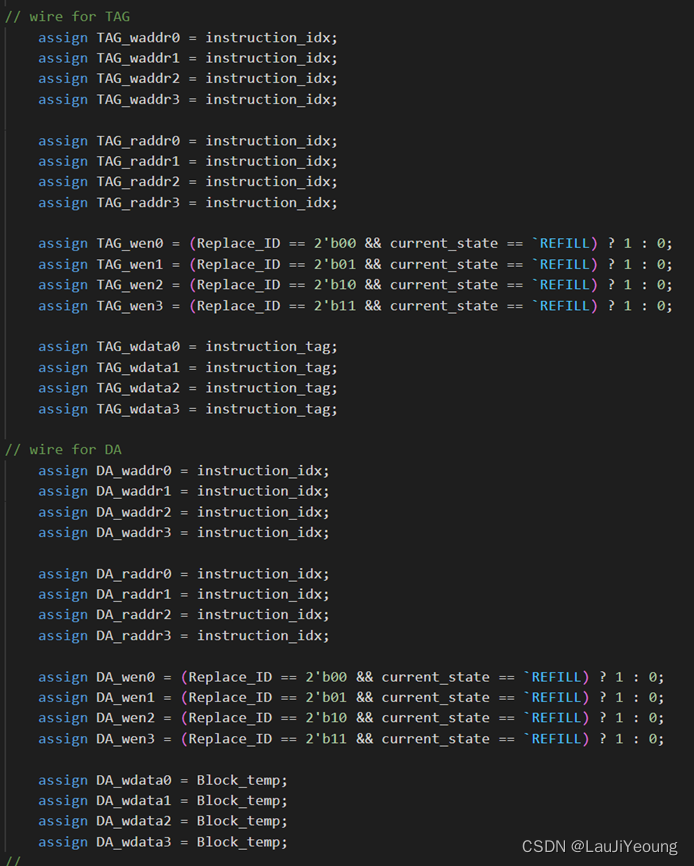

总的来讲,ICache没有什么难点,按照题意设计四个way的Tag和Data的专用寄存器堆,然后再判断当前的块是在哪个位置即可:

唯一值得注意的是写入地址的设计,即Replace_ID的设计,我的设计是循环写入,即先写way0,way1…way3最后又来写way0。

另外一个值得注意的点是burst操作:

always @ (posedge clk) begin

if(current_state == `MEM_RD && from_mem_rd_req_ready)

len <= 0;

else

if(current_state == `RECV && from_mem_rd_rsp_valid)

len <= len + 1;

end

always @ (posedge clk) begin

if(current_state == `RECV && from_mem_rd_rsp_valid) begin

case(len)

3'b000 : begin

Block_temp [ 31: 0]<= from_mem_rd_rsp_data;

end

3'b001 : begin

Block_temp [ 63: 32]<= from_mem_rd_rsp_data;

end

3'b010 : begin

Block_temp [ 95: 64]<= from_mem_rd_rsp_data;

end

3'b011 : begin

Block_temp [127: 96]<= from_mem_rd_rsp_data;

end

3'b100 : begin

Block_temp [159:128]<= from_mem_rd_rsp_data;

end

3'b101 : begin

Block_temp [191:160]<= from_mem_rd_rsp_data;

end

3'b110 : begin

Block_temp [223:192]<= from_mem_rd_rsp_data;

end

3'b111 : begin

Block_temp [255:224]<= from_mem_rd_rsp_data;

end

endcase

end

end

对于这一块,我是这么考虑的:我按照教案的解释设计了一个len的register用来统计当前的长度,然后利用当前的len来选数,写进读入的Block。

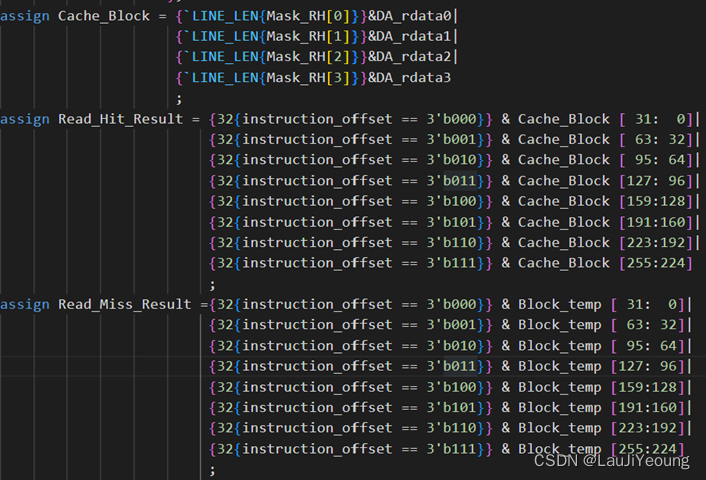

最后读出部分就比较简单了,如果是hit,就用寄存器读出的值,否则就用从内存得到的值即可:

这里是使用地址的低2-4位进行选数,因为这是按照byte存储的。

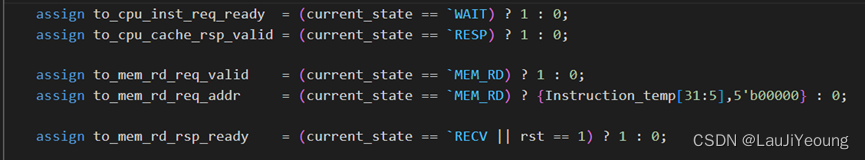

其余的一些小细节是:

再WAIT阶段要把两个WAIT信号拉高,传给内存的地址要是BLOCK的首位地址。

D-Cache

D-Cache总的来讲就比较复杂了,为此我设计了16种独热码:

`define D_WAIT 16'b0000000000000001

`define D_JUDGE 16'b0000000000000010

`define D_CACHE_RD 16'b0000000000000100

`define D_RESP 16'b0000000000001000

`define D_EVICT 16'b0000000000010000

`define D_MEM_WB 16'b0000000000100000

`define D_MEM_RD 16'b0000000001000000

`define D_RECV 16'b0000000010000000

`define D_REFIL 16'b0000000100000000

`define D_CACHE_WB 16'b0000001000000000

`define D_IO_RECV 16'b0000010000000000

`define D_IO_RESP 16'b0000100000000000

`define D_IO_WB 16'b0001000000000000

`define D_IO_RD 16'b0010000000000000

`define D_IO_REQ 16'b0100000000000000

`define D_MEM_REQ 16'b1000000000000000

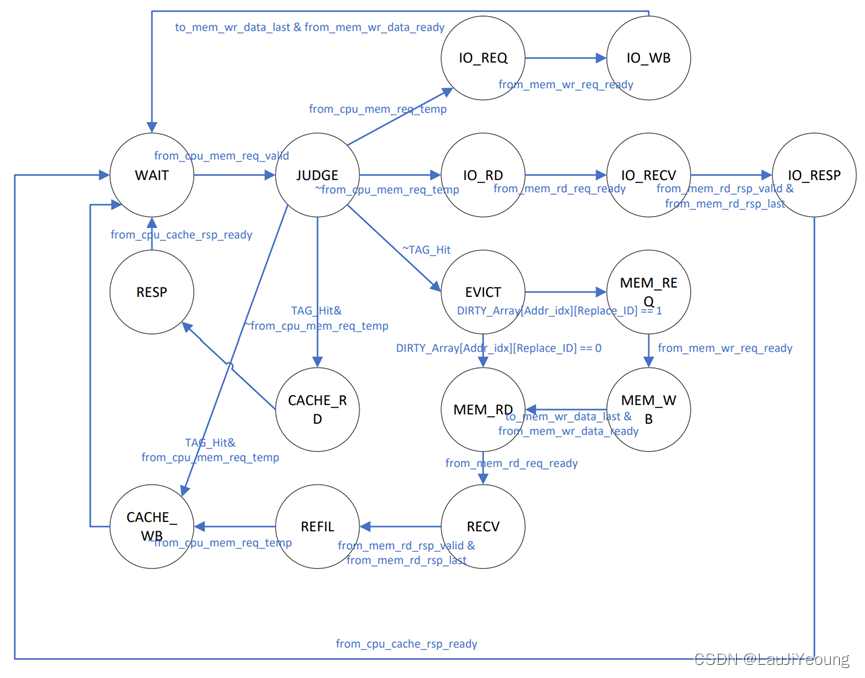

状态转移图如下:

总的来讲,这个状态转移设计的比较臃肿,对于旁路部分,将读和写分开来写,读的部分直接模仿ICache的状态转移图即可。对于写,按照要求,必须先传REQ再传数据,所以需要两个状态。

对于非旁路部分,则有四种情况,如果是命中的读,则和ICache一样,如果是命中的写,也比较简单,直接往内部写即可。对于未命中,由于采用Write

Allocate策略,所以全部进入替换策略。如果发现Cache内容已经被改写,则依旧是经过一个REQ和WB过程进行写回。

随后和ICache一摸一样的进行读入,到REFIL,如果是写操作则改写,否则还是和CPU握手后传回数据。

具体实现:

always @ (posedge clk)begin

if(rst == 1'b1)begin

current_state<=`D_WAIT;

end

else begin

current_state<=next_state;

end

end

always @ (*)begin

case(current_state)

`D_WAIT :begin

if(from_cpu_mem_req_valid)

next_state = `D_JUDGE;

else

next_state = `D_WAIT;

end

`D_JUDGE :begin

if(op_IO)begin

if(from_cpu_mem_req_temp)

next_state = `D_IO_REQ;

else

if(~from_cpu_mem_req_temp)

next_state = `D_IO_RD;

else

next_state = `D_JUDGE;

end

else begin

if(~from_cpu_mem_req_temp)begin

if(TAG_Hit)

next_state = `D_CACHE_RD;

else

next_state = `D_EVICT;

end

else begin

if(TAG_Hit)

next_state = `D_CACHE_WB;

else

next_state = `D_EVICT;

end

end

end

`D_CACHE_RD :begin

next_state = `D_RESP;

end

`D_RESP :begin

if(from_cpu_cache_rsp_ready)

next_state = `D_WAIT;

else

next_state = `D_RESP;

end

`D_EVICT :begin

if(DIRTY_Array[Addr_idx][Replace_ID] == 1)

next_state = `D_MEM_REQ;

else

if(DIRTY_Array[Addr_idx][Replace_ID] == 0)

next_state = `D_MEM_RD;

else

next_state = `D_EVICT;

end==

`D_MEM_REQ :begin

if(from_mem_wr_req_ready)

next_state = `D_MEM_WB;

else

next_state = `D_MEM_REQ;

end

`D_MEM_WB :begin

if(to_mem_wr_data_last & from_mem_wr_data_ready)

next_state = `D_MEM_RD;

else

next_state = `D_MEM_WB;

end

`D_MEM_RD :begin

if(from_mem_rd_req_ready)

next_state = `D_RECV;

else

next_state = `D_MEM_RD;

end

`D_RECV :begin

if(from_mem_rd_rsp_valid & from_mem_rd_rsp_last)

next_state = `D_REFIL;

else

next_state = `D_RECV;

end

`D_REFIL :begin

if(~from_cpu_mem_req_temp)

next_state = `D_RESP;

else

next_state = `D_CACHE_WB;

end

`D_CACHE_WB :begin

next_state = `D_WAIT;

end

`D_IO_RD :begin

if(from_mem_rd_req_ready)

next_state = `D_IO_RECV;

else

next_state = `D_IO_RD;

end

`D_IO_RECV :begin

if(from_mem_rd_rsp_valid & from_mem_rd_rsp_last)

next_state = `D_IO_RESP;

else

next_state = `D_IO_RECV;

end

`D_IO_REQ :begin

if(from_mem_wr_req_ready)

next_state = `D_IO_WB;

else

next_state = `D_IO_REQ;

end

`D_IO_WB :begin

if(to_mem_wr_data_last & from_mem_wr_data_ready)

next_state = `D_WAIT;

else

next_state = `D_IO_WB;

end

`D_IO_RESP :begin

if(from_cpu_cache_rsp_ready)

next_state = `D_WAIT;

else

next_state = `D_IO_RESP;

end

default: next_state = current_state;

endcase

end

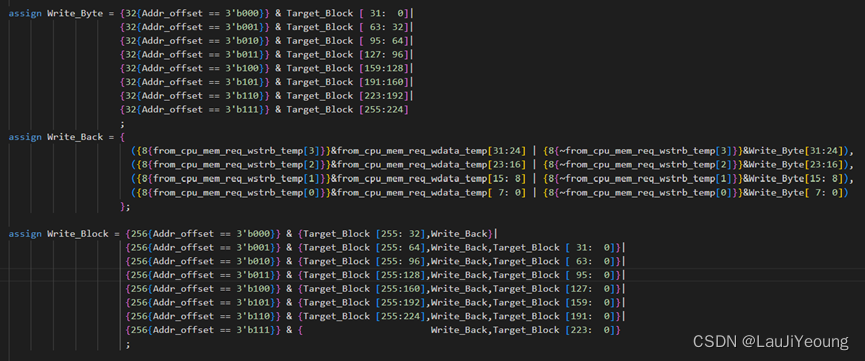

其余大部分内容都是一样的,唯一比较特别的是替换操作,我的实现比较繁琐,具体思路是从Cache中取出所需要的Block,然后再取出所需要的Byte,接着再得到修改后的Byte,最后又拼回所需要的Block。

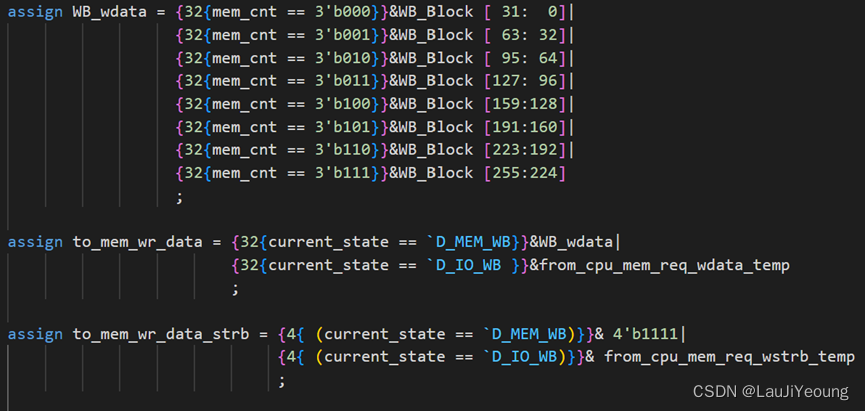

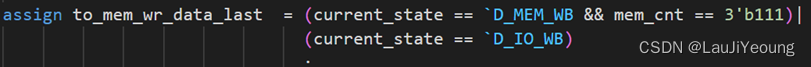

另外一个比较特殊的地方是Burst写的时候的信号问题,这实际上也不是很难:

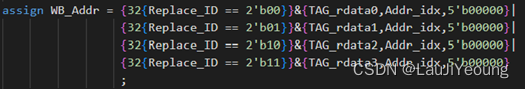

第一是一定要用Tag专用寄存器拼接出对应的地址,而不是误用读入的地址:

其次是在读出数据的时候对8个Byte的位置需要进行选数:

对于握手信号,注意在最后一拍拉高:

1452

1452

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?